Устройство динамического приоритета

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

{u)i995092 (61)Дополнительное к авт. свид-ву (22) Заявлено 14.0881 (21) 3327620/18-24

f$q} gN 3 с присоединением заявки ¹â€”

6 З6 Ф 9/46

Государственный комнтет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 07.02.83. Бюллетень ¹

Дата опубликования описания 07-0283 (ЩУДК 681.325 (088.8) Э.П. Чернаков, Б.С. Богумирский и В.М. Шщанков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДИНАМИЧЕСКОГО ПРИОРИТЕТА

Изобретение относится к вычислительной технике и может быть исполь« зовано в вычислительных системах.

Известно устройство приоритета, содержащее флажковый регистр, группу элементов И, регистр обслуживания, элемент задержки, блок аварийного останова и сдвиговый регистр (1).

Его недостаток — невозможность из. менения приоритетов заявок.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство переменного приоритета, содержащее флажковый регистр, первую группу элементов И, регистр обслуживания, первый . . элемент ИЛИ, первый элемент задержки, блок аварийного останова, сдвиговый регистр, буфер масок, генератор импульсов и элемент И (2).

Это устройство имеет следующие недостатки: низкую надежность, так как в случае появления одновременно нескольких заявок на выходе регистра обслуживания за счет сбоев при включении питания и т.д. зти заявки проходят на выход устройства. Одновременно с появ- лением заявок на выходе устройства эти заявки поступают в блок аварийного останова, где в результате этого будет выбран сигнал, сбрасывающий регистр обслуживания в исходное состояние, однако это произойдет уже после появления ошибочно выработанных сигналов на выходе устройства;, некорректность по отношению к sassке с"высшим приоритетом во время обслуживания заявки с низшим приоритетом, т.е. если во время обслуживания какой-либо заявки поступит. заявка с более высоким приоритетом, то она не будет обслуживаться до тех пор, пока не будет завершено обслуживание этой заявки.

Цель изобретения — повышение надежности.

Поставленная цель достигается тем, что в устройство, содержащее регистр заявок, первый блок элементов И, блок памяти масок, первый элемент ИЛЙ, первый элемент задержки, блок, аварийного останова, сдвиговый регистр, пер вый буферный регистр, генератор им25 пульсов и элемент И, причем единичные входы регистра заявок соединены с группой входов заявок устройства, уп равлякщий вход регистра заявок подключен к входу конца обслуживания

30 устройства, группы выходов регистра

995092 заявок соединены с первой группой входов первого блока элементов И и с входами первого элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу генератора импульсов, вы- ход элемента И соединен с управляющим (входом сдвигового регистра, выход ко торого соединен с адресным входом блока памяти масок, информационные входы которого подключены к группе входов масок устройства, выходы блока памяти масок соединены с в торой группой входов первого блока элементов И, выходы первого буферного регистра соединены с входами блока аварийного останова и с входами сброса регистра заявок, введены второй буферный регистр, схема сравнения, второй элемент задержки, три блока элементов И и три элемента ИЛИ, причем выходы первого блока элементов И соединены с группой входов второго блока элементов И, управляющий вход которого подключен к выходу первого элемента задержки, группа выходов второго блока элементов И соединена с входами второго буферного регистра, установочный вход которого подключен к выходу второго элемента ИЛИ, входы третьего элемента ИЛИ соединены с группой выходов первого блока элементов 30

И, выход. третьего элемента ИЛИ соединен с первым входом второго элемента ИЛИ, с входами первого элемента задержки, с управляющим входом третьего блока элементов И и через второй 35 элемент задержки — с первым входом четвертого элемента ИЛИ, выход которого подключен к первому входу сдвигового регистра, установочный вход второго буферного регистра и вторые вхо- ) ды второго и четвертого элементов ИЛИ соединены с входом конца обслуживания устройства, первый выход блока аварийного останова соединен с третьими входами второго и четвертого элементов ИЛИ, выход второго буферного регистра подключен к первому входу схемы сравнения, второй вход которой соединен с выходами сдвигового регист- ра, а выход схемы сравнения соединен с четвертым входом четвертого элемента ИЛИ, выход сдвигового регистра, соединен с входом третьего блока элементов И, выход которого соединен с входом второго буферного регистра, второй выход блока аварийного останова соединен с управляющим входом четвертого блока элементов И, группа входов и выходов которого соединены соответственно с группой выходов пер.вого буферного регистра и с группой 60 информационных выходов устройства.

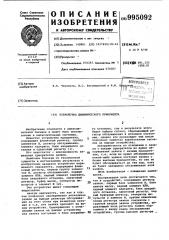

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — структурная схема блока аварийного останова. 65

Устройство (фиг. 1) содержит регистр 1 заявок, блок 2 элементов И, буферный регистр 3, элемент HJiH 4, элемент 5 задержки, блок 6 аварийного останова, регистр 7 сдвига, блок

8 памяти масок, генератор 9 импульсов, элемент И 10, буферный регистр

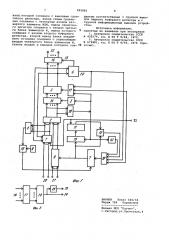

11, схему 12 сравнения, элемент 13 задержки, блоки 14-16,элементов И, элементы. ИЛИ 17-19, группу входов 20 заявок устройства, группу входов 21 масок устройства, вход 22 конца обс- луживания устройства, группу информа,ционных выходов 23 устройства, группу входов 24 блока аварийного останова, выходы 25 и 26 блока аварийного останова. Блок аварийного останова (фиг.

2) содержит дешифратор 27, элемент

ИЛИ 28, элемент НЕ 29.

Устройство работает следующим образом.

В исходном состоянии регистры 1, 3 и 11 обнулены, регистр 7 установлен в исходное состояние (в первый разряд занесена единица, а остальные разряды обнулены), а в блок 8 занесен массив масок приоритета.

При поступлении сигналов заявок через входы..20 устройства на входы регистра 1 на выходе элемента ИЛИ 4 появляется единичный потенциал, открывающий элемент И 10. Импульсы с выхода генератора 9 импульсов проходят на управляющий вход сдвигювого регистра 7, Под действием этих сигналов единица, первоначально записанная в первый разряд регистра 7, продвигается в последующие разряды. Вследствие этого с выходов управляемого этим регистром по адресным входам блока 8 на вторые входы блока 2 начинают поступать маски в порядке убывания приоритета. Когда единица появится в разряде маски, соответствующем заявке со старшим текущим приоритетом, на соответствующем выходе блока 2 возникает единичный сигнал, который проходит через элемент ИЛИ 18, затем — через элемент ИЛИ 17, обнуляя регистр

3, и с задержкой, необходимой для обнуления, проходит на управляющий вход блока 14. При этом единичный сигнал с одного из выходов блока 2 записывается в регистр 3. Если на выходах регистра 3 присутствует только одна единица, то сигналом с выхода элемента НЕ 29 открывается блок 16 элементов И и с выхода соответству.мцего разряда регистра 3 единичный сигнал поступает на соответствующий выход группы выходов 23.

Сигнал с выхода элемента ИЛИ 18 также подается на управляющий вход блока 15 (при этом код из сдвигового регистра 7 переписывается со сдвигом на один разряд в сторону первого разряда в регистр 11) и с, задержкой проходит через элемент ИЛИ 19 на входы

995092 сдвигового регистра 7, устанавливая Формула изобретения

его в исходное -состояние. При этом

Устройство динамического приоритев первый разряд сдвигового регистра содержащее регистр заявок, перльта, содерж вый блок элементов И б ок па я . первый элеме т ИЛИ первый элемент задержки, блок аварийнбго остана управляющий вход сдвигового регистра 7, то осуществляе.ся сдвиг этой единицы в последующие разряды до тех

ПОРР пока содерж""Ое сдвигового Реги- " ра заявок соединены с группой стра 7 не совпадет с содержимым ре- 30

rmcTpa 11. IIpH aToM cxeMa 12 cpaaHe + < a д к

° ния выдает единичный сигнал, который, вх конца обслуживания устройства, пройдя через элемент ИЛИ 19, устанав- группа выходов регистра заявок соеди" ливает РегистР 7 в исходное состоЯ" A rpynhoA Входой первого ние3 затем Осуществляется сдвиг до 15 блока элементов И и с входами. первосовпадениЯ и т.д. ПРи этом из блока о элемента ИЛИ, в од которого сое. 6 выбиРаютсЯ только. маски, соответ- - ен с пе в входом элемента И, втоствующие более высокому по отношению к обслуживаемой заявке приоритету. ,пу генератора импульсов, выход элеменПри поступлении на регистр 1 более 2О И соед нен с управля входом пРиоРитетной заЯвки, чем обслУживае- сдвигового регистра, ВыхОд которого мая, в случае, рассмотренном ранее, соединен с адресным входом блока памяу pynne лемен ов И появл ется единичный сигУстройства, выходы блока naawwayy маствующий разряд регистр егист а 3 после его сок соединены с второй группой вхообнуления. Далее работа устройства дов первого блока элементов И, выхопроисходит описанньм ьм выше способом. ды первого буферного регистра соедивходами e o a аварий осТа22 ст ой30 нова и с входами сброса регистра эапроисходит селективный сброс - обслуявок, отличающеес я тем, ReHHoA заЯВки в РегистР, У что, с целью пов „ения надежности е 1 обн ле.ние

РегистРа 3 и Устано к устройства в. работе путем исключения стоЯние РегистРа 7 ° ПРи отсутствии сбойн ситуаций, в него введены втоЗ5 рой буферный регистр, схема сравнения, второй элемент задержки, три блока элементов И и три элемента ИЛИ, 1 О; В п от ив ном причем выходы первого блока элемейзаявок . . тов И соединены с группой входов вто4щ рого блока элементов И, управляющий г по какой-либо причине (а рим р,. Ж ) регистр

Ято более одной заявки, пОдов второго блока элементов И соедидешифратора 27. Этот-сигнал. проходит через элемент ИЛИ 28 на выход 26, в

Результате чего устройство переводит 45 ятых заявок.

ИЛИ входы третьего элемента ИЛИ соеРОМе того снимается сигнаЛ управ ляющего входа группы 16 элементов И, чем запрещается прохождение заявок на

50 второго. элемента ИЛИ с входами первоом блок 1б должен обеспечивать задержку по своим информационным входам, д остаточную входом третьего блока элементов И и. для прохождения сигнала через че ез блок б че еэ второй элемент задержки — с

aaapHAHoro ocTaHosa на е у"Ра ИЛИ е и авляащий чере вход. обсл жива 55 выход которого подключен к первому

ВХОцу сдвигОВОго регистра устанОВОч ния двух и более заявок срабатывает и вторые входы второго и четвертого элементов ИЛИ соединены с входом конКР ает блок 16, не ДОПУСТИВ по"Вле- 60 ца Обслуживания устройства, первый выход блока аварийного останова соединен с третьими входами второго и четве того элементов ИЛИ выход тов режим просмотра принятых заявок. рого буферного регистра подключен к

ПРименение изобРетени " " "" 65 первому входу схемы сравнения, вто,й повысить надежность устройства.

995092 вход которой соединен с выходами сдвигового регистра, выход схемы сравнения соединен с четвертым входом четвертого элемента ИЛИ, выход сдвигового регистра соединен с входом третьего блока элементов И, выход которого соединен с входом второго буферного регистра, второй выход блока аварийного останова соединен с управлякщим входом четвертого блока элементов И, группа входов и выходов которого сое- >О динены соответственно с группой выходов первого буферного регистра и с группой информационных выходов устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 450174, кл. G 06 F 9/46, 1972, 2. Авторское свидетельство СССР

Ф 679981, кл. G 06 F 9/46, 1976 (прототип) .

ВНИИПИ Заказ 646/34

Тираж 704 Подписное

Филиал ППП "Патент", г.Ужгород,ул.Проектная,4