Устройство для быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

{ii>995096

-(61)Дополнительное к авт.„свид-ву— (22) Заявлено 17 ° 08. 81 (2! ) 3332944/18-24 с присоединением заявки Йо .— (23) Приоритет— (И) М. Кд.з

G Об F 15/332

Государственный комитет

СССР по делам изобретений и открытий

)$3) УДК 681. 3 (088. 8) Опубликовано 07.0283. Бюллетень Nо g

Дата опубликования описания.07 ° 02 83. (72) Автор изобретения

Г.М.Зайцев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ

ФУРЬЕ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах вычисления спектра по алгоритму быстрого преобразования Фурье (БПФ), например, в специализированных арифметических устройствах спектрального анализа для операций с комплексными числами.

Известно устройство для выполненния быстрого преобразования Фурье, в котором все вычислительные операции над действительными числами выполняются параллельно,чем обеспечивается достаточно высокое быстродействие

С1 3.

Недостатки этого устройства— большое количество оборудования и неоптимальное его использование при выполнении базовой операции БПФ. .Наиболее близким техническим решением к предлагаемому является устройство для быстрого преобразования

Фурье, содержащее девять регистров, умножитель, сумматор, два коммутатора и блок микропрограммного управления С2).

Однако в данном устройстве одна базовая операция БПФ выполняется эа шесть тактов умножения, что приводит к недостаточно высокому быстродействию.

Цель изобретения -- повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройстве для быстрого преобразования Фурье, содержащем шесть входных регистров, умножитель, сумматор, регистр произведений, два регистра сумм два Коммутатора и блок микропрограммного управления, причем выходы первого и второго входных регистров через первый коммутатор подключены к входам умножителя, выход которого подклюЧен к.входу регистра произведений, выходы третьего и четвертого входных регистров и выход регистра произведений через второй коммутатор подключены к входам сумматора, выход которого является выходом устройства и подключен к входам регистров сумм, выходы блока микропрограммного управления подключены к управляющим входам коммутаторов, выходы

25 пятого и шестого входных регистров подключены к дополнительным информационным входам первого коммутатора, а выходы регистров c — к дополнительным информационньхк-входам второ- .

ЗО го коммутатора.

995096

ReB,,„= 2ReA,— ReA,- „;

Формула изобретения

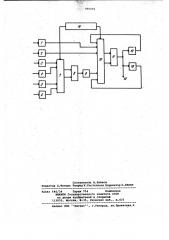

На чертеже представлена функциональная схема устройства для быстрого преобразования Фурье.

Устройство содержит входные регистры 1 — 6, коммутатор 7, умножитель 8, регистр 9 произведений, коммутатор 10, сумматор 11, регистры

12 и 13 сумм и блок 14 микропрограммного управления.

Блок 14 может состоять из генератора тактовых импульсов, счетчика тактовых импульсов и блока памяти микрокоманд, адресный вход которого подключен к выходу счетчика, а выход является выходом блока микропрограммного управления.

Устройство выполняет за каждую базовую операцию следующие операции:

КеЯ,,„=ReA.,+ВВ,.КеС,.— Э в„.з с,.;

А,+aee," C,.+ В„.ReC,; где A. — первое комплексное число; 25

B ° — второе комплексное число;

С; — комплексная весовая функция.

На выходные регистры 1-4 записываются исходные числовые данные ВеА», ;Т,А;, РеВ :,й щ В, ReC< и 0„, C» . ЗО

Коммутатор 7 сомножителей направляет на умножитель 8 входные данные для получения промежуточных произведений (соответственно по четырем тактам текущей базовой операции, которые 35 последовательно записывают в регистр 9 произведения: в конце первого тактапроиэведение ReB .ReC в конце второго — 3 8, ° Д С;;,в конце третьего - ReB. - J C„H oH e eTee Te o 40 .D B - ReC-. B первой половине второго такта на сумматор 11 через коммутатор 10 поступают ReA из входного регистДа 1 и первое произведение.

Эта частная сумма записывается в конце первой половины второго такта в регистр 12. В течение первой половины третьего такта коммутатор 10 подает на сумматор 11 новое произведение из регистра 9 и частную сумму иэ регистра 12 в результате сложения этих слагаемых, в сумматоре ll в конце первой половины третьего такта на выход 15 выдается и одновременно записывается в регистр 13 первый результат ReA:,+„ . В течение половины третьего такта коммутатор 10 подает слагаемые из регистра 13 и входного регистра 1 для получения на сумматоре 11 второцо числа ReB „..

Иа протяжении первой половины чет-Щ вертого такта на сумматор 11 через коммутатор 10 подается третье лроизВедение из регистра 9 и число иэ входного регистра 2, частная, сумма записывается в регистр 12. В течение Ц первой половины первого такта следую,щей базовой операции на выходе сумматора 11 после поступления на него через коммутатор 10 четвертого произведения из регистра 9 образуется следующее число юА „+„,которое записывается в регистр 13 и выдается на выход 15. Во второй половине первого такта следующей базовой операции получается последнее четвертое число путем сложения числа из входного регистра 2 и регистра 13, поступающих на сумматор 11 через коммутатор 10.

Таким образом, в течение всех четырех тактов текущей базовой операции вычисляются четыре сомножителя, а частичные суммы и конечные результаты на выходе сумматора образуются e течение первой половины второго и нетвертого тактов, а также в полутактах третьего такта текущей и первого такта последующей базовой операций.

Таким образом, в предлагаемом устройстве цикл работы состоит иэ четырех тактов или восьми полутактов. Причем, в шести полутактах сумматор и блок умножения работают одновременно.

Использование предлагаемого устройства позволяет получить выигрыш по быстродействию в сравнении с прототипом на ЗЗЪ.

Устройство для быстрого преобразования Фурье, содержащее шесть входных регистров, умножитель, сумматор, регистр произведений, два регистра сумм, два коммутатора и блок микропрограммного управления, причем выходы первого и второго входных регистров через первый коммутатор подключены к входам умножителя, выход которого подключен к входу регистра произведений, выходы третьего и четвертого входных регистров и выход регистра произведений через второй коммутатор подключены к входам сумматора, выход которого является выходом

:,устройства и подключен к входам ре-. гистров сумм, выходы блока микропрограммного управления подключены к управляющим входам коммутаторов, о т— л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, выходы пятого и шестого входных регистров подключены к дополнительным информационным входам первого коммутатора, а выходы регистров сумм — к дополнительным информационным входам второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Патент США 9 3800130, кл. 235-156, опублик. 1974, 2. Авторское свидетельство СССР

9 736113, кл. G 06 F 15/332, 1977 (прототип), 995096

Составитель В. Байков

Редактор A.Ìñòûëü Техред Ж;Кастелевич Корректор О.Билак

Заказ 646/34 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений-и открытий

113035, Москва, -Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4