Аналоговый умножитель

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистическик

Республик ()995099

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 21. 08. 81 (21) 3331349/18-24 (51) М. Кл.> с присоединением заявки ¹

С 06 О 7/16

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет

Опубликовано 07,0233, Бюллетень 9 5

Р ) УДК 681 ° 335 (088. 8) Дата опубликования описания 07..02.83

Д .Ъ. (72) Авторы изобретения

В. Н. Лапенко, И.К. Герасин и В. А. Соловьев

Московский институт электронной техники . (71) Заявитель (54) АНАЛОГОВЫЙ УМНОЖИТЕЛЬ

Изобретение относится к электрическим .вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Известен аналоговый умножитель, который содержит дифференциальный усилитель и операционные усилите-:. ли j1 3.

Недостаток этого умножителя— малая точность в широком динамическом диапазоне входных сигналов.

Наиболее близким к предлагаемому является аналоговый. Умножитель, содержащий -усилитель, логарифмирукщие и антилогарифмирующие диоды, сумматор (2 ).

Недостатком известного аналогового умножителя является малая точность перемножения, вызванная влиянием некомпенсироаанных температурных потенциалов логарифмирующих ди« одов.

Цель изобретения — повышение точности перемножения.

Укаэанная цель достигается тем, что в аналоговый умножитель, содержащий первый, второй и третий усилители, первый и второй логарифми рукицие диоды, антилогарифмирующий дйод, сумматор, первые электроды первого и второго логарифмнрукнцих диодов соединены с входами первого и второго усилителей соответственно, выходы которых подключены к входам сумчатора, выход последнего через антилогарифмирующий диод соединен с входом третьего усилителя, выход которого является выходом аналогового умножителя, введены первый, вто- рой и третий модуляторы, первый и второй аттенюаторы, первый и второй интеграторы, первый и второй фазочувствительные выпрямители, дополнительный усилитель, генератор опорного напряжения и блок вычитания,. причем входы первого и второго моду ляторов являются соответственно первым и вторым входами аналогового умножителя, выходы первого и второго модуляторов подключены к входам первого и второго усилителей соответственно, выход первого усилителя через первый аттенюатор соединен с вторым электродом первого логарифмнрующего диода, выход второго усилителя через второй аттенюатор соединен с вторым электродом второго логарифмирующего диода, выход третьего усилителя через последовательно соединенные дополнительный усилитель, первый фазочувст995099 вительный выпрямитель и первый интег- ратор подключен к управляющему входу первого аттенюатора, выходы первого и второго усилителей соединены с входами блока вычитания, выход которого через последовательно соединенные второй фазочунствительный выпрямитель н второй интегратор подключен к управляющему входу второго аттенюатора, выход третьего усилителя соединен с входом третьего модулятора, © выход которого подключен к входу третьего усилителя, выход генератора опорного напряжения соединен с управляющими входами первого, второго и третьего модуляторов и первого и второго фазочувствительных выпрями- . телей.

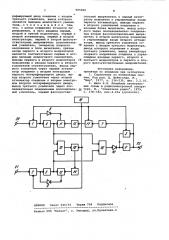

На чертеже представлена функциональная схема аналоговго умножителя,.

Устройство включает первый, второй и третий модуляторы 1 — 3, первый, второй и третий усилителя 4 — б, дополнительный усилитель 7, первый и второй логарифмирующие диоды 8 и 9, антилогарифмирующий диод.10, riepвый и второй аттенюаторы 11 и 12, 25 первый и второй интеграторы 13 и 14, блок 15 вычитания, сумматор 16, первый и второй .фазочунстнительные выпрямители 17 и 18, генератор 19 опорного напряжения, первый и вто- 39 рой входы 20 и 21 и выход 22 аналогового умножителя.

Аналоговый умножитель работает следующим образом.

На входы первого и второго моду- 35 ляторов 1 и 2 подаются перемножаемые напряжения. На управляющие входы этих модуляторов от генератора 19 опорного напряжения подается напряженив в виде меандра. Это напряжение щ() изменяет крутизну преобразонания первого и второго модуляторов 1 и.2, так, что она-принимает дна значения.

В результате, на выходах первого и второго модуляторов 1 и 2 формируются пульсирующие токи с частотой опорного напряжения, пропорциональные величинам соответствующих перемножаеьых напряжений и крутизнам модуляторов. На выходах первого и второго усилителей 4 и 5 формируются напряжения, принимающие дна значения в такт с опорным напряжением

КТ1 и„911

0 = — — Cn о

KT us

u — — Ь "2;(w)

КТ2

0 = — — 2п i (>)

21 2 % О

КТ а5

0 = — — tn i (4)

22 к, q, зо где П,U — напряжения на первом и втором входах 20 и 21; напряжения на выходе первого усилителя 4 соответственно н первый и второй такты (полупе- . риоды) опорного напряжения, П21,П вЂ” напряжения на выходе второго усилителя 5 воответетненно в первый и второй такты (полупериоды ) опорного напряжения;

К вЂ” постоянная Больцмана; заряд электрона

Т, Т вЂ” температуры переходон первого и второго логарифмирующих диодов 8 и 9. соответственно;

3 - ток насыщения диода;

К1, К -. коэффициенты передачи первого и второго аттенюаторон 11 и 12 соответственно;

S„, S — значения крутизны преобразования перного и второго модуляторов 1 и 2 соответственно в первом и втором тактах опорного напряжения.

Эти напряжения подаются на блок

15 вычитания на выходе которого формируется напряжение, пропорциональное логарифму отношения напряжений на первом и втором входах 20 и

21, которое имеет приращение в виде . переменной составляющей с частотой опорного напряжения. Эта переменная составляющая выделяется вторым фазочувствительным выпрямителем 18 и через второй интегратор 14 изменяет коэффициент передачи второго аттвню атора 12 так, что переменная составляющая на выходе блока 15 вычитания уменьшается. Процесс регулирования происходит до твх пор, пока переменная составляющая на выходе блока 15 вычитания не примет нулевое значение.

В установившемся режиме переменная составляющая на выходе первого усилителя 4, определяемая разностью между выражениями (1) и (2), КТ1 91

0 -U = — — 0 (<)

11 12 к„q 3 и переменная состанляющая на выходе второго усилителя 5, определяемая разностью между выражениями (3) и (4), 1 Кт2 51

0 -0 = — — 2n (6)

22 К е,. s должны быть равны. Приравняв (5 ) и (б ), получим

Т

K2=K1 т ( г

1 - 995099

Это является условием, прн котором переменная составляющая на выходе блока 15 Вычитания равна нулю. подставив (7 ) в (3 ) и (4 ), получим

2 1, Π= 1 — 1 Cn ) (8)

К, Ч о

5 —" 2n — (9)

22 K q, е

Отскда следует, что величина на.пряжения на выходе второго усилителя

5 пропорциональна температуре nepsoro логарифмирующего .диода 8 и коэффициенту передачи первого ат- )5 тенюатора 11, т.е. -температурные потенциалы первого и второго логарифмирующих диодов 8 и 9 становятся . равными.

Одновременно на выходе сумматора

16 формируется напряжение, IIporioy.циональное логарифму произведения напряжений на первом и- втором входах 20 и 21, которое -н такт с опорным напряжением принимает два значения . 25

Кт1 и1О25„ ц =О 40 = — . е» . 2,(1а)

d1 11 21 К1 Е, . КТ1 010252

u =u о = — "Qn («I

36

Таким образом, - выходное напряжение сумматора 16 имеет приращение в ниде меандра

hU =0 -U = — — В» — ° (12) ., 35 а С1 а2 К„

Это напряжение вызывает пульсирующий ток через антилогарифмирующкй диод 10. Третий усилитель 6 и третий модулятор 3 совместно выполняют 40 функцию преобразователя ток - напряжение с переменной крутизной, определяемой частотой опорного напряжения. В результате, на выходе третьего усилится 3 Форруется. Напряжениеу ро- 4% порциональное произведению напряжений на первом и втором входах 20 и

21, имеющее переменную составляющую в виде меандра. Эта составляющая уси ливается дополнительным усилителем 50, 7 и выпрямляется-первым фаэочувствительным выпрямителем 17. Выходное напряжение первого интегратора 13 регулирует коэффициент передачи первого аттенюатора 11 так, что переменная 55 составляющая в выходном напряжении третьего усилителя 6 уменьшается..

Регулировка коэффициента передачи происходит до тех пор, пока пере- - 60 менная составляющая не станет равной нулю. С учетом того, что крутизна третьего модулятора 3 изменяется синфазно,с крутизной первого и второго модуляторов 1 и 2, входное напря- 65

/ жение антилогарифмирующего диода

10 принимает два значения

KT О S

3 t» еых з .

sx„= <(, гже и,„ — нанрнжение на находе третьего усилителя 6 .(на выходе 22 );

Т вЂ” температура перехода анти логарифмирующего диода 10;

8» S4- значение крутизны третьего модулятора 3 в соответствии с тактами опорного напряжения.

Переменная составлякщая на антилогарифмирующем диоде 10 равна (З 5 3 а() =u -u = — 8» —., - (1Й ех gx1 вх Q s4

В установившемся режиме величина переменной составляющей на выходе сумматора 16 должна быть равна переменной составляющей на антилогарифмиру-нлщем диоде 10. Тогда, выбрав (16)

$2= $4 (17) и приравняв (12) и(15), получим т1 — (1e ).

1= т, О учетом (18) выражения (10) и (11) можно записать следующим обра зом:

Кт 0102 S1

0 = — 0» ; (19)

01 % ЗД

О

К7 U 025 ()„= — 2» 1 2 и (о). с2 т. е. происходит выравниванйе температурных потенциалов.

Приравняв (13 ) и (19) кли (14 ) и (20 ), получим

П П 2.. (21)

Таким образом, в предлагаемом аналоговом умножителе различие:в температурах первого и второго логарифмирующих диодов 8 и 9 и антилогарифмирукщего диода 10 и их дрейф не влияют на выполнение операции перемножейия двух напряжений. Следовательно, предлагаемы аналоговый умножктель обладает более высокой точностью перемножения. формула изобретения

Аналоговый умножктель, содержащий первый, второй и третий усилители, первый и второй логарифьесрующке диоды, антилогарифмирующий диод, сумматор, .первые электроды первого и второго логарифмирующих диодов сое-динены с входамк первого к второго усилителей соответственно, выходы которых подключены к входам сумматора, ныход последнего через антилога.

995099, ВНИИПИ Заказ 646/34 Тираж 704 Подписное

Филиал ППП "Патент", r. Ужгород, ул.Проектная,4 .Рифмирующий диод соединен с входом третьего усилителя, выход которого является выходом аналогового умножи теля,.отличающийся тем, что, с целью повыаения точности перемножения, в него введены первый, второй и третий модуляторы, первый н второй аттенюаторы, первый и второй интеграторы, первый и второй фазочувствительные выпрямители, дополнительный усилитель, генератор опорного 10 напряжения и блок вычитания, причем входы первого и второго модуляторов являются соответственно первым и вторым входами аналогового умножителя, выходы первого и второго модуляторов 15 подключены к входам первого и второго усилителей соответственно, выход первого усилителя через первый аттенюатор соединен с вторым электродом первого логарифмирующего диода, выход второго усилителя через второй аттенюатор соединен с вторым электродом второго логарифмирующего диода, выход третьего усилителя через последовательно соединенные дополнитель- д5 ный усилитель, первый фазочувствительный выпрямитель и первый интег - ратор подключен к управляющему входу первого аттенюатора, выходы первого и второго усилителей соединены с входами блока вычитания, выход которого через последовательно соединенные второй фазочувствительный выпрямитель и второй интегратор подключен к управляющему входу второго аттенюатора, выход третьего усилителя соединен с входом третьего модулятора, выход которого подключен к входу третьего усилителя, выход генератора опорного напряжения соединен с управляющими входами первого, второго и третьего модуляторов и первого и второго фазочувствительных выпрямителей.

Источники информации, принятые во внимание при экспертизе .1. Справочник по нелинейным схемам. Под ред. Д. Шейнголда. N.

"Мир", 1977, с. 234-235, фиг. 3.2.10.

2. Шило В.Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. М., "Советское радио", 1979, с. 178-182, рнс.4.20а (прототип).