Многоканальный цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (1о995311

Союз Свввтскйх

Социалистических

Республик

К АВТОРСКОМУ- СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заяалено02 .04.83, (21) 3269665/18-21

f51) h4 gs з

Н 03 К 3.3/02 с присоединением заявки Ио

Государственный комитет

СССР но делам изобретений н открытий (23) Приоритет (531 У К 68 . 325 (088.8) Опубликовано 070283. Бюллетень 14о. 5

Дата опубликованмя описания 07.02. 83 уйбышевский политехнический. институт им. В. В. Куйбышева (71) Заявитель (54) -ИНОГОКАНАЛЬННЙ ЦИФРОАНАЛОГОВЫЯ ПРЕОБРАЗОВАТЕЛЬ

ИзобреТение относится к вычислительной технике, в частности к п реобразователям код — напряжение, иможет быть использовано в системах вывода информации из цифровых вычислительных машин..

Известен многоканальный цифроаналоговый преобразователь (ЦАП) > содержащий общий для всех каналов преобразователь код — напряжение, выход которого через схему сравнения Н ключи соединен с входами аналоговых запоминающих элементов, выполненных .на интеграторах «1).

Недостатком данного устройства является низкое быстродействие.

Известен также многоканальный цифроаналоговый преобразователь, со держащий блок цифровой памяти, блок управления, первые ключи, блоки аналоговой памяти и одноканальный пре« образователь код - напряжение, входы которого через. блок цифровой памяти

° соединены с шинами входного кода, а выходы через первые ключи подключены к входам .блоков аналоговой памяти,:вход блока управления соединен с шиной кода номера канала, выходы бло. ка управления подключены к управляющнм входам не.рвых ключей и блока цифровой памяти I;2j

Недостатком устройства являются большое время записи аналоговой информации в аналоговый запоминат0щий элемент на интеграторах и невозможность быстрой смены аналоговой информации в любом канале преОбразбва

10 теля как вследствие принципиально низкого быстродействия аналоговых запоминающих элементов на интеграто" рах, так и:вследствие того, что каналы обслуживаются преобразователем код - напряжение поочередно и,для записи новой информации необходимо ож дать момента, когда псщощдет очеред на обслуживание данного канаЛа. Из.менение очередности обслуживания каналов не решает проблему, так как возможна.ситуация, когда в некоторых каналах очередное восстановление информации (регенерация) будет пропущено несколько раз подряд, что может привести к выходу сигналов за

2 пределы достоверных значений вследствие естественного дрейфа выходного напряжения. интеграторов.

Цель изобретения - повыаение быстродействия устройства.

995311

ЗО

45

50 формула изобретения

60

Поставленная цель достигается тем, что в многоканальный цифроаналоговый п рео бра зов а тель, соде ржащий блок цифровой памяти, блок управления, первые ключи, блоки аналоговой памяти и одноканальный преобразователь код - напряжение, входы которого через .блок цифровой памяти соединены с шинами входного кода, а выходы через первые ключи подключены к входам блоков аналоговой памяти, вход блока управления соединен с шиной кода номера канала, выходы блока управления подключены к управляющим входам первых ключей и блока цифровой памяти, введены вторые ключи и второй однока-I5 нальный преобразователь код — напряжение (ПКН), входы которого соединены с шинами входного Кода и соответствующими входами блока цифровой памяти, выход второго одноканального преобразователя код — напряжение подключен через вторые ключи к соответствующим входам блоков аналоговой памяти и выходам первых ключей.

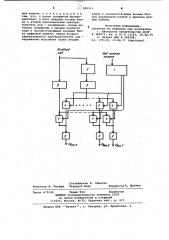

На чертеже приведена функциональная схема устройства.

Шина кода номера канала соединена с входом блока 1 управления, а шины входного кода через блок 2 цифровой памяти подключены к входу первого одноканального ПКН 3, выходы которого соединены через первые ключи 4 с входами блоков 5 аналоговой памяти ° Шины входного кода подключены также к входу второго ПКН б, .выход которого через вторые ключи 7 соединен с входами блоков 5 аналоговой памяти. Выходы блока 1 управления подключены к управляющим входам бло,ка 2 цифровой памяти, первых 4 и вторых 7 ключей. 40

Каждому каналу преобразования многоканального ЦАП в блоке 2 цифровой памяти отводится одна запоминающая ячейка, в которой хранится текущий код преобразования.

Устройство работает следующим образом.

Блок 1 управления поочередно считывает коды из ячеек блока 2 цифровой памяти на входы первого ПКН 3, одновременно открывая ключ 4 соответствующего канала. В этом режиме обеспечивается циклическая регенерация аналоговой информации в блоках 5 аналоговой памяти, причем период регенерации выбирается таким, чтобы гарантировать достоверность аналоговой информации на выходах блоков 5 аналоговой памяти. При поступлении нового кода для записи в канал, номер которого подается на отдельные входы блока 1 уйравления, последнее открывает аналоговый ключ 7 в соответствии с заданным номером канала, обеспечивая тем самым незамедлительную запись нового значения сигнала через второй ПКН б в соответствующий блок 5 аналого вой памя ти. Одновременно блок 1 управления записывает новый код преобразования в ячейку блока 2 цифровой памяти, выделенную для данного канала. Таким обра- . зом, процесс регенерации не замедляется, а новое значение кода сразу же преобразуется в аналоговый сигнал на выходе соотве тствующего канала.

В случае, когда запись нового зна чения сигнала и регенерация аналоговой информации должны производиться по одному и тому же каналу, процесс регенерации по данному каналу блокируется и блок 1 управления сразу же переходит к регенерации информации по следующему каналу. Запсь же нового значения сигнала через преобразователь б код — напряжение в данный канал проходит обычным образом.

Устройство позволяет с помощью двух ПКН организовать практически любое количество быстродействующих каналов цифроаналогового преобразования. Числс их зависит только от качества работы блоков аналоговой памяти, в частности от скорости спада. напряжения в этих элементах. Для существующих аналоговых запоминающих элементов типовым значением скорости спада является величина 10-100 мВ/с, что при точности 10 дв. разрядов, размахе выходного напряжения -10 В и времени, отводимом на одно цифроаналоговое преобразование, 10 мкс позволяет организовать соответственно

50000-5000 каналов цифроаналогового преобразования с погрешностью, вносимой схемой, показанной на чертеже, меньше 0,5 младшего значащего разряда и временем преобразования по любому каналу 10 мкс. При выполнении такого преобразователя по известной функциональной схеме потребовалось бы 5000-50000 дорогостоящих 10-разрядных преобразователей код — напряжение .

Многоканальный цифроаналоговый преобразователь, содержащий блок цифровой памяти, блок управления, первые ключи, блоки аналоговой памяти и одноканальный преобразователь код— напряжение, входы которого через блок цифровой памяти соединены с шинами входного кода, а выходы через первые ключи подключены к входам блоков аналоговой памяти, вход блока управления соединен с шиной кода номера канала, выходы блока управления подключены к управляющим входам первых ключей и блока цифро995311

Авиа ж

Составитель A. Сима,гин

Редактор В. Петраш Техред И. Надь Корректор А. Лзятко

Заказ б70/45 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент., г. Ужгород, ул. Проектная, 4 вой памяти, о т л и ч а ю.шийся тем, что, с целью повышения быстродействия, в него введены вторые ключи и второй одноканальный преобразователь код — напряжение, входы которого соединены с шинами входного кода и соответствующими входами блока цифровой памяти, выход второго одноканального преобразователя код— напряжение подключен через вторые ключи к соответствующим входам бло-. ков аналоговой памяти и выходам пер« эых ключей.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство .СССР

Р 340077, кл. H 03 К 13/03, 29.06.70

2. Патент C3QA 9 358308 кл. 179-15, 15.06;71 (прототип).