Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (n>995316 (61) Дополнительное к авт. свид-ву(22) Заявлеиоlб. 04 ° 81 (21) 3277499/18-21 рцМ gw з

Н 03 К 13/17 с присоединением заявки М— (73) Приоритет

Государственный комитет

СССР. но делам изобретений и открытий

Опубликовано 0702.83. Бюллетень Мо 5 ($3}УДК 681 ° 325 (088.8) Дата опубликования описания 07.02.83. 1

"В.И.Егоров, В.A.×åðåïàíoâ и N.Ã.Ðoõìà -

"i 3 ст р в

Сыктывкарский лесопромышленный комплеж".„им.Ленинского р комсомола и Харьковский ордена Ленина полйтешщческнй институт им. В.И.Ленина (72) Авторы изобретения (7) ) Заявители (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к информационно-преобразовательной технике и может .быть использовано в устройствах преобразования, например, напряжения в код.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь, содержащий цифроаналоговый преобразователь, компаратор, генератор. тактовых импульсов, триггер циклов, регистр сдвига, буферный регистр и блок управления, выполненный в виде выходного регистра, трехвходовых элементов И и линий задержки, количество которых равно разрядам преобразования, причем выход генератора тактовых импульсов (ГТИ) соединен с одним из входов элементов И каждого разряда, через элемент H cq счетными входами регистра сдвига каждого разряда (кроме первого), выполненного на последовательно соединенных RS-триггерах, через элемент И первого разряда регистра сдвига и через элемент задержки с одним из входов триггера циклов, выход которого соединен с элементом И первого разряда регистра сдвига, выход которого через линию задержки соединен с первым входом RS-триггера

1-го разряда регистра сдвига, выход которого соединен с вторым входом элемента И первого разряда, а выходы RS-триггеров всех последующих разрядов соединены с вторыми входами. элементов И соответствующих разря.дов и установочными входами выходного регистра блока управления, а также элементами И регистра сдвига соответствующего разряда, применяющимися для формирования бита. переноса сброса предыдущего RS-триггера в регистре сдвига, причем одновременно с этим третьим входы,элементов И каждого разряда соединены с выходом компаратора через элемент

НЕ, а выходы элементов И через ли- . нии задержки каждого разряда сое20 динены c R-входами триггеров выходного регистра, который посредством ключей управляет выходом цифроаналогового преобразователя (1).

Недостатком устройства является необходимость строгой синхронизации и задержки во времени тактового импульса на R-вход и импульса запуска, на S-вход триггера цикловая импульсов на S-входе и R-входе первого . разряда регистра сдвигат импульса

З0 .с выхода компаратора, тактового им995316 пульса и одновременно с этим наличия предыдущего состояния триггера сдвига соответствующего разряда.

Это усложняет отладку схемы, требует сложных в реализации и ненадежных в работе схем, перенастройки схем при переходе на другой диапазон такт вых частот, уменьшает быстродействие всего преобразователя в целом за счет наличия 2-тактной схемы синхронизации.

Цель изобретения — повышение быстродействия и надежности работы устройства.

Поставленная цель достигается тем что в аналого-цифровой преобразователь, содержащий блок управления, включающий регистр управления, выходы которого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход которого соединен с входной шиной, триггер циклов, первый вход которого соединен с шиной запуска, ге- нератор тактовых импульсов, выход которого соединен с первым входом регистра сдвига, введен буферный регистр и блок управления дополнительно включает узлы укорочения импульсов, генератор одиночных импульсов, элементы И и НЕ и линию задержки, причем выход триггера циклов соединен с входом генератора тактовых импульсов и с первым входом генератора одиночных импульсов, выход которого соединен с вторым входом регистра сдвига и через элемент НЕ с первым входом элемента И, второй вход которого соединен с вы.ходом регистра сдвига, а выход соединен с вторым входом триггера цик лов, S-входом первого триггера и .R-входами остальных триггеров регистра управления, С-входы которого соединены с соответствующими разрядными выходами регистра сдвига, а начиная с второго разряда через узлы укорочения с S-входами соответствующего разряда, при этом D-входы подключены к выходу компаратора, а выходы регистра управления подключены. к входам буферного регистра, управляющий вход которого через линию задержки соединен с последним разрядным выходом регистра сдвига и вторааи входом генератора одиночных импульсов.

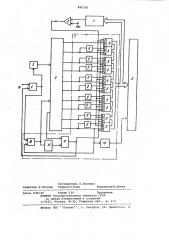

На,чертеже представлена схема аналого-цифрового преобразователя.

Преобразователь содержит цифроаналоговый преобразователь (ЦАП) 1, компаратор 2, генератор 3 тактовых импульсов (ГТИ), триггер 4 циклов,. регистр 5 сдвига, буферный регистр 6 и блок 7 управления, состоящий из регистра 8 управления на D-триггерах узлов 9 укорочения импульсов, генецоеобразователя 1 сравнивается с ратора 10 одиночных импульсов, элемента И 11, элемента НЕ 12, линии 13 за".,ержки,14 — шина запуска, Анало1о-цифровой преобразователь работает следующим образом.

5 Импульс запуска поступает на усо- тановочный вход триггера 4 цйклов, переводит его в состояние, включаю- щее генератор 3 тактовых импульсов и генератор 10 коротких одиночных им10 пульсов, выходной импульс которого необходим для записи в регистр 5 сдвига начальной информации (уровень 0 в первый разряд и уровень l во все последующие). С регистра 5

15 сдвига задержанный импульс, а также инвертированный элементом ЙЕ 12 импульс с выхода генератора 10 одиночных импульсов поступают на входы элемента И 11. В результате этого

g0 образуется импульс, сбрас. .г.ающий в нулевое состояние все разряды регистра 8 управления, кроме первого, а в первом триггере регистра 8 уровень l

25 Одновременно импульс .- выхода элемента И 11 поступает на сброс триггера 4 циклов, но, так как импульс запуска по длительности больше, чем импульс с»выхода элемента

3О И 11, триггер 4 циклов остается в прежнем состоянии.

После поступления импульса на

С-вход триггера 1-ro разряда регистра 8 управления на его выходе . 5 появляется сигнал, который коммутирует старший разряд цифроаналого-, вого. преобразователя 1. Вес (напряжение U< п ), соответствующий старшему разряду, сравнивается с исследуемым сигналом (напряжение Uщ )

4О на компараторе 2.

В случае 06к>ицап1 íà D-входы (до окончания тактового импульса, поступившего на С-вход) регистра 8 управления подается уровень 1, При этих условиях на выходе D-триггера регистра 8 управления сохраняется уровень 1, При U „

5О и происходит запись 0 на выходе. Следующие тактовые импульсы генератора 3 производят сдвиг уровня 0 с 1-го разряда во все последующие разряды регистра 5 сдви55 га.

Сформированные таким образом нулевые уровни для каждого разряда поступают на С-входы соответствующих

D-триггеров регистра 8 управления, 60 а также через узлы 9 укорочения импульсов на их S-входы. Выходы регистра 8 управления коммутируют соответствующие ключи ЦАП 1, при этом напряжение с выхода цифроаналогового

995316 иссз едуеьым сигналом П на компа- -.: ах раторе 2. При этом пройсходит суммирование весов (напряжений) каждого последующего разряда ЦАП 1 и выставляется код на -регистре 8 управления, определяющий величину входного исследуемого сигнала. . Импульс регистра 5 сдвига последнего разряда, записав в регистр 8 управления информацию по результатам поразрядного уравновешивания входного сигнала с опорным напряже нием ЦАП 1, через линию 13 задержки переписывает. ее в буферный регистр 6., Линия 13 задержки вводится с целью записи истинной информации из регистра 8 управления только лишь после прихода импульса с компаратора 2 на

D-вход последнего разряда регистра 8 управления. Одновременно импульс последнего разряда регистра 5 сдвига поступает .на генератор 10 одиночных импульсов, который при этом стирает информацию в регистре 5 сдвига и формирует на элементе И 11 им-. пульс, задержанный на время, определенное длительностью импульса генератора 10 одиночных импульсов. Импульс генератора 10 сбрасывает в начальное состояние все (кроме первого) разряды регистра 8 и перево-. дит триггер 4 циклов в,состояние, запрещающее работу генератора 3 до прихода следующего импульса Запуск (строб от ЭВИ или любой другой импульс). С приходом следующего импульса запуска процесс повторяется.

В буферном регистре информация сохраняется дс следующего цикла и может счйтываться в любое время, -вплоть до окончания нового цикла преобразования.

Влагодаря предлагаемому построению блока 7 управления преобразование заканчивается за время, мень-. шее длительности такта (в прототи-пе для преобразования необходимо:—

2 тактовых импульса) .

Таким образом, быстродействие устройства. увеличивается за счет отсутствия второго тактирующего -импульса в 1+1/и раз, где п-число. разрядов преобразования, и за счет .. сокращения периода цикла обработки сигнала по цепи IIAII - компараторблок управления. формула изобретения

Аналого-цифровой йреобразователь, содержащий блок управления, включающий регистр управления, выходы ко« торого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход. которого соединен с входной шиной, триггер циклов, первый вход. которого соединен с шиной запуска, генератор тактовых импульсов, выход которого соединен с первым входом регистра сдвига, отличающийся тем, что, с целью повышения быстродействия и надежности в работе, в него введен буферный регистр и блок управления дополнительно вклю»

20 чает узлы укорочения импульсов, генератор одиночных импульсов, эле- . менты И -и НЕ и линию задержки, причем выход триггера циклов соеди-. нен с входом генератора, тактовых

25 импульсов и с первым входом генератора одиночных импульсов, выход которого соединен с вторым входом регистра сдвига и через элемент НЕ с первым входом элемента H второй

3() вход которого соединен с выходом регистра сдвига, а выход соединен с вторым входом триггера циклов, S-входом первого триггера и R-входами остальных триггеров регистра управления, С-входы которого соединены . с соответствующими разрядными выходами регистра сдвига, а начиная с второго разряда через узлы укорочения с S-входами соответствующего раз. 4О ряда, при этом Р-входы подключены к выходу компаратора, а выходы регист,ра управления подключены к входам буферного регистра,. управляющий вход которого через линию задержки

45 со ходом регистра сдвига и вторым вхо-, дом генератора одиночных импульсов.

Источники информации, принятые во внимание при экспертизе

l. Управляющие вычислительные ма-5О шины в АСУ технологическими процессами. Под ред. Т.Харрисона. "Мир, 1975, т.l, с, 294-297.

995316

Составитель П.Беляева

Редактор В.Петраш Техред N.Íàäü Корректор И.Шучла

Заказ 670/45 Тираж 934 Подписное

ЙНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„, д, 4/5

Филиал ППП Патент, r. ужгород, ул. Проехтная, 4