Двухпетлевое устройство импульсно-фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву—

{22) Заявлено 24.04.81 (21) 3281682/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з

Н 03 1.?(00

Гасударственные кемитет

СССР (53) УДК 621.396..662 (088.8) Опубликовано 07.02.83. Бюллетень ¹5

Дата опубликования описания 17.02.83 лв делам лзабратений и еткрмткй

В

А. В. Пестряков,— М. Ю. Соловьев, Н. Н. Филим нов, "" " - -- : и В. В. Шахгильдян .

К, C

Московский ордена Трудового Красного Знамени электротехнический институт связи (72) Авторы, изобретения (71) Заявитель (54) ДВУХПЕТЛЕВОЕ УСТРОЛСТВО ИМПУЛЬСНОФАЗОВОЛ АВТОПОДСТРОИКИ ЧАСТОТЫ

Изобретение относится к радиоэлектронной технике и может быть использовано в быстродействующих устройствах формирования и стабилизации сетки частот.

Известны устройства импульсно-фазовой автоподстройки частоты (ИФАПЧ), содержащие две петли автоподстройки, в цепи обратной связи которых включены делители частоты с переменными коэффициентами деления. Известные двухпетлевые устройства ИФАПЧ позволяют сформировать сигналы с повышенной чистотой спектра (1).

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее включенные в кольцо первый подстраиваемый генератор, делитель частоты с переменным коэффициентом деления, первый импульсно-фазовый детектор (ИФД), второй подстраиваемый генератор, выход которого соединен с вторым входом первого импульсно-фазового детектора через первый делитель частоты с переменным коэффициентом деления (ДПКД), второй делитель частоты с переменным коэффициентом деления и второй импульсно-фазовый детектор, другой вход которого подключен к опорному генератору (2).

Недостатком известного устройства является низкое быстродействие. Это связано с тем, что инерционность охватывающего первый подстраиваемый генератор кольца ИФАПЧ, определяющая быстродейст5 вие всего устройства, не может быть сделана малой в силу ограниченности полосы перестройки генератора. Максимальное быстродействие в известном устройстве получается при использовании ИФД с трапецеидальной характеристикой, значение крутизны рабочего участка которой удовлетворяет равенству Яу Г (ч — ч,) >р =1, где 2у=)Щ 15У-полоса удержайия петли

ИФАПЧ;

К„Мз,1) — коэффициенты деления соот15 ветственно первого, второго

ДПКД и делителя частоты с фиксированным коэффициентом деления;

s — крутизна перестройки генератора;

20 V — максимальное значение модуля выходного напряжения ИФД;

F (м-е!-крутизна нормированной характеристики ИФД в рабочей точке Ч,;

995336

3 — разность фаз сигналов на входах импульсно-фазового детектора;

Тр — период регулирования в петле

ИФАПЧ.

При выполнении указанного равенства процесс установления разностей фаз генераторов длится один период регулирования, если начальная фаза выходного сигнала такова, что выходной импульс второго

ДПКД попадает на рабочий участок характеристики ИФД. В этом случае набег фазы генератора за период регулирования при любой начальной частотной расстройке таков, что следующий за первым импульс с выхода ДПКД попадает в точку характеристики ИФД, соответствующую положению устойчивого равновесия в устройстве.

Максимально возможный набег фазы генератора за период регулирования составляет величину/ч -ч,/D, где -ч, и — начало и конец рабочего участка характеристики ИФД, независимо от того, в какой момент времени по отношению с опорному импульсу приходит импульс с выхода ДПКД.

Выходной импульс ДПКД в известном устройстве может появиться в любой момент времени по отношению к импульсу опорной частоты, определяемый, в основном, начальным состоянием тракта счета

ДПКД. Величина рабочего участка характеристики ИФД при оптимальном по быстродействию выборе параметров кольца ИФАПЧ мала и может составлять, с учетом возможности перестройки генератора, доли процента от протяженности характеристики

ИФД. Поэтому переходный процесс может продолжаться длительное время (десятки, сотни периодов регулирования), необходимое для достижения разностью фаз сигналов на входах ИФД величины, соответствующей рабочему участку его характеристики, после чего установление происходит за один период регулирования.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в двухпетлевое устройство ИФАПЧ, содержащее соединенные в кольцо первый подстраиваемый генератор, делитель частоты с фиксированным коэффициентом деления, первый импульсно-фазовый детектор, второй подстраиваемый генератор, выход которого соединен с вторым входом первого импульсно-фазового детектора через первый делитель частоты с переменным коэффициентом деления, второй импульснофазовый детектор, другой вход которого подключен к опорному генератору, введены формирователь стробирующих импульсов, формирователь импульсов сброса, логический блок, при этом вход формирователя стробирующих импульсов и вход восстановления исходного состояния логического блока соединены с выходом опорного генератора, первый и второй выходы формирова4 теля стробирующих импульсов соединены соответственно с первым и вторым входами управления логического блока и с первым и вторым входами формирователя импульсов сброса, первый сигнальный вход логического блока соединен с выходом второго делителя частоты с переменным коэффициентом деления, выходы формирователя импульсов сброса соединены с вторым и третьим сигнальными входами логического блока, выход логического блока подключен к входу сброса ДПКД.

Логический блок содержит первый .логический элемент И, один вход которого является первым входом управления, другой вход, являющийся первым сигнальным входом, соединен с входом второго логического элемента И и с входом сброса первого триггера, выход соединен с установочным входом второго триггера, установочный вход первого триггера соединен с входом сброса второго триггера, являющимся входом восстановления исходного состояния, второй вход второго логического элемента И является вторым входом управления, выход второго триггера соединен с одним входом третьего логического элемента И, другой вход которого является вторым сигнальным входом, выход первого триггера соединен с одним входом четвертого логического элемента И, другой вход которого является третьим сигнальным входом, выходы второго, третьего и четвертого логических элементов И соединены с входами логического элемента ИЛИ, выход которого является выходом логического блока.

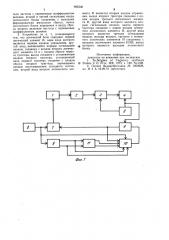

На фиг. 1 изображена структурная электрическая схема двухпетлевого устройства импульсно-фазовой автоподстройки частоты; на фиг. 2 — структурная электрическая схема логического блока; на фиг. 3 — развернутая во временной области характеристики ИФД (а) и временные диаграммы (б, в, г, д, е, ж, з) напряжений в точках структурной схемы.

Двухпетлевое устройство импульснофазовой автоподстройки частоты, содержит соединенные в кольцо первый подстраиваемый генератор 1, делитель 2 частоты с фиксированным коэффициентом деления, первый импульсно-фазовый детектор 3, второй подстраиваемый генератор 4, выход которого соединен с вторым входом первого импульсно-фазового детектора через первый делитель 5 частоты с переменным коэффициентом деления, второц делитель 6 частоты с переменным коэффициентом деления и второй импульсно-фазовый детектор 7, другой вход подключен к опорному генератору 8, при этом вход формирователя 9 стробируюыц х импульсов и вход восстановления исходного состояния логического блока 10 соединены с выходом опорного генератора 8, первый и второй выходы формирователя 9 стробирующих импульсов соединены с первым и вторым входами форми995336 рователя 11 импульсов сброса и с первым и вторым входами управления логического блока 10, первый сигнальный вход логического блока 10 соединен с выходом второго делителя 6 частоты с переменным коэффициентом деления, второй н третий сигнальные входы логического блока 10 соединены с выходами формирователя 11 импульсов . сброса, выход логического блока 10 подключен к входу сброса второго делителя 6 частоты с переменными коэффициентом деления.

Логический блок 10 содержит первый логический элемент 12 И, один вход которого является первым входом управления, другой вход, являющийся первым сигнальным входом, .соединен с входом второго логического элемента 13 И и с входом сброса первого триггера 14, выход соединен с установочным входом второго триггера 15, установочный вход первого триггера 14 соединен с входом сброса второго триггера 15, являющимся входом восстановления исходного состояния, второй вход второго логического элемента 13 И является вторым входом управления, выход второго триггера 15 соединен с одним входом третьего логического элемента 16 И, другой вход которого является вторым сигнальным входом, выход первого триггера 14 соединен с одним входом четвертого логического элемента И 17, другой вход которого является третьим сигнальным входом, выходы второго, третьего и четвертого логических элементов И соединены с входами логического элемента 18 ИЛИ, выход которого является выходом логического блока 10.

Устройство работает следующим образом.

Опорный импульс (фиг. Зб) приводит логический блок в исходное состояние, при котором разрешается прохождение второго импульса сброса на выход логического блока 10, Формирователь 9 стробирующих импульсов формирует первый стробирующий импульс на первом выходе (фиг. Зв) соответствующий нижнему горизонталь< ному участку характеристики ИФД 7.

По заднему фронту первого стробирующего импульса формирователь 11 импульсов сброса формирует первый импульс сброса (фиг. Зд). При этом на втором выходе формирователь 9 стробирующих импульсов

-формирует второй стробирующий импульс (фиг. Зг), соответствующий рабочему участку характеристики ИФД 7. По заднему фронту второго стробирующего импульса формирователь 11 импульсов сброса формирует второй импульс сброса (фиг. 3e).

На фиг. Зж показана диаграмма выходного напряжения логического блока 10. Если выходной импульс ДПКД 6 (фиг. Зз) приходит в момент действия первого стробирующего импульса, то он переводит логический блок 10 в состояние, при котором на его выход проходит только первый импульс сброса. Сброс ДПКД 6 происходит в момент времени, соответствующий началу рабочего участка характеристики ИФД 7.

Если выходной импульс ДПКД 6 не приходит в период действия первого и второго

5 стробирующих импульсов, (тогда он должен будет прийти в момент, соответствующий верхнему горизонтальному участку . характеристики ИФД 7), то логический блок 10 остается в исходном состоянии. Второй импульс сброса, пройдя через логичес10 кий блок 10, сбрасывает ДПКД 8 в момент, соответствующий началу верхнего горизонтального участка характеристики ИФД7.

В обоих случаях следующий за первым импульс ДПКД 6 обязательно попадает на рабочий участок характеристики ИФД 7

15 и переходной процесс заканчивается за один период регулирования. Если выходной импульс ДПКД 6 приходит в период действия второго стробирующего импульса, логичес. кий блок 10 переводится в состояние, запрещающее прохождение второго импульса

2 сброса на выход. Устройство ИФАПЧ при этом работает в обычном режиме автоподстройки с оптимальными по быстродействию параметрами и начальными фазовыми соотношениями сигналов.

2S

Преимущество устройства по сравнению с известным заключается в повышении быстродействия (уменьшении времени переходного процесса). При этом достигается быстродействие двухпетлевого устройства, близкое к предельному быстроЗО действию устройства автоматического ре; гулирования.

Формула изобретения

1. Двухпетлевое устройство импульснофазовой автоподстройки частоты, содержащее соединенные в кольцо первый подстраиваемый генератор, делитель частоты с фиксированным коэффициентом деления, первый импульсно-фазовый детектор, второй подстраиваемый генератор, выход которого соединен с вторым входом первого импульсно-фазового детектора через первый делитель частоты с переменным коэффициентом деления, второй делитель частоты с переменным коэффициентом деления и второй импульсно-фазовый детектор, 45 другой вход которого подключен к опорному генератору, отличающееся тем, что, с целью повышения быстродействия, в него введены формирователь стробирующих импульсов, формирователь импульсов сброса и логический блок, при этом вход формирователя стробирующих импульсов и вход восстановления исходного состояния логического блока соединены с выходом опорного генератора, первый и второй выходы формирователя стробирующих импульсов соединены с первым и вторым входами фор55 мирователя импульсов сброса и с первым и вторым входами управления логического блока, первый сигнальный вход логического блока соединен с выходом второго дели995336

7 теля частоты с переменным коэффициентом деления, второй и третий сигнальные входы логического блока соединены с выходами формирователя импульсов сброса, выход логического блока подключен к входу сброса второго делителя частоты с переменным коэффициентом деления.

2. Устройство по п. 1, отличающееся тем, что логический блок содержит первый логический элемент И, один вход которого является первым входом управления, другой вход, являющийся первым сигнальным входом, соединен с входом второго логического элемента И и с входом сброса первого триггера, выход соединен с установочным входом второго триггера, установочный вход первого триггера соединен с входом сброса второго триггера, являющимся входом восстановления исходного состояния, второй вход второго логического эле8 мента И является вторым входом управления, выход второго триггера соединен с одним входом третьего логического элемента И, другой вход которого является вторым сигнальным входом, выход первого триггера соединен с одним входом четвертого логического элемента И, другой вход которого является третьим сигнальным входом, выходы второго, третьего и четвертого логических элементов И соединены с входами логического элемента ИЛИ, выход которого является выходом логического блока.

Источники информации, принятые во внимание при экспертизе

1. Technignes of freguency synthesis

15 Stokes Ч. О. Proc. IEE, 1973, ч. 120. No 10К.

2. Патент Великобритании № 1263928, кл. Н 3 А 16.02.72 (прототип).

995336

Редактор В. Пилипенко

Заказ 620!46

Составитель С. Даниэлян

Техред И. Верес Корректор О, Билак

Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП сПатент», г. Ужгород, ул. Проектная, 4