Устройство фазовой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<и>995360 (61) Дополнительное к авт. саид-ву— (Д) М. gy.ç

Н 04 L 7/02 (22) Заявлено 260181 (21) 3240603/18-09 с присоединением заявки М— (23) Приоритет —.

Государственный комитет

СССР по делам изобретений и открытий

iSS)УДК 621.394. . 662 (088. 8) Опубликовано 07.0283. Бюллетень М5

Дата опубликования описания 07.0233 (72) Авторы изобретения

С.И. Лачинов, Н.Н. Ольшевский и Б.В. Султан

Пензенский политехнический институт (71) 3аяв итель (54) УСТРОЙСТВО -ФАЗОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к технике электросвязи и может быть использовано в системах фазовой синхронизации для устройств передачи дискретной инФормации.

Известны цифровые системы фазовой синхронизации, в которых испольэуххх я цифровые отсчеты от аналого-цифройфго . преобразователя, находящегося до пет- .1р ли системы синхронизации (1).

Указанные устройства отличаются сложностью, поскольку в состав их входят функциональные преобразователи, реализация которых требует большого объема электронной памяти.

Известно устройство фазовой синхронизации, содержащее последовательно соединенные фазовый детектор, дискретный усредняющий блок, блок добавленияясключения импульсов.и счетчик, а также генератор опорной частоты, выход которого подключен к входам счетных импульсов фазового детектора и блока добавления-исключения имульсов, а также делитель частоты (2j.

Недостатком этого устройства фа.. зовой синхронизации является его ограниченный частотный диапазон.

Цель изобретения — расширение частотного рабочего диапазона.

Для достижения указанной цели в устройство фазовой синхронизации, содержащее последовательно соединенные фазовый детектор, дискретный усредняющий блок, блок добавления-исключения импульсов и счетчйк, а также генератор опорной частоты, выход которого подключен к входам счетных импульсов фазового детектора и блока добавления-исключения импульсов и делитель частоты, введены формирова- тель импульсов, элементы задержки, элемент ИЛИ и последовательно соеди-. ненные дополнительный счетчик, блок перезаписи кодов, запоминающий регистр и блок совпадения кодов, причем сигнальный вход фазового детектора объединен с входом формирователя импульсов, выход которого через делитель частоты подключен к входу перезаписи запоминающего регистра, к первому входу элемента ИЛИ и к входу первого элемента задержки, выход которого подключен к управляющему входу блока перезаписи кодов непосредственно и через второй элемент задержки к вхо- ду сброс дополнительного счетчи ка, к счетному входу которого подклю.чен выход генератора опорной частоты, выходы счетчика подключены к соответ60

9953

4 ствующим входам блока совпадения ко-. дов, выход которого подключен к опорному входу фазового детектора непосредственно и.через элемент ИЛИ к входу сброс счетчика.

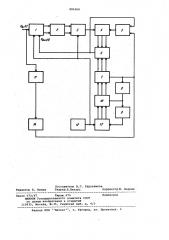

На чертеже изображена структурная электрическая схема предлагаемого устРойства.

Устройство фаэовой синхронизации содержит фазовый детектор 1, дискретный усредняющий блок 2, блок 3 добав- 10 ления-исключения импульсов, счетчик 4 элемент ИЛИ 5,блок 6 совпадения кодов, запоминаккций регистр 7,элементы 8 и 9 задержки, блок 10 перезаписи кодов, формирователь 11 импульсов, генератор 12 опорной частоты, дополнитель- 15 ный счетчик 13, делитель 14 частоты.

Устройство фазовой синхронизации работает следующим образом.

Вхождению устройства данного в режим работы подстройки частоты пред- 20 шествует предварительный цикл. Длительность этого цикла Трформируетсяя» с помощью делителя 14 частоты, приведенного перед началом работы в нулевое состояние. На вход делителя час-25 тоты 14. поступают короткие импульсы с формирователя 11, синхронные с пе-, реходами через ноль сигнала О „(Ц, При этом т с ВХ1

30 т = — 2

О где -коэффициент деления делителя где частоты 14.

35 вК= .пеРеход входного сигнала.

1 вх

В течение этого времени импульсы с выхода генератора 12 поступают на дополнительного вход счетчика 13, s 40 результате чего в последнем накапливается число Н 7 у =оо . где &„ - частота генератора 12 опорной частоты.

Т

По окончании интервала времени т.е. в момент переполнения делителя

14 частоты, его выходным импульсом ос уществляется установка s нулевое со7 и. стояние запоминающего регистрд . 50 счетчика 4 через элемент ИЛИ 5, а спустя время задержкй В„и, обеспеемое элементами 8 и 9 соответстнно (ь + с c „) - перепись в запоминающий регистр 7 числа Й;,-нак †.55 опленного в старших разрядах дополнительного счетчика 13 и сброс, этого

4< счетчика. число )4 у где. и число отбрасываемых (неисполь.зуемых)разрядов дополнительного счетчика 13, пропорционально среднему (свободному от влияния наложенных на . сигнал шума значению периода вход- 65 ного сигнала Te ср . Это число используется для формирования выходной частоты устройства фазовой синхронизации, осуществляемого следующим образом.

Импульсы.с.выхода генератора 12, проходя через блок 3 добавления-исключения импульсов, поступают на вход счетчика 4. В момент равенства чисел в этом счетчике и запоминающем регистре 7 срабатывает блок 6 совпадения кодов и выдает импульс, устанавливающий в ноль счетчик 4 ° Последний вновь начинает заполняться импульсами генератора 12, снова срабатывает блок 6 совпадения кодов и т.д., т.е. процесс повторяется. Период следования выход- " ных импульсов блока 6 совпадения кодов

1 й1 т о откуда, с учетом (1) имеем ЗЫх 7вх ср TaxaM образом, частота выходного сигнала предлагаемого устройства

Ев,„=.т,„равна, частоте U zz (t )

Начальная фаза формируемого таким образом сигнала корректируется с помощью фазового детектора 1, дискретного усредняющего блока 2, блока 3 добавления-исключения импульсов путем добавления {исключения) импульсов (в зависимости от определяемого фазо-.. вым детектором 1 знака рассогласования фаз Ов, (+) и Озы,,(+) в последовательности выходных ймпульсов генератора 12, поступающих на счетчик 4.

По окончании предварительного цикла дополнительным счетчиком 13 начинается измерение нового среднего значения периода входного сигнала, которое осуществляется аналогично в течение юд полупериодов Uq)((4)у выход ным импульсом делителя 14 частоты вновь производится подготовка (сброс) запоминающего регистра 7 и перепись в. него нового числа. Этот процесс .

/ периодически повторяется. Тем самым в устройстве осуществляется дискретное слежение за частотой входного сигнала Озх(t) в результате чего соэ» даются более благоприятные условия для работы схемы корректировки начальной фазы.

Благодаря отсутствию в устройстве. при формировании выходного сигнала линейного преобразования кода в частоту, удается избежать неравномерности следованйя выходных импульсов синтезатора дискретных частот (в предлагаемом варианте эту роль выполняют счетчики 4 и 13, запоминающий регистр

7, блок 6 совпадения кодов и блок 10 перезаписи кодов. Импульсы на выходе блока 6 совпадения кодов имеют равномерную расстановку во времени (сле"

Дуют с периодом 6% cp ). В связи с этим отсутствует необходимость деле995360

5 ния выходной частоты синтезатора дискретных частот (последняя оказывается равной выходной частоте схемы или частоте входного сигнала).

Таким образом, при использовании той же элементной базы, что и в известном устройстве сТВНоВНТсН возмож" ным увеличение вер;. ней .границы частотного диапазона предлагаемого устройства.

Формула изобретения

Устройство фаэовой синхронизации, содержащее последовательно соединен- 5 ные фазовый детектор, дискретный усредняющий блок, блок добавления-исключения импульсов и счетчик, а также генератор опорной частоты, выход ко-. торого подключен к входам счетных им- -у пульсов фазового детектора и блока добавления-исключения импульсов и -делитель частоты, о т л и ч а ю щ е еся тем, что, с целью расширения частотного рабочего диапазона, в него введены формирователь импульсов, элементы задержки, элемент ИЛИ и последовательно соединенные дополнитель.ньМФ счетчик, блок перезаписи кодов, заищминающий регистр и блок совщдуэ6 ния кодов, причем сигнальный вход фазового детектора объединен с входом формирователя импульсов,.выход которого через делитель частоты подключен к входу перезаписи запоминающего регистра, к первому входу элемента ИЛИ и к входу первого элемента задержки, выход которого подключен к управляющему, входу блока перезаписи кодов непосредственно и через второй"элемент задержки к входу сброс дополнительного счетчика, к счетному входу которого подключен выход генератора опорной частоты, выходы счетчика подключены к соответствующим входам блока совпадения кодов, выход которого подключен к опорному входу фазового детектора непосредственно и через элемент ИЛИ к входу сброс счетчика

Источники информации, принятые во внимание при экспертизе

1. Жодэишскнй И.И. Цифровые систе- ьы фазовой синхронизации.- Радиотехника и электроника,1979,т.24,В 9, с. 1786. .-2. Жодэишский M.È. и др. Расчетные модели .цифровых систем ФАН . -Известия . вузов СССР. Радиоэлектроника. 1976, т. 19, Р 3, с. 43 (прототип).

995360

Заказ 672/47 Тираж 675

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035р Иосква, Ж-35, Раушская наб. д. 4/5

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель В.Г. Евдокимова

Редактор Е. Кинив Техред Л.Пекарь Корректор И. Шароши