Устройство для вычисления квадратного корня из суммы квадратов двух чисел

Иллюстрации

Показать всеРеферат

О П И С А Н И:Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ рщ997034,Соеоз .Советснни. Социалистических

Реслублнй (61) Дополнительное и авт. свид-ву(22) Заявлено 060781 (21) 3313677/18-24

Р М.ип.

G06 F 7/552 с присоединением заявки НоГосударственный комитет

- СССР по делам изобретений и открытий (23) ПриоритетОпубликовано 150283, Бй>ллетень Hо 6

f53) У@К %81. 325 (088 . 8) Дата опубликования описания 150283

f72) Автор изобретения

Н.Н. Протченко (71).Заявитель (54 ) VCTPOACTBO ДЛ ВЫЧИСЛЕНИН KB PATHOKO KOPHH

ИЭ СУММЫ КВАДРАТОВ ДВУХ .ЧИСЕЛ в" «+ +San инв+ -сдб

Изобретение относится к вычислительной технике и может быть применено в специализированных цифровым вычислителях.

Известно устройство для вычисле.ния квадратного корня иэ суммы квадратов двух чисел, содержащее сумматор и коммутатор (1,3.

Недостатками этого устройства являются низкая точность вычисления и относительно низкое быстродействие.

Наиболее близкиМ к предлагаемому по техничаекой сущности является устройство для вычисления квадратно

ro корня иэ суммы квадратов двух чисел, содержащее коммутатор -и сумматор, причем цервые и вторые входы коммутатора подключены. соответственно ко входным шинам величин х и у,. а выход - ко входу сумматора. Цикл вычислений состоит из девяти тактов, задаваемых управляющими сигналами, формируемыми с помощью распределителя импульсов. Операции вычитания, сдвига и сложения кодов выполняются последовательно, причем используется одна- схема суммирования, что связано с усложнением .схемы управления и коммутации, а также с необходимостью запоминания промежуточных результатов 2).

Недостатками этого устройства

5 являются повышенная сложность структуры и относительно низкое быстродействие, которые являются следствием последовательной организации процесса вычислений. Время вычисле1р ния определяется выражением где Г - время выполнения одной операции суьвжрования чисел; . Ц ® — время записи одного числа в сумматор или регистр; Сниа- время инвертирования кода; — время сдвига числа на один разряд.

Цель изобретения - упрощение и повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство для вычисления квадратного корня из суммы квадратов двух чисел, содержащее коммутатор, первый сумматор, причем информационные входы коммутатора подключены к входам аргументов Х и У устройства, а выход — к первому входу

997034

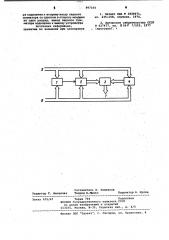

4 первого сумматора, содержит схему сравнения кодов и второй суммаrop, первая и вторая группы входов второго сумматора.и схемы сравнения ,объединены и подключены к входам аргументов Х и У устройства, выход схемы сравнения кодов подключен к управляющему входу коммутатора, выход второго сумматора подключен к второму. входу первого сумматора со сдвигом в сторону младших на один разряд, выход первого сумматора подключен к выходу устройства, На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит схему сравнения кодов 1, коммутатор 2, первый сумматор 3, второй сумматор 4, вход« ные .шины 5 и 6 величин:Х и У соответственно, выходную шину 7, и-разрядные входные шины,5 и 6 соединены поразрядно соответственно с первыми 20 и вторыми входами схемы 1, коммутатора 2 и второго сумматора,4. Выход схемы 1 подключен к управляющему вхо, ду первого сумматора 3. Выход второго сумматора 4, содержащий п-.1 раэ- 2р ряд, подключен к второму входу нервого сумматора 3 со сдвигом в сторону младших на один разряд. Выходы разрядов с 1-го по (n+1)-й первого сумматора 3 подключены к выходной шине 7.

Работа устройства основана на аппроксимации вычисляемой функции следующей приближенной зависимостью;

454х У - «A+n$(lxl+lvl), (2) 33 где Д= /у /, если/Х/) /y/j(3)

Д=/у /, если/Х/У/,>

На входные шины 5 и 6 поступают прямые двоичные коды абсолютных значений величин Х и У. Схема 1 обеспечивает проверку выполнения усло- щ вий (,3) и (4) и формирует сигнал управления коммутатором 2. При выполнении условия (3) на управляющий вход коммутатора 2 поступает логичес кая "1" и на первый вход сумматора

3 проходит прямой код величины /х/.

Если выполняется условие (4), то на выходе схемы 1 формируется логический "О" и коммутатор 2 подключает к первому входу сумматора 3 прямой код величины /у/ . Таким образом, на, первый вход сумматора 3 поступает код большей величины, а в случае их равенства - код величины /х/. Сумматор 4 обеспечивает суммирование прямых кодов величин /х/ и /у/ в 40 соответствии с выражением (2). Уменьшение полученной суммы в два раза достигается подключением разрядов выхода сумматора 4 к разрядам второ

ro входа сумматора 3 со сдвигом 65 в сторону младших на один разряд.

Старшим разрядом .выхода сумматора 4 является выход переноса старшего разряда, а младшим - второй разряд.

Первый разряд выхода сумматора 4 не используется.

Сумматор 3 обеспечивает суммирование слагаемых, входящих в выражение (2), и на его выходе 7 формируется конечный результат. Точность вычислений функции полностью соответствует точности, обеспечиваемой известным устройством. При этом зависимость относительной погрешности вычислений функции от соотношения входных величин описывается кривой, а максимальная погрешность вычислений не превышает

5,723.

В предлагаемом устройстве реализован параллельный способ вычислений, причем результат вычислений формируется на выходе устройства с задержкой относительного момента поступления входных величин в параллельном коде, определяемой выражением где - задержка, вносимая схемой суммирования, Сопоставляя выражения (6) и (1) находим, что ГрС Г@, т.е. быстродействие предлагаемого устройства выше, чем известного. Входящие в состав предлагаемого устройства элементы, работают одновременно и необ- ходимы непосредственно для выполнения вычислений. Кроме того, вспомогательные элементы, имеющиеся в известном устройстве, в состав предлагаемого устройства не входят, что упрощает устройство.

Формула изобретения

Устройство для вычисления квадратного корня из суммы квадратов двух чисел, содержащее коммутатор, первый сумматор, причем информационные входы коммутатора подключены к входам аргументов Х и У,устройства, а выход - к первому входу первого сумматора, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повышения быстродействия, оно содержит схему сравнения кодов и второй сумматор, первая и вторая, группы входов второго сумматора и схемы сравнения объединены и нодклйчены к входам аргументов Х и У устройства, выход схемы сравнения кодов подключен к управляющему входу коммутатора, выход второго суммато997034

1. Патент США 9 3829671, кл. 235-158, опублик. 1970.

Составитель В. Эеменков

Редактор Т. Веселова Техред К.Иыцьо Корректор И. Шулла

Заказ 935/67

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ра подключен к второму входу первого

:сумматора со сдвигом в сторону младших на один раэряд, выход первого сум-,. матора подключен к выходу устройства

Источники информации, принятые во внимание при экспертизе

2. Авторское свидетельство СССР

9 627477, кл. 6 06 f 7/552, 1977 (прототип).