Многоканальный цифровой фильтр

Иллюстрации

Показать всеРеферат

«11997232

Союз. Советских Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт. свид-ву-. (22) Заявлеио10.0431 (21} 3303883/18-24 с присоединением заявки ¹(23) Приоритет—

Опубликовано 1502.83. Бюллетень ¹ б

Дата опубликования описания 150283

Р Ц К з

Н 03 Н 17/06

Государственный комитет

СССР по делим изобретений и открытий ($3) УДК 68i. 32 (088. 8) »

Н»Ю. Филиппов, Ю.С. Ицкович, и Т.П. Иванк на -.": .. *

f., (72) Авторы изобретения

I: (71) 3а явитель (5 4 ) МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к радиоприемной технике, в частности к цифровой фильтрации, и может использоваться в ци фро вых корреляционных фильтрах и анализаторах спектра.

Известны устройства цифровых интеграторов, используемые в цифровых корреляционных фильтрах.

Известен интегратор для цифрового корреляционного фильтра, содержащий два квантователя опорного сигнала, два умнох<ителя и два накапливающих сумматора. В интеграторе входной сигнал поступает на умножители,, на вторые входы которых поступает квантован- 15 ный опорный сигнал. Выходной сигнал уМножителей интегрируется в накапливающем сумматоре, в результате чего на выходе сумматора формируется сигнал проинтегрированного во врем<зни 20 произведения входного и опорного сигналов (1) .

Недостатком известного интегратора является его- черезмерная сложность, 25 обусловленная наличием квантователей и умножителей, что ограничивает область применения интегратора, в част ности, он не может быть использован в многоканальных фильтрах. 30

Известен также цифровой корреляционный фильтр, который содержит соединенные в кольцо комбинационный сумматор, регистр,,двухканальный блок памяти, инвертор (2) .

Недостатком данного интегратора является то, что в. каждый момент квантования он всегда умнов<ает предыдущий выходной сигнал на минус единицу, т.е. является фильтром верхних частот, что ограничивает область его применения, так как, например, известный интегратор не может быть использован в. качестве интегратора для вторичного интегрирования.

Цель изобретения - расширение функциональных возможностей за счет дополнительной низкочастотной фильтрации.

Поставленная цель достигается тем, что в многоканальный цифровой фильтр, содержащий сумматор, первый вход которого является входом фильтра, а выход сумматора соединен со входом регистра, блок памяти, выход которого соединен со вторым входом сумматора, вход переноса которого является управляющим входом фильтра, введены элемент ИЛИ-НЕ, группа элементов НЕ, группа элементов И-НЕ и группа бло997232 ков коммутации, .каждый из которых содержит элемент 2И-ИЛИ-НЕ, элемент

И-НЕ и элемент ИЛИ-НЕ, причем выход элемента 2И-ИЛИ"НЕ соединен с первым входом элемента И-НЕ, выход которого подключен к первому входу элемента

ИЛИ-НЕ блока коммутации, при этом выходы разрядов регистра подключены ко входам соответствующих элементов !

НЕ группы и- первым входом элементов .

2И-ИЛИ-НЕ соответствующих блоков ком- 10 мутации группы, выходы элементов НЕ группы подключены ко вторым входам элементов. 2И-ИЛИ-HE соответствующих блоков коммутатации группы, первый и второй входы элемента ИЛИ-НЕ объединены соответственно с третьим и четвер- 5 тым входами элементов 2И-ИЛИ-НЕ блоков коммутации группы и являются соответственно входами низкочастотного и высокочастотного диапазона фильтра, выход элемента ИЛИ-НЕ подключен ко 20 вторым входам элементов ИЛИ-НЕ блоков коммутации группы, вторые входы элементов И-НЕ блоков коммутации объединены и являются входом начальной установки фильтра, выходы элемен- Я5 тов ИЛИ-НЕ блоков коммутации соеди .ены с первым входом блока памяти, выходы элементов И-EIE блоков коммутации группы соединены со вторым входом блока памяти, выход которого соеди- щ0 нен с первыми входами элементов И-IIE группы, вторые входы которых объединены и являются стробирующим входом фильтра, выходы элементов И-НЕ группы являются выходами фильтра. 35

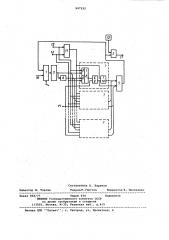

На чертеже представлена блок-схема устройства.

Устройство содержит сумматор l, блок памяти 2, группу элементов И-BI."

3, Упра вляющий вход 4, регистр 5, группу элементов НЕ б, группу блоков 7 коммутации, количество которых соответствует количеству разрядов,, элемент 8 2И-ИЛИ-НЕ, элемент 9 И-НЕ, и элемент 10 ИЛИ -НЕ, элемент 11

ИЛИ-НЕ, управляющий вход 12 вычитания45 управляющий вход 13 .сУммирования, вход 14 обнуления блока памяти, стробирующий вход 15, вход 16 интегратора, . выход 17 интегратора.

Принцип действия фильтра заключает- 50 ся в следующем.

Перед началом Работы ячейки памяти .блока,2 обнуляются. Для этого по входу 14 обнуления на входы блока 7 коммутации подается уровень логичес- 55 кого нуля и независимо.от состояний других входов блоков 7 на его втором выходе устанавливается уровень логического нуля, а на первом выходе уровень логической единицы, что сост- ветствует записи логического нуля по парофазным входам блока 2 в соответствующую ячейку памяти. После обнуления ячеек памяти блока 2 по входу 14 на входы блоков 7 подается потенциал логической единицы, который не изме. няется в течение всей последующей работы.

При работе фильтра в качестве фильтра верхних частот н каждом такте квантования происходит вычитание из текущего значения входной величины результата интегрирования, полученного в предыдущем такте квантования.

Это эквивалентно операции сложения в сумматоре 1 текущего значения входной величины с инверсным значением результата ийтегриронания предыдущего такта квантования при подаче на вход переноса н младший разряд сумматора 1 уровня логической единицы по входу 4. Получение на втором входе сумматора 1 в текущем такте квантования инверсного значения результата интегрирования, полученного н предыдущем такте квантования, осуществляется следующим образом. В предыдущем такте квантования результат суммирования из сумматора 1 переписывается н регистр 5, с выхода которого поразрядно прямо и через группу элементов

НЕ б подается соответственно на входы блоков 7 коммутации, на соответствующие входы которых со входа 12.поступает потенциал логической единицы, и на другие входы — потенциал логического нуля со входа 13. При этом если в однол из разрядон регистра 5 записан," единица, то на одном выходе соответствующего блока 7 коммутации устанавливается потенциал логической единицы, а на другом выходе — потенциал логического нуля, что соответствует записи н ячейку блока памяти 2 логического нуля. Если же н одном из разрядов регистра 5 записан нуль, то на перном выходе соответствующего блока

7 коммутации устанавливается потенциал логического нуля, а на другом выходе — потенциал логической единицы, что соответствует записи н блок 2 памяти логической единицы.

Считывание из блока 2 памяти происходит путей подачи по входу 12 и входу 13 логического нуля, тогда независимо от сигналов на входах блоков 7 коммутации, на выходах этих блоков будут уровни логического нуля, что соответствует режиму считывания из блока 2 памяти. При работе фильтра в качестве фильтра нижних частот н каждом -акте, квантования происходит сложение н сумматоре текущего значения входной неличины с прямым значением Результата интегрирования, полученного в предыдущем такте квантования, для чего на вход переноса в младший разряд сумматора 1 подается сигнал логического нуля по входу 4.

Получение прямого значения результата интегрирования в блоке 2 памяти достигается следующим образом. В предыдущем такте квантования резуль997232 тат суммирования из сумматора 1 переписывается в регистр 5, с выхода которого поразрядно. непосредственно через группу элементов НЕ 6 подается соответственно на входы блоков 7 коммутации, на соответствующие входы 5 которых со входа 12 поступает потенциал логического нуля, а потенциал логической единицы со входа 13. При этом если в одном из разрядов регистра 5 записана единица, то на первом . ð выходе соответствующего блока 7 коммутации устанавливается потенциал. логического, нуля, а на другом выходепотенциал логической. единицы, что соответствует записи в ячейку блока памяти логической единицы. Если же в одном из разрядов регистра 5 записан нуль,то на первом выходе соответствующего блока 7,коммутации устанавливается потенциал логической единицы, а на другом выходе — потенциал логического нуля, что соответствует записи в ячейку блока памяти 2 логического нуля.

Считывание из блока 2 памяти при работе фильтра в качестве фильтра ниж25 них частот аналогично считыванию из блока 2 памяти при работе фильтра в качестве фильтра верхних частот. При поступлении управляющего сигнала на вход 15 сигнал из блока 2 памяти пос- Зр тупает через группу элементов И-ПЕ 3 на выход устройства.

Эффективность фильтра особенно высокая при разработке многоканальных корреляционных фильтров и анализаторов спектра, в которых используется большое количество фильтров. В этом случае использование данного фильтра, который можно использовать в качестве фильтра верхних и нижних частот, из 4р меняя лишь управляющие сигналы, позволит существенно упростить прибор в целом, уменьшить затраты на его изготовление и регулировку.

Формула изобретения

14ногоканальный цифровой фильтр, содержащий сумматор, первый вход которого является входом фильтра, а 50 выход сумматора соединен с входом регистра, блок памяти, выход которого ,соединен с вторым входом сумматора, вход переноса которого является управляющим входом фильтра,, о т л и ч а юшийся тем, что, с целью расширения функциональных воэможностей за счет дополнительной низкочастотной фильтрации, в него введены элемент

ИЛИ-НЕ, группа элементов HE группа элементов И-НЕ и группа блоков комму тации, каждый из которых содержит элемент 2И-ИЛИ-НЕ,элемент И-НЕ и элемент ИЛИ-НЕ, причем выход элемента

2И-ИЛИ-HE соединен с нервым входом элемента И-НЕ,выход которого подключен к первому входу элемента ИЛИ-НЕ блока коммутации,при этом выходы разрядов регистра подключены к входам соответствующих элементов НЕ группы и первым входам элементов 2И-ИЛИ-НЕ соот. соответствующих блоков коммутации группы, выходы элементов НЕ группы подключены к вторым входам элементов

2И-ИЛИ-НЕ соответствующих блоков коммутации группы, первый и второй входы элемента ИЛИ-HE объединены соответственно с третьим и четвертым входами элементов 2И-ИЛИ-НЕ блоков коммутации группы и являются соответственно входами низкочастотно"

ro н высокочастотного диапазона фильтра, выход элемента ИЛИ-НЕ подключен к вторым входам .элементов ИЛИ-НЕ блоков коммутации группы, вторые входы элементов И-НЕ блоков комм1этации объединены и являются входом начальной установки фильтра, выходы элементов

ИЛИ-НЕ блоков коммутации соединены с первым входом блока памяти, выходы элементов Й-НБ блоков коммутации группы соединены с вторым входом блока памяти, выход которого соединен с первыми входами элементов И-HЕ группы, вторые входы которых объединены и являются стробирующим входом фильтра, выходы элементов И-НЕ группы являются входами фильтра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 632052, кл. Н 03 Н 7/02, 1976.

2. Авторское свидетельство СССР по заявке t) 2631578/18-24, кл. Н 03 Н 7/28 26. 10. 79 (прототип).

997232

Составитель A. Баранов

Корректор В. Прохненко

Редактор М. Товтин

Заказ 958/77 Тираж 934

° ВНИИПИ ГосУдарственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д.4/5

Техред М. Гергель

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4