Преобразователь отраженного двоичного кода в позиционный двоичный код и обратно

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

«»999039 (61) Дополнительное к авт. свид-sy (22) Заявлено 170281 (21) 3270236/18-24 с присоединением заявки №

Р1 М К з

G 06 F 5/02

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 23,0283. Бюллетень ¹ 7 (S3) УДК 681.325 (088.8) Дата опубликования описания 230283

М

Е

Карлюка и A.Н. Голокофос

/ )..

1 (72} Авторы изобретения

I - с.,",". . «ву»

1 it .i;: л<- Fji." t з

A.Ñ. (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ОТРАЖЕННОГО ДВОИЧНОГО КОДА

В ПОЗИЦИОННЫЙ ДВОИЧНЫЙ КОД И ОБРАТНО

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении измерительных систем и управляющих систем.

Известно устройство для преобразования отраженного двоичного кода в позиционный двоичный код, содержащее элементы задержки элементы И ИЛИ 10

И-HE триггеры и.формирователи в ка)кдом разряде (1) .

Недостаток известного устройства состоит в низком быстродействии и невозможности обратного преобразования.

Наиболее близким решением данной задачи по технической сущности и схемному построению является преобразователь двоичного кода в код Грея и обратно, содержащий регистр из триггеров со счетными входами группы, формирователей, элементов И и элементов задержки (2).. Недостаток известного устройства состоит в низком быстродействии, так как преобразование в (n-1) этап, каждый из которых включает в себя сумму времен срабатывания триггера, формирователя, элемента И и времени задерж-. ки сигнала элементом задержки;

Целью изобретения является увеличение быстродействия.

Поставленная цель достигается тем, что в преобразователь отраженного двоичного кода в позиционный двоичный код и обратно, содержащий регистр и первую группу элементов И, первые . входы которых соединены с управляющим входом преобразователя, выходы которого являются выходами регистра, единичный вход n-ro разряда которого соединен с входом старшего разряда преоб" разователя, где n — число разрядов преобразуемого кода введены вторая и третья группы из (n-1)-го элемента И; группа из (n-2) полусумматоров, причем i-й полусумматор (i = 1-: n"1) имеет (i+1) входов и элемент НЕ, вход которого является стробирующим входом преобразователя и соединен с первыми входами элементов И второй группы, вторые входы которых соединены с вхо\. дами соответствующих разрядов преобразователя, а выходы i-ro элемента И второй н третьей групп соответственно — с единичными и счетными входам соответствующих разрядов регистра, первые входы элементов И третьей группы соединены с выходом элемента НЕ, второй вход j -го (j = 1 n "2) эле999039 мента И третьей группы соединен с вы- ходом 1 -го полусумматора группы, первый вход которого соединен с входом (1 +1)-rо разряда преобразователя, второй вход 1 -ro элемента И первой группы соединен с входом (j +2)-го5 разряда .преобразователя, второй вход (п-1)-го элемента И третьей группы соединен с входом n-ro разряда преобразователя и вторым входом (п-2)-го элемента И первой группы, выход- j -Го 10 элемента И первой группы соединен (1 +1) -ми входами с первого по j -ый цолусуммиторов группы.

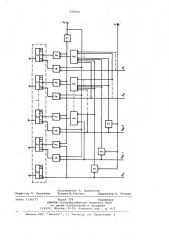

На чертеже приведена блок-схема предлагаемого отраженного двоичного )5 кода в позиционный двоичный код и обратно.

Преобразователь содержит регистр

1, включающий в себя. триггеры 2, пев вую 3, вторую 4 и третью 5 группы элементов И, группу 6 полусумматоров, инвертор 7, стробирующий вход",8, управляющий вход 9 и входы N<- N

Преобразователь отраженного двоичного кода в позиционный двоичный код и обратно работает следующим образом.

В исходном состоянии все триггеры

2 регистра 1 находятся в нулевом состоянии, на информационных входах N

При наличии на входах полусумматоров нечетного числа единиц, на их выхо-. дах появляются единичные .потенциалы.

Для преобразования отраженного двоичного кода в позиционный двоичный код 4 на управляющий вход 9 необходимо по. дать единичный потенциал на все время преобразования. При этом состояние триггеров 2 в регистре 1 изменяется на противоположное. в тех разрядах, по отношению к которым в старших разрядах имеется нечетное количество еди.ниц в исходном коде. Для преобразования позиционного двоичного кода в отраженный двоичный код на управляющий вход 9 необходимо подать нулевой по,.тенциал на все время преобразования, в результате чего на выходах элементов И 3 устанавливаются нулевые потенциалы. При этом состояние триггеров 2 в регистре 1 изменяется на про- о тивоположное в тех разрядах, по от- . ношению к которым в соседнем старшем .разряде имеется единица в исходном коде; Для получения максимального быстродействия преобразователя в слу-Я чае, если время tk срабатывания полусумматора 6 младшего разряда больше времени tz< срабатывания триггера 2, время t1 от момента подачи исходного кода до момента подачи стробирующего потенциала определяется выражением t = t +

1 где tz — время срабатывания элемента И 3.

Время преобразования Тд для этоР го случая определится выражением

Т "Р 1 +"Не + ИБ +"т ° где t — время срабатывания инвертора 7; „ — время срабатывания элемента

И 5.

Для получения максимального быстродействия преобразователя в случае, если время „ > t„, время 1 определяется

И4 тГ

Предположим йеобходимо преобразовать четырехразрядный отраженный дво-, ичный код 1010 (что соответствует в десятичной системе числу двенадцати) в позиционный двоичный код. При поступлении.исходного кода 1010 в стар-. шем и во втором .разрядах регистра.1 . триггеры 2 установятся в единичное состояние, и в регистре будет записан исходный вал. Единичный потенциал, поступивший на вход старшего разряда, вызовет появление на выходе элемента

И 3 единичного потенциала, который, поступив на другой вход полусумматора 6 второго разряда, приведет к ее срабатыванию, так как на первом ее входе присутствует нулевой потенциал со входа Ng. Полусумматор 6 первого разряда не срабатывает, так как на его входах присутствует четное число единиц. Через время й,после подачи исходного кода на стробирующий вход

8 подается нулевой поетнциал, закрывающий элементы, И 4 по первому входу.

Единичный потенциал с выхода инвертора 7, поступая на первые входы элементов И 5, приведет к срабатыванию тех из них, на вторых входах которых присутствует единичный потенциал. В данном случае единичный потенциал с выхода элементов И 5 во втором и третьем разрядах установит триггеры

2 в противоположное состояние, в результате чего в регистре оказывается позиционный двоичный код 1100 (в десятичной системе! — 12).

Следовательно, при преобразовании отраженного двоичного кода в позиционный двоичный код состояние триггеров в регистре изменяется на противоположное в тех разрядах, в которых срабатывает полусумматор при наличии нечетного количества единиц во всех старших по отношению к данному разрядов исходного кода;

Таким образом, при наличии единичного потенциала на управляющем входе

999039 в преобразователе устанавливается .ре.жим преобразования .отраженного двоичного кода в позиционный двоичный код, который предусматривает один этап преобразования, включающий в себя состояние триггеров тех разрядов, по отношению к которым в старших разрядах исходного кода имеется нечетное количество единиц. Быстродействие преобразователя ограничено лишь временем распространения .сигнала на двух элементах И, -полусумматоре, инверторе и времени переключения триггера.

ПредПоложим необходимо преобразовать четырехразрядный позиционный код 1101 (тринадцать) в отраженный tS двоичный код. Так как на первый вход полусумматора б второго разряда поступает единичный сигнал информационного входа N, а на другом его входе нулевой потенциал, то.ца выходе полу- 2() сумматора б появляется единичный потенциал. На выходе полусумматора б первого разряда продолжает оставаться нулевой потенциал, вследствие наличия нулевых потенциалов на его вхо-. 25 дах. Через время t после подачи исходного кода на стробирующий вход 8 подается нулевой потенциал, закрывающий элементы И 4 по первому входу.

Единичный потенциал с выхода инверто- Зо ра 7 приведет к срабатыванию тех элементов И 5, на вторых входах которых присутствует единичный потенциал. В данном случае единичный потенциал с выхода элементов И 5 во втором и 35 третьем разрядах установит триггеры 2

B противоположное состояние, в результате чего в регистре оказывается отраженный двоичный код 1011 (в десятичной системе — 13).

Следовательно, при преобразовании 4О позиционного двоичного кода в отраженный двоичный код состояние триггеров в регистре изменяется в тех разрядах, в которых полусумматор.срабатывает при наличии единицы в соседнем стар- 45 шем разряде исходного кода.

Таким образом, при наличии нулевого потенциала на управлякщем входе в преобразователе устанавливается режим преобразования позиционного двоичного g) кода в отраженный двоичный код, который предусматривает один этап преобразования. !

Конструктивные особенности предлагаемого технического решения позволя55 ют. повысить быстродействие преобразователя, так как преобразование отраженного двоичного кода в позиционный двоичный код происходит в один этап, включающий в себя запись в регистр 60

;.исходного кода и изменения на противоположное состояние триггеров тех разрядов, по отношению к которым в старших разрядах исходного кода имеет ся нечетное количество единиц. Время преобразования, в общем случае, определяется как сумма двух. времен срабатывания элементов И, времени срабаты-. вания полусумматора в младшем разряде, времени срабатывания инвертора и времени переключения триггера.

Предлагаемый преобразователь может быть построен в виде чисто комбинационного устройства, для чего разрядные входы преобразователя должны быть заведены на дополнительные входы полусумматоров. В этом случае необходимость в триггерах и элементах И 5 отпадает, а быстродействие преобразователя увеличивается.

Формула изобретения

Преобразователь отраженного двоичного кода в позиционный двоичный код и обратно, содержащий регистр и первую группу элементов И, первые. входы которых соединены с управляющим входом преобразователя, выходы -которого являются выходами регистра, единичный вход n-ro разряда которого соединен с входом старшего разряда преобразователя, где n — число разрядов преобразуемого кода, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в него введены вторая и третья группы из (n-1)-го элемента И, группа из (n-2) полусумматоров, причем

i-ый полусумматор (i =1 †: n-1) .имеет (i+1) входов и элемент НЕ, вход которого является стробирующим входом преобразователя и соединен с первыми входами элементов И второй группы, вторые входы которых соединены с входами соответствующих разрядов преобра" зователя, а выходы i-ro элемента И второй и третьей групп соответственно - с единичными и счетными входами соответствующих разрядов регистра, первые входы элементов И третьей группы соединены с выходом элемента Е, второй вход j -го (j = 1 -: и -2) элемента И третьей группы соединен с выходом j -го полусумматора группы, . первый вход которого соединен с входом (j +1)-го разряда преобразователя, второй вход j -го элемента И первой группы соецинен с входом ((+2)-го разряда преобразователя, второй вход (n-1)-го элемента И третьей группы соединен с входом n-ro разряда преобразователя и вторым входом (n-2)-го элемента И первой группы, выход j -го элемента И первой группы соединен с () +1)-ми входами с первого по -ый. полусумматоров группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 336699770066,, кклл. Н 03 К 13/24, 08. 11.73.

2. Авторское свидетельство СССР

М 560222, кл. G Об F 5/02, 30 ° 05.77 ,(прототип).

999039

Составитель М. Аршавский

Техред М.Гергель Корректор Л. Бокшан

Редактор Т. Киселева

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1156/71

Филиал ППП Патент, r. ужгород, ул. Проектная, 4