Функциональный преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических респубпин

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву(22)»«>«o 12. 01. 81 (2! ) 3277054/18-24 с присоединением заявки М (23) Приоритет (53)NL. Кл.

G 06 G 7/26

Гасударственный кеаятет

СССР ко елхщ изавРетвккя и етквытий

Опубликовано 23.02.83. Бюллетень М 7 (53) УДК 68>.33 (088. 8) Дата опубликования описания 23.02.83 (72) Авторы изобретения

В. Д . Циделко и А. 3. Булгаков

Киевский ордена Ленина политехнический ин им. 50-летия Великой Октябрьской социалис революции (71 ) Заявитель (54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к информационно-измерительной технике и может быть использовано при построении ана логовых и аналого-цифровых вычислительных устройств.

Известен преобразователь напряжение-частота, содержащий сумматор входных переменных, соединенный последовательно с интегратором,и блок, формирующий импульсы (1 1.

Недостатком этого преобразователя является ограниченный класс воспроизводимых функций.

Наиболее близким к изобретению является функциональный частотный преобразователь, содержащий два интегратора, между входами и выходами каждого из которых включен ключ, выходы .интеграторов подключены к первым входам соответствующих компараторов, выходы компараторов через блок управления подключены к управляющим входам ключей, четыре сумматора, входы которых через соответствующие ключевые элементы сое; динены с источниками входного и опОР» ного напряжений, выходы первого и второго сумматоров подключены соответственно к входам интеграторов, 5 а вторые входы компараторов соединв ны соответственно с выходами третье» го и четвертого сумматоров 1 2).

Недостатком этого преобразова- . ,теля является недостаточно широкий класс воспроизводимых функциональных возможностей.

Цель изобретения - расширение класса решаемых задач.

Поставленная цель достигается тем, что в функциональный преобразователь, содержащий два интегратора, между входом и выходом каждого . из которых включен разрядный ключ,. го Bblxopbl интеграторов подключены к ин" формационным входам соответствующих . компараторов, управляющие входы ко". торых подключены к выходам соответствующих сумматоров опорных величин,, $

3 9 входы которых подключены к соответствующей группе входов опорных величин преобразователя, первый и второй сумматоры входных переменных, входами подключенные к соответствующей группе входов входных переменных преобразователя, введены и-1 интеграторов, где и-число входных переменных, триггер, п-1 компараторов, и-2 разрядных ключей, л+1 управляющих ключей, и-1 сумматоров опорных величин и п-1 сумматоров входных переменных, причем выход n+1-го сумматора входных переменных соединен с первым входом 0 +1-го интегратора, второй вход которого соединен с выходом n+1-ro управляющего ключа, уп.равляющий вход которого соединей с первым выходом триггера, первый вход которого соединен с выходом и+1-го компаратора, являющимся выходом пре.-. образователя,управляющий вход n+1-ro компаратора подключен к шине уровня ограничения преобразователя, второй выход триггера подключен к первому управляющему входу первого разрядного ключа, выходы и-2-х разрядных ключей соединены соответственно .с выходами п-2-х интеграторов, выходы i-x (i

1,2 „,.n) компараторов соединены со вторыми управляющими входами i-x разрядных ключей и первыми управляющими входами К-х (К=1,2, n+1) управляющих ключей, вторые управляющие входы которых подключены соответственно к первым управляющим входам I-x разрядных ключей, подключены соответственно к выходам К-х сумматоров входных переменных и n+1-ro сумматора опорных величин, выходы

j-x компараторов (j=1,2,...n-1) подключены соответственно к первым управляющим входам последующих j+1-х разрядных ключей, а выход и-го компаратора соединен со вторым входом триггера, выходы Ьх интеграторов ((3,4,...п+1) соединены соответственно со входами f-x компараторов, а выходы К-х управляющих ключей соединены соответственно со входами К-х интегоатооов.

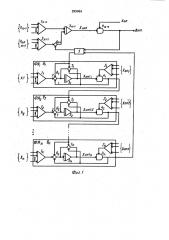

На фиг. 1 представлена структур» ная схема функционального преобразователя (ФП), на фиг.2 - временные диаграммы его работы.

Функциональный преобразователь (Фиг.1 ) содержит.,сумматоры 11- 1

9906,9 4 входных переменных, сумматоры 2 -2 . ий опорных величин, интеграторы 3 -

1 иН компараторы 4 -41, триггер 5, уп- равляющие ключи 6 -6, разрядные ключи 7, -7, функциональные ячейки 1 ВИ . функциональный преобразователь работает следующим образом.(фиг.2).

Если в исходный момент времени на первый вход интегратора 3и+g ерез сумматор входных переменных 1 поИ 1 даются. входные переменные Хи, то происходит их интегрирование в прямом направлении до уровня ограничения ХО4(иг.2а) компаратора 4И+,котарый, срабатывая, переключает триггер 5. Сигналом первого выхода триггера 5 открывается управляющий ключ би+, сигналом второго выхода открыщ вается ключ 64 и закрывается разрядный ключ 7 первой функциональной ячейки ФЯ . При этом, на второй вход интегратора 3И+4 через ключ 6И+А с выхода сумматора 2и подаются опорные еевеличины Хои, чем обуславливается инин тегрирование в обратном направлении .в течение времени to, которое определяется последовательным интегрированием входных переменных Х, З0 Х ...Х И соответствующих функциональных ячеек ФЯ, ФЯ ....ФЯ „. В резульЯ . тате равенства зарядов накопительно-го элемента интегратора 3и < при пряИ+1 мом и обратном интегрировании. можно

Хи+4 t„=- Хоо 10 (1) где t>- период следования выходных им импульсов.

Откуда, выходная частота F ÔÏ опре40 деляется выражением

Хюл4

1 2) х она +о

Временной интервал t начинается в мо.мент срабатывания ключей 6„, 7, ФЯ

4$ и подключения входных переменных Х через сумматор 11 ко входу интегратора 3А . На выходе интегратора 3 величина Х т изменяется по линейному закону (фиг.?б) до опорной переменной величины Х компаратора 4, подавае lip 1 мой с выхода сумматора 2, который закрывает ключ 6 и открывает ключ

7 ФЯ, а в ФЯq закрывает ключ 7, открывает. ключ 6 . 3 этот момент сбрасывается в исходное состояние интегратор 3 фЯ<, переключается в режим прямого интегрирования интегратор

3 ФЯ (фиг.2в), заканчивает я временной интервал t, начинается t<. Работа последующих функциональных ячеек происходит аналогичным образом в соответствии с временными диаграм мами фиг.2. Временной интервал t за- 5 канчивается- в момент срабатывания компаратора 411ФЯ11, которЫй переключает триггер 5, закрывающий ключ 6« л,обеспечивая повторение цикла преобразое вания (интегрирования в прямом направлении).

При этом временной интервал и можно представить в виде . ал ta. ° ty,1 Х (3)

15 1, „. 1 - посточнйые времан« интеграторог 3л — 3и функциональных ячеек ФЛл, фя „....фЯ„(8л- 8„).

Учитывая (3) и (4) выражение (2) принимает вид

1 Г ) f Xceq Xanz Хощ,, (5)

- ОК11+„ Х,1 Х + Х« где с -г«„=- =... -„ 25

Наличие сумматоров на входах ин-. теграторов и компараторов позволяет наращивать число пе,временных, входящих в выражение (9 }.

Рассмотренная структура функционального преобразователя обеспечивает выполнение дополнительных операций умножения, деления и увеличения числа переменных величин с помощью последовательно включенных однотипных функциональных ячеек, построенных на аналоговых микросхемах средней степени интеграции меньшей стоимости по сравнению с аналоговыми схемами, формирующими те же функции.

Технико-экономический эффект от применения предлагаемого преобразователя состоит в уменьшении количест. ва дорогостоящего оборудования при построении преобразователей, выполняющих широкий класс множитель«о-деiS лительных операций.

Формула изобретения функциональный преобразователь, содержащий два интегратора, между

50 входом и выходом каждого из которых включен разрядный ключ, выходы интеграторов подключены к информационным входам соответствующих компараторов, управляющие входы которых подключены к выходам соответствующих 55 сумматоров опорных величин, входы которых подключены к. соответствующей группе входов опорных величин преоб 5 999069 и разователя, первый и второй сумма" тори входных переменных, входами подключенные к соответствующей группе входов входных переменных преобразователя, о т л.и ч а ю-шийся тем, что, с целью расширения класса решаемых задач, в него введены и-1 интеграторов, где а-число входных г.еременных, триггер, и- 1 .компарато

poe, n-2 разрядных ключей, И +1 управляющих ключей, и-1 сумматоров опор» ных величин « и-1 сумматоров вход,ых переменных, причем выход и+1"го сумматора входных переменных соединен с первым входом и+1-го интегратора, второй вход которого соединен с выходом и- 1-го управляющего ключа, управляющий вход которого -оединен с первым выходом триггера, первый вход которого соединен с выходом и+1-го компаратора, являющимся вы" ходом преобразователя, управляющий вход и+1-го компаратора подклю ен к шине уровня ограничения преобразова- . теля, второй выход триггера подключен к первому управляющему входу первого разрядного ключа, выходы и-2-х разрядных ключей соединены соответственно с выходами и-2-х интеграторов, выходы i-х (1=1, 2,...n) компараторов соединены со вторыми управляющими входами «-х разрядных ключей и первыми управляющими входами К-х (К=1, 2, ... n+1) управля" ющих ключей, вторые управляющие вхо. ды которых подключены соответственн< к первым управляющим входам i-х раз. рядных ключей, информационные входы

К-х управляющих ключей подключены соответственно к выходам К-х сумматоров входных переменных и n+1-го сумматора опорных величин, выходы

j-x компараторов (j= 1,2,...n-1) под" ключены,соответственно к первым управляющим входам последующих j+1"х разрядных ключей, а выход n-ro компаратора соединен со вторым входом триггера выходы с-х интеграторовf Ь3,4,...n+1) . соединены соответственно со входами

Ьх компараторов, а выходы К-х управ" ляющих ключей соединены соответственно со входам К-х интеграторов.

Источники информации, принятые во внимание при экспертизе

1. Патент СНА 1Г 3040273,, кл. 33214, опублик. 1962.

2. Авторское свидетельство СССР

N 809241 кл.G 06 r 7Л6, 1979 (прототип).

999069

Хват .

Хо, Хиит

Хоп1

Минт

)(one

Минт

Хоаи

Составитель В.смирнова

Редактор Л. Филиппова ТехредМ.Гергель Корректор И. Ватрушкина . Заказ 1158/73 . Тираж 704. Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4