Федюнин Роман Николаевич (RU)

Изобретатель Федюнин Роман Николаевич (RU) является автором следующих патентов:

Ячейка однородной вычислительной среды

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих функцию счетчика, с представлением результата в унитарном или двоичном коде и для применения в устройстве для сжатия двоичных векторов. Техническим результатом является повышение функциональных возможностей ячейки за счет введения операции подсчета числа единиц с...

2284568

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих арифметическое сложение двоичных векторов, упорядоченное хранение и трансляцию информации при массовой параллельной обработке данных. Техническим результатом является повышение функциональных возможностей ячейки за счет реализации операции арифметического сложения...

2285285

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных. Техническим результатом является расширение функциональных возможностей устройства за счет реализации операции хранения и обработки информации в непозиционной системе счисления. Устройство содержит семь эл...

2295147

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных. Техническим результатом является расширение функциональных возможностей устройства за счет реализации операции хранения и обработки информации в непозиционной системе счисления. Устройство содержит шесть э...

2300800

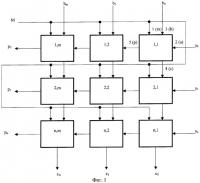

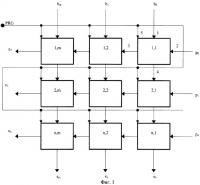

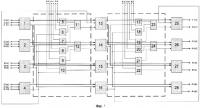

Однородная вычислительная структура для выполнения операций по заданному модулю

Изобретение относится к вычислительной технике и может быть использовано для выполнения арифметических операций над числами, представленными в непозиционной модулярной системе счисления. Техническим результатом является повышение функциональных возможностей устройства. Устройство содержит N2 полных сумматоров, элементов И, где K=N-1, (N-2)(N-1) элементов ИЛИ, управляющих входов. 3 ил.

2310223