Интегральная логическая схема

Иллюстрации

Показать всеРеферат

(72) Авторы изобретеиия

Ю.Н.Еремин, А.С.Федонин и И.B. (71) Заявитель (54) ИНТЕГРАЛЬНАЯ ЛОГИЧЕСКАЯ СХЕМА

Изобретение относится к микроэлект- . ронике и может быть использовано в вычислительной технике и в системах дискретной автоматики.

Известен инвертор,. в котором повы5 шение быстродействия обусловлено тем, что крутизна фронтов выходного импульса сохраняется, а амплитуда перепада уменьшается за счет введения цепи, состоящей из нескольких диодов и о транзистора $ 1 j .—

Недостатком укаэанного инвертора является повышенное потребление мощности от источника питания в состоянии логической "1" и пониженное зна- )s чение выходного напряжения логической и1!1.

Известен также ТТЛ элемент, содержащий входной многоэмиттерный транзистор, двухэмиттерный фаэораэделительный и выходной транзисторы, резисторы и ускоряющую цепь. База многоэмиттерного и коллектор фазоразделительного транзисторов соединены чв" рез резисторы с шиной питания, коллектор первого упомянутого транзистора соединен с базой второго. Один эмиттер фаэовращательного транзистора соединен с базой выходного транзистора и через резистор с общей шиной, второй эмиттер соединен с коллектором выходного транзистора с ускоряющейся цепью и выходом элемента (2 .

Недостатком известного элемента является то, что через транзистор ускоряющеч цепи при включении выходного транзистора протекают существен ные импульсные токи, в то же время величина. базового тока упомянутого транзистора ограничена резистором, включенным между коллектором фазораэделительного транзистора и шиной питания, величину которого нельзя уменьшать, так как зто приводит к росту потребляемой мощности, указанные обстоятельства приводят к увели-, 3 10014 чению времени включения выходного транзистора и росту потребляемой мощности при повышении частоты переключения (за счет развития бросков импульсных токов), а такжв ограничению нагрузочной способности в состоянии логического "0".

Цель изобретения - уменьшение по.требляемой мощности и увеличение быстродействующей нагрузочной способ- 1© ности.

Поставленная цель достигается тем, что в интегральную логическую схему, содержащую входной многоэмиттерный транзистор,,база которого через резистор соединена с шиной питания, коллектор - с базой фазораэделительного транзистора, коллектор которого через резистор соединен с шиной питания и базой транзистора ускоряющей це-рв пи, коллектор которого через резистор соединен с шиной питания, эмиттер через диод - с коллектором выходного транзистора и выходом> эмиттер выходного транзистора соединен с общей ши- 25 ной, введен дополнительный транзистор> коплектор которого соединен с шиной питания, база — с эмиттером фазоразделительного транзистора, через дополнительный диод - с коллектором выходного зв транзистора и через последовательно соединенные диод и резистор — с общей шиной, эмиттер дополнительного транзистора соединен через соответствующио. резисторы с общей шиной и базой выходного транзистора, при этом коллектор выходного многоэмиттерного транзистора подключен к его базе.

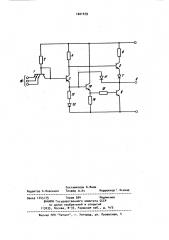

На чертеже изображена схема устройства.

Устройство содержит входной многоэмиттерный транзистор 1, база которого подключена к источнику питания через резистор 2 и фазоразделительный транзистор 3, коллектор которого через резистор 4 подключен к источнику питания. База транзистора 3 соединена с коллектором и базой транзисто-, ра 1. В схеме имеется ускоряющая цепь, состоящая из транзистора 5, ба- о за которого соединена с коллектором транзистора 3, коллектор через резистор б - с источником питания, а эмиттер - с анодом диода 7, катод которого соединен с выходом 8 и коллектором выходного транзистора 9, эмиттер транзистора 9 подключен к общей шине питания, коллектор дополнительного тран"

9 ф зистора 10 соединен с источником питания, база — с эмиттером транзистора

3, с анодом дополнительного диода 11, катод которого подключен к выходу 8, и с резистором 12, второй конец которого подключен к аноду диода 13, катод которого соединен .с общей шиной, эмиттер транзистора 10 соединен с резисторами 14 и 15, вторые концы которых соединены соответственно с общей шиной питания и базой транзистора 9. Эмиттеры транзистора 1 подключены к вхюду устройства.

Предлагаемое устройство работает следующим образом.

Если на часть входов 16 (или на все) подан низкий уровень напряжения, фазоразделительный транзистор 3 закрыт, следовательно, закрыт и выходной транзистор 9, так как в базу его не втекает ток, и на выходе 8 схемы— высокий уровень напряжения.

Если на все входы 16 подать высокий уровень напряжения, фазоразделительный транзистор 3 откроется и через него потечет ток, который разветвится: часть потечет в цепь,,состоящую из резистора 12 и диода 13, а часть — в базу транзистора 10, включенного по схеме эмиттерного повторителя. При этом в базу транзистора 9 задается избыточный ток, обеспечивающий его быстрое включение, причем величина этого избыточного тока может быть весьма значительной и ограничивается, практически, лишь резистором 1, сопротивление которого выполняется небольшой величины.

В начальный момент времени, когда транзистор 9 еще не включился, ток через диод 11 протекать не может и падение напряжейия на резисторах 4 и 12 примерно равны. Напряжение на базе транзистора 5 быстро снижается, что также способствует более быстрому включению выходного транзистора 9.

Как только включится выходной транзистор 9, и на его коллекторе напряжение станет равным. падению напряжения на прямосмещенном р-п-переходе, через диод 11 начинает протекать ток, ответвляющий часть тока из базы дополнительного транзистора 10 в кол" лекторную часть выходного транзистора 9.

Таким образом, через транзистор

10 протекает ток, необходимый лишь для.создания на резисторе 14 падения

5 1001 напряжения, равного прямому падению напряжения на база-эмиттерном переходе выходного транзистора 9 и базовый ток транзистора 9.

При этом уменьшается базовый ток з транзистора 10 и его величина определяется коэффициентом усиления транзистора 9, а весь избыточный ток протекает через диод 11 в коллектор . транзистора 9. о

Таким образом, обеспечивается ограничение степени насыщения выходного транзистора 9, снижение потребляемой мощности, так как резистор 4может в этом случае быть сравнительно 1 большой величины, поскольку не он определяет величину базового тока транзистора 9,, а также повышение нагрузочной способности схемы в состоянии логического "0", так как при увели- 20 чении тока нагрузки часть тока, про-. текающего через диод 11, перераспределяется в базу дополнительного транзистора 10 и вызывает увеличение базового тока транзистора 9.

Если теперь на части входов 16 (или на всех) вновь создать низкий уровень напряжения, транзистор 3 вы. ключается, при этом прекращается ток в базу выходного транзистора, а так как отсутствует избыточный базовый ток, выходной транзистор 9 быстро выключается. При этом будет существенно меньшим и бросок тока при выключении схемы через форсирующую цепь. Ç5 формула изобретения

Интегральная логическая схема, содержащая входной многоэмиттерный

479 6 транзистор, база которого через. резистор соединена с шиной питания, коллектор - с базой фазоразделительно о транзистора, коллектор которого через резистор соединен с шиной питания и базой транзистора ускоряющей цепи, коллектор которого через резистор соединен с шиной питания, эмиттер через диод - с коллектором выходного тран" зистора и выходом, эмиттер выходного транзистора соединен с общей шиной, отличающаяся тем, что, с целью уменьшения потребляемой мощности, увеличения быстродействия и нагрузочной способности, введен дополнительный транзистор, коллектор которого соединен с шиной питания, база - с эмиттером фазоразделительного транзис тора, через дополнительный диод - с коллектором выходного транзистора и через последовательно соединенные диод и резистор — с общей шиной, эмиттер дополнительного транзистора соединен через соответствующие резисторы с общей шиной и базой выходного транзистора, при этом коллектор входного мно" гоэмиттерного транзистора подключен к его базе.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР 305587, кл, H 03 K 19/00, 1976.2. Шагурин И.И. Транзисторно-транзисторные логические схемы. И., "Советское радио", 1974, с.96, рис. 3, 4а (прототип).

1001479.

Составитель А.Янов

Редактор А.Власенко Техред А.Ач Корректор,ßåêèàð

Заказ 1445/75 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раумская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проевтная, 4