Многофункциональный логический элемент

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Colo 3 Советскин

Социалистических

Республик (11)1 005313

{6l ) Дополнительное к авт. свид-ву (22) Заявлено 10.08.81 (2l ) 3325202/18;71 с присоединением заявки J4 (23) П риоритет

Опубликовано 15.03,83. Бюллетень М 10

Дата опубликования описания 15.03.83 (51)M. Кл.

Н 03 К 19/01

Гвсудерстеееа1 квинтет

СССР (53) УДК621. .374(088.8) 60 делен изевретеннй и открытий

Ю. М. Герасимов, А. Н. Кармазинский, В. П. Нарейко, ЮЛ. Яьячеюю и А. И. Соловьев

° »

»»

Московский ордене Трудового Красного Знам и - - -"" - -. .А инженерно-физический институт (72) Авторы изобретения (7i) Заявитель (54) МНОГОФУНКЦИОНАЛЬНЪЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к вычислительной технике, электронике и, в частности, может быть использовано при разработке

БИС на дополнительных МЙП транзисторах»

Известен многофункциональный логический элемент, существенным признаком которого является использование ступенчатого включения логических элементов на дополняющих МДП транзисторах f1 ).

Недостачами этого элемента являются низкое быстродействие и искажение логических уровней при большом числе погичесвих элементов со ступенчатым вклю- чением. t5

Известен многофункциональный коньюнк-. тивно-инверсный логический элемент, содержащий многовходовые элементы, выполняютцие произвольные заданные логические функции, первый из которых вклю» 2 чен между шиной питания и общей шиной, а каждый последукеций одним выводом подключен к шине питании, а другим - к выходу предыдущего многовходового логического элемента, и управляемые элементы восстановления уровня напряжения логической единицы, у которых. один вывод подключен к шине питания, второйк выходу соответствующего многовхо дового логического элемента, начинаи со второго, а вывод управления через инвертор — к выходу предыдущего многовхо дового логического элемента 1 2 $

Недостатком устройства является низкое быстродействие из-за перезаряда выходных емкостей через большое число поспедовательно включенных МЙП транзисторов тт гипа между выходом каждого многовходового логического элемента и обшей шиной.

Цепью изобретения является повышение быстродействия.

Для достижения поставленной цели s многофункциональный логический элеаеент, содержащий многовходовые логические элементы, выполняющие произвольные заданные логические функции, первый из которых включен между шиной вкодового логического элемента равен инверсии от срответствуюшей функции, т. е. ра

° ° вен F <), F °,, Г .), соответственно.

Если обозначить функции, выполняемые на выходах многофункционального., логического элемента, соответственно, D(p} Ъ) ",D(;),то легко показать ч справедлива следующая рекуррентнвя формула:

1 о)= (о)

g . р. „Р.;где =$2„-, так ad F o), F „), F< >), -., Ft;) любые заданные функции, то возможно реализовать. широкий спектр выходных функций много функционального логического элемента.

Элементы 6-8 восстановления уровня напряжения логической единицы подключают выход каждого последующего многовходового алемента к шине питания в момент, когда на выходе предыдущего элемента устанавливается уровень напряжения логического нуля. Это обеспечивает установление уровня напряжения логичес кой единицы на выходе последуюшего элемента. В качестве элемента восстановления уров ня напряжения логической единипы может использоваться, например, р-канальный транзистор.

Установка уровня напряжения логической единицы на выходе многовходового логического элемента 2 осуществляется или через группу р-канальных транзисторов этого элемента, или через элемент 6 восстановления уровня напряжения логической единицы, а установка уровня напряжения логического нуля осуществляется при разряде паразитной емкости через группу и -канальных транзисторов атого алемен та и через и -канальный транзистор инвертора.

Быстродействие многофункционального логического элемента увеличивается, так как с ростом функциональной сложности длина цепи разряда емкости на любом выходе многовходового логического алемента определяется группой П -канальных транзисторов алемента и предыдущего инвертора, в отличие от известного устройства, где с ростом числа ступеней увеличивается длина цепи разряда емкости и, следовательно, уменьшается быстродействие.

Многофункциональный логический эле мент, содержащий многовходовые логичес3 1005313 ф питания и общей шиной, в каждый последующий одним выводом подключен к шине питания, и управляемые элементы восстановления уровня напряжения логической единицы, у которых 5 один вывод подключен к шине питания, а второй — к выходу соответствующего многовходового логического элемента, начиная со второго, введены разделитель ные инверторы, у каждого иэ которых 10 выход подключен ко второму выводу соответствующего многовходового логического элемента, начиная со второго, а вход— к выходу предыдущего многовходового логического элемента и к выводу управления элемента восстановления уровня напряжения логической единицы последующего многовходового логического Ылементв.

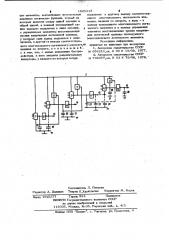

На чертеже представлена электрическая принципиальная схема многоЬункционального логического элемента.

Схема содержит многовходовые логи, ческие эл.менты 1-4, которые подключены

Одним выводом к шине питания 5, Уцр&вляе!мые элементы восстановления уровня напря-д жения логической единицы 6, 7 и 8 одним выводом подключены также к шййе питания 5, а другим — к выходу соответствуюшего многовходового логического элемента, начиная со второго, а именно, к выходу элементов 2, 3 и 4, Вывод управления элементов 6, 7 и 8 подключен, соот-. ветственно, к выходу элементов 1, 2 и

3. Входы дополнительно введенных разделительных инверторов 9-12 подключены, соответственно, к выходам элементов

1-4 и к выводам управления элементов

6, 7 и 8, а выходы инверторов 9-12, которые одновременно являются выходами многофункционального логического элемента 13-16, подключены, соответствен40 но, ко второму выводу элементов 2, 3 и

4. Второй вывод элемента 1 подключен к общей шине 17, Емкости,нагрузки с учетом парвзитных емкостей представлены конденсаторами 18-26, подключенными между входом разделительных инверторов

9-12 и общей шиной 17 и между выходом этих инверторов и общей шиной 17.

Устройство работает следукхцим образом. 50, Ffa выходе многовходовых логических элементов, если они включены между шиной питания H об пей IQHHQN выполняются

),О) ° (1) -" (1) иэ этих функций может быть любой зв- ф

Формула изобретения данной функцией от любого числа логических переменных )(, )(, „„Х ° . Зкви валентный входной сигнал каждого многоS 1005313 4 кие элементы, выполняющие произвольные подключен к другому выводу соответствузаданные логические функции, ncрвый из юшего многовходовогс логического влекоторых включен между шиной питании и мента, начиная со второго, а вход - к обшей шиной, а каждый последуккпий од-.. выходу предыдущего многовходового логи» ним выводом подключен к шине питания, g ческого элемента и к выводу управления к управляемые элементы восстановления элемента восстановления уровня напряавуровня напряжения логической единицы. сия логической единицы последукк его у которых один вывод подключен к шине многовходового логического элемента. питания, а другой-к выходу соответствую- Источники информации, щего многовходового логическо .о элемента 14 принятые во внимание при экспертизе начиная со второго, о т л и ч а ю m и " - 1. Авторское свидетельство СССР с я тем, что, с пелью повышения быстро- % 6562l3,êë. Н 03 К 19/08, 1977. действия, в него введены разделительные 2. Авторское свидетельство СССР инверторы, у каждого из которых выхрд N 736377 кл. Н 03 К 19/08, 1978.

Составитель Л. Петрова

Редактор А. Йолинич Техред.E.баритончик Корректор М. Коста

Заказ 1925/77 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4