Устройство для выборки информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫБОРКИ ИН;ФОРМАЦИИ , содержащее первый, второй, третий и четвертый МДП-тран зисторы, причем стоки первого и второ го ключевых транзисторов являютсй первым и вторым выходами устройства, соответственно, стоки третьего и iчетвертого ключевых транзисторов являются разрядными выходами устройства , затворы третьего и четвертого ключевых транзисторов объединены и являются адресным входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства , исток третьего ключевого транзистора соединен со стоком первого транзистора, исток четвертого ключевого транзистора соединен со стоком второго ключевого транзистора , истоки первогои второго ключевых транзисторов соединены с адресным входом устройства, затворы первого ж второго ключевых транзисторов являются первым и вторым входом записи устройства. ч .

ССЮЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„10 i 4029

y G 11 С 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОВРЕТЕНИЙ И OTHPbfTHA

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

K . .АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

Ю 3 (2 1) 3364075/18-24 (22) 15.12,81

° °

46) 23.04.83. бюл. F. 15

72) В.В.баранов, Р.М;Герасимов, ,Н.Г.Григорьев, А.Н.Кармазинский, . П.б.Поплевин и Э.rl.càâîñòüÿíîs (53) 681. 327.6(088.8) : (56) 1.Патент ClllA Н 4131951, кл. 365-203, опублик. 1978.

2. Патент США И 4103345, кл. 365-190, .опублик. 1978. .3 ° lEEE 1. of Solid-State С1rcults, 1981, v. SC-16, 11 5, р.р.460-46 (прототип).

44) f57) УСТРОЙСТВО ДЛЯ ВцбОРКИ ИН, ФОРМАЦИИ, содержащее первый, второй, третий и четвертый ключевые МДП-тран зисторы, причем стоки первого и второго ключевых транзисторов являютсй первым и вторым выходами устройства, соответственно, стоки третьего и четвертого. ключевых транзисторов являются разрядными выходами устройства, затворы третьего и четвертого .ключевых транзисторов объединены и являются адресным входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, исток третьего ключевого транзистора соединен со стоком первого транзистора, исток четвертого ключевого транзистора соединен со

1стоком второго ключевого транзистора,истоки первогои второгоключевых транзисторов соединены с адресным, входом устройства, затворы первого и второго ключевых транзисторов являются первым и вторым входом записи устройства.

1 10140

Изобретение относится к вычисли- тельной технике и может быть использовано при построении микромощных интегральных запоминающих устройств на дополняющих МДП-транзисторах.

Известны устройства для выборки

I информации для оперативного запомина" ющего устройства (ОЗУ ) на дополняющих МДП-транзисторах, содержащие два ключевых транзистора, две выходные 10 и две разрядные шины, а также адресную шину, причем стоки ключевых транзисторов соединены с внешними разрядными шинами, истоки — с внутренними разрядными шийами (! "!или шиной питания через дополнительные транзисторы (2 1.

О

Недостатком этих устройств является низкое быстродействие.

Наиболее близким к изобретению по 20 технической сущности является устройство для выборки информации для ОЗУ на дополняющих МДП-транзисторах, содержащее два транзистора записи, два ключевых транзистора, два выходных 25 транзистора и две разрядные шины, две шины записи и адресную шину 3 1, Недостатком известного устройства является низкое быстродействие, обусловленное задержкой сигнала

30 считывания на транзисторе, включенном между ключевым транзистором и разрядной шиной.

Цель изобретения — повышение быстродействия устройства для выборки информации для ОЗУ на дополняющих МДП-транзисторах.

Поставленная цель достигается тем, что в устройстве для выборки информации, содержащем первый, второй, третии и четвертыи ключевые МДП-транч v

40 зисторы, причем стоки первого и второго ключевых транзисторов являются первым и вторым выходами устройства, соответственно, стоки третьего и четвертого ключевых транзисторов являются разрядными выходами устройства, затворы третьего и четвертого ключевых транзисторов объединены и являются адресным входом устройства, исток третьего ключевого транзистора соединен со стоком .первого ключевого транзистора, исток четвертого ключевого транзистора со стоком второго ключевого транзистора, истоки первого и второго ключевых транзисторов соединены с адресным входом устройства, затворы первого и второго ключевых транзисторов являютмя первым и вторым входом записи устройства.

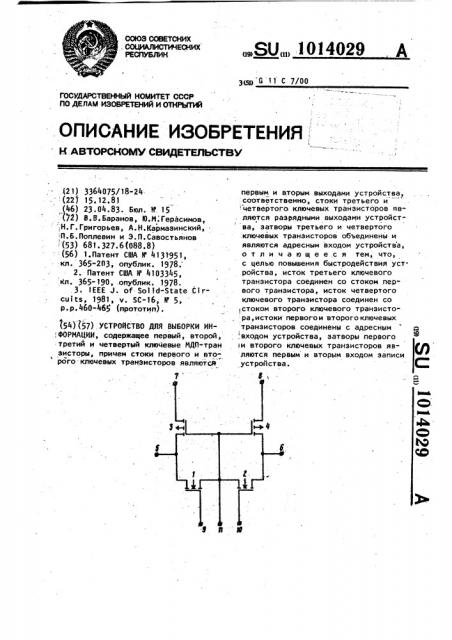

На чертеже представлена принципиальная электрическая схема предлагаемого устройства.

Устройство содержит первый 1 и второй 2 ключевые транзисторы первого типа проводимости, третий 3 и четвертый 4 ключевые транзисторы второго типа проводимости, первый 5 и второй

6 выходы устройства, разрядные выходы 7 и 8, первый 9 и второй 1О входы и адресный вход 11.

Устройство для выборки информации для ОЗУ на дополняющих МДП-транзисторах работает следующим образом.

В режиме записи к адресному входу

11 и одному из входов записи, например 10, приложен сигнал логического нуля, а к входу 9 записи - сигнал логической единицы. При этом транзисторы 3 и 4 открыты по затвору, транзйстор 2 закрыт, а транзистор 1 открыт, разряжая выход устройства

5 до уровня логического нуля. Таким образом обеспечивается запись логического нуля. Запись логической единицы обеспечивается подачей сигнала логического нуля на адресный вход 11 и вход 9 записи и подачей сигнала логической единицы на вход 10 записи.

При считывании информации на адресный вход 11 и входы 9 и 10 записи подается сигнал логического нуля.

Транзисторы 1 и 2 при этом закрыты, а транзисторы 3 и 4 открыты, обеспечивая прохождение сигнала считывания с выходов устройства 5 и 6 на разрядные входы 7 и 8 °

8 устройстве для выборки информации повышение быстродействия достигается исключением ключевых транзисторов из тракта записи, подключением транзисторов 1 и 2 непосредственно к выходам устройства.

Исключение ключевых транзисторов из тракта записи позволяет увеличить уровень полезного сигнала на выходах устройства за счет устранения потерь на пвразитных сопротивлениях и емкостях разрядных шин (особенно важно для интегральных микросхем запоминающих устройств с большой информационной емкостью ) и последовательно включенных ключевых транзисторах. При этом условия записи легко могут быть обеспечены соответствующим выбором размеров транзисторов записи и транзисторов выходного каскада дешифратора

З 1014029 4 столбцов. Сведение к минимуму влияния максимальным конструктивным приблипаразитных сопротивления и емкостей . жением трачзисторов записи к запомивнутренних разрядных шин достигается нающим элементам.

Составитель Г. Бородин

Редактор Г. Безвершенко Техред Л. Пекарь Корректор О. Билак

Заказ 3026/61 Тираж 592 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Рауаская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4