Параллельный дешифратор

Иллюстрации

Показать всеРеферат

ПАРАЛЛЕЛЬНЕОЙ ДЕШИФРАТОР, {Содержащий квазистатический эле1мент ИЛИ-НЕ, iвыход которого соединен с первым входом элемента И-НЕ, ВЫХОД которого соединен с первым управляющим входомэлёмец а ИЛИ-НЕ и является выходой дешифратору второй управляющий вход элемента ИЛИ-НЕ является управляющим входом дешифратора, информационные входы элемента ИЛИ-НЕ являются ингформационными входами дешифратора, отличающийся тем, что с целью повышения быстродействия, он содержит первый и второй инверторы , причем вход первого инвертора соединен с вторвм управляющим входом элемента ИЛИ-НЕ, третий . управляющий вход которого соединен с выходом первого инвертора и вхо-. дом второго инвертора, выход которрго соединен с вторым входом (П элемента И-НЕ.

(19) (Н) COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(59 G 11 С 8 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3362776/18-24 (22) 09.12.81 (46) 23.04.83. Бюл. 9 15 (72) В.В.Баранов, (O.М.Герасимов, Н.Г.Григорьев, A.Н.Кармазинский, П.Б.Поплевин и Э.П.Савостьянов (53) 621.327.6(088.8) (56) 1. Патент С)Ш Р 4048629, кл. 340-173, опублик. 1977.

2. Патент СШа Р 3679911, .кл. 307-251, опублик. 1972. . 3, Авторское свидетельство СССР

9 798997 кл. G ll С 8/00 28.12.78 (прототип). (54) (57) ruu A)U1E)11 H é ПЕШИфР) СР, содержащий квазистатический элеент ИЛИ-НЕ,;выход которого соединен с первым входом элемента

И-НЕ, выход которого соединен с первым управляющим входом элемента

ИЛИ-НЕ и является выходом дешифратора, второй управляющий вход элемента

ИЛИ-НЕ является управляющим входом дешифратора, информационные входы элемента ИЛИ-НЕ являются ин.— формационными входами дешифратора, отличающийся тем, что с целью повышения быстродействия, он содержит первый и второй инверторы, причем вход первого инвертора соединен с вторым управляющим входом элемента ИЛИ-НЕ, третий . управляющий вход которого соединен с выходом первого инвертора и вхо-. дом второго инвертора выход коf е торого соединен с вторым входом элемента И-НЕ.

1014030

65

Изобретение относится к . вычислительной технике и электронике и может быть использовано при построении микромощных интегральных запоминающих устройств (ЗУ), на дополняющих МДП-транзисторах.

Известны ячейки для построения параллельного дешифратора на одноканальных МДП-транзисторах статического и динамического типа, представляющие собой логические элементы ИЛИ-НЕ или И-НЕ, состоящие из параллелъной группы транзисторов и нагрузочного транзистора, на отношение размеров которых наложено ограничение (11и(2). 35

Однако дешифраторы построенные, на основе таких ячеек, потребляют. значительную мощность в статическом режиме и непригодны для ЗУ на дополняющих МДП-транзисторах.

Наиболее близкой к изобретению является ячейка параллельного дешифратора, содержащая квазистатический логический элемент ИЛИНЕ (И-HE) с информационными и управляющими входами, логический элемент И .с задержкой, в которой выход квазистатического элемента

ИЛИ-НЕ подключен к первому входу элемента И-НЕ, а его первый управ,ляющий вход - к выходу элемента

,И-НЕ, второй управляющий вход соединей с вторым входом элемента И, .и с задержкой подключен к второй. шине управления, первый выход.логического элемента И с задержкой 35 подключен к первой шине управления, а выход этого элемента - к второму входу логического элемента

И-НЕ. На шины питания всех элементов ячейки подаются постоянные 40 потенциалы (31.

Недостатком известной ячейки параллельного дешифратора являет ся наличие ограничений на фазовые соотношения между сигналами на управляющих входах, а так- . ,же на величину задержки сигнала И, в. результате чего снижается быстро-, . действие дешифратора и процент выхода годных. Кроме того, известная схема параллельного дешифратора критична к разбросу параметров транзисторов, в результате чего она имеет. небольшой диапазон работоспособности при воздействии различных дестабилизирующих факторов °

Цель изобретения — повышение быстродействия.

Поставленная цель достигается там, что в параллельный дешифратор, содержащий квазистатический эле« 60 мент ИЛИ-НЕ, выход которого соединен .с первым управляющим входом элемента ИЛИ-НЕ и является выходом .дешифратора, второй управляющий вход элемента ИЛИ-НЕ является управляющим входом дешифратора, информационные входы элемента ЙЛИ-, НЕ являются информационными входами дешифратора, введены первый и второй инверторы, причем вход первого инвертора соединен с вторым управляющим входом элемента

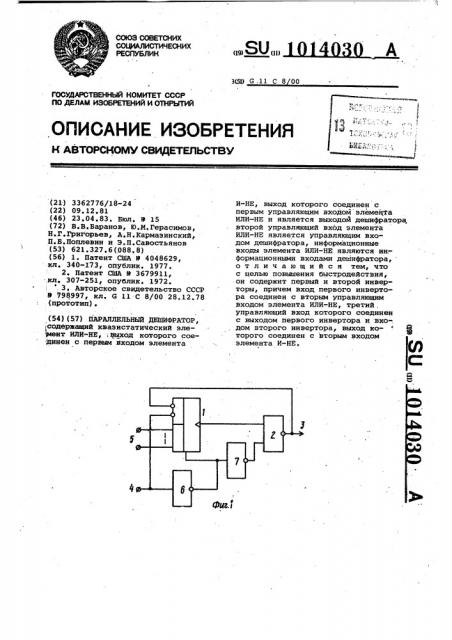

ИЛИ-НЕ, третий управляющий вход которого соединен с выходом первого инвертора и входом второго инвертора, вход которого соединен . с вторым входом элемента И-НЕ. .На фиг.1 представлена функциональная схема предлагаемого дешифратора; на фиг.2 - принципиальная электрическая схема квазистатическрго элемента ИЛИ-НЕ, Дешифратор содержит квазистатический элемент ИЛИ-HE 1, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с первым управляющим входом элемента ИЛИ-НЕ и является выходом 3 дешифратора. Второй управляющий вход элемента

ИЛИ-HE является управляющим входом

4 дешифратора. Информационные вхо" ды элементы ИЛИ-НЕ являются информационными входами 5 дешифратора.

Вход первого инвертора б соединен с вторым управляющим входом элемен-. та ИЛИ-НЕ l, выход которого соединен с выходом первого инвертора 6 и входом второго инвертора 7, выход которого соединен с вторым входом элемента И-НЕ.

Элемент ИЛИ-НЕ содержит группу ,параллельно соединенных транзисторов 8, затворы которых являются информационными входами элемента, истоки объедийены и являются третьим управ ляющим входом элемента, стоки объединены и являются выходом элемента, а также соединены с стоками нагрузочных транзисторов 9 и 10, истоки которых соединены с шиной 11 питания, а затворы являются соответственно первым и вторьж управляющим входами элемента ИЛИ-НЕ.

Параллельный дешифратор работает следующим образом.

В исходном состоянии (режим хранения} строб-сигнал на входе ин» вертора б соответствует уровню логического О, в результате чего на.. выходе первого инвертора 6 и третьем. управляющем входе элемента ИЛИ-НЕ напряжение соответствует логической 1 и такое же, как и íà его второй шине питания . Нагрузочный транзистор 9 в элементе ИЛИ-НЕ открыт и потенциал на выходе этого элемента соответствует логической 1 независимо от кода адресного сигнала на логических входах 5. Элемент не потребляет мощность в статичес- ком состоянии. На первом входе элемента И-НЕ потенциал соответствует

Редактор Г.Безвершенко й

Составитель Б.Бородин

Техреду. Гергель .. Корректор А . Тяско

:Заказ .3028/62 ..............Тираж .592 .........Подписное .

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д..4j5

Филиал ППП Патент, r. Ужгород, ул. Про .ктная, 4 логической 41 на втором - логическому О, в результате чего на выходе этого элемента 3, на первом управляющем входе элемента 1 потенциал способствует логической 1 .

Второй нагрузочный транзистор 10 в элементе ИЛИ-НЕ 1 закрыт.

В режиме разрешенйя на вход 4 подается строб-сигнал, который соответствует логической 1, в результате чего на выходе первого инвертора потенциал соответствует логическому Π— включено, питание элемента ИЛИ-НЕ 1. На выходе второго инвертора 7, -и на втором входе элемента И-НЕ 2 потенциал соответствует логическОЙ - 1 - разрешающий сигнал. Нагрузочные транзисторы 9 и 10 в элементе ИЛИ-НЕ

1 закрыты. В случае, если на всех входах 5 потенциалы соответствуют логическому О (ячейка выбрана), на выходе элемента ИЛИ-НЕ 1 и первом входе элемента И-НЕ сохраняется (в .динамическом режиме) потенциал, соответствующий логической 1 . На выходе 3 элемнты И-НЕ 2 появляется сигнал -выборки, соответствующий логическому О, и второй нагрузочный.транзистор 10 в элементе 1 открывается, поддерживая уровень логической 1 íà его стоке.

:,В случае, если на одном из выходов 5 потенциал соответствует логи ческой 1 (ячейка не выбрана), после установления на входе 4 сигнала логической 1 на выходе квазистатического элемента ИЛИ-НЕ устанавливается потенциал, соответствующий логическому . О, причем он .устанавливается раньше, чем сигнал логической . 1 на выходе второго инвертора 7 (на величину задержки. этого элемента) . В результате этого на выходе элемента И-HE 2 сохраняется потенциал логической 1 — отсутствие выборки.

При переключении в исходное состояние потенциал на входе 4 переключается на логический О, в результате чего на выходе второго инвертора 7 и втором входе

10 элемента И-HE. 2 устанавливается запрещающий сигнал логического . 0, а на выходе элемента

ИЛИ-НЕ 1 — разрешающий сигнал логической 1 . Причем первый:из них

15 должен установиться раньше, чем второй. Это условие обеспечивается соответствующим выбором размеров нагрузочного транзистора в элементе ИЛИ-НЕ 1 и размеров транзисторов в инверторах 6 и 7.

Повьыение быстродействия в пред-. лагаемой ячейке дешифратора достигается следующим. В схеме известного дешифратора имеется логический эле-.

25 мент с задержкой, наличие которого связано с необходимостью обеспечения синфазности работы узлов дешифратора. Для обеспечения нормальной работы дешифратора при разбросе хаЗО рактеристик компонентов схемы в условиях серийного производства задерж.ку логического элемента выбирают достаточно большой и приблизительно равной суммарной задержке остальных

35 каскадов схеьы. Схема предлагаемого дешифратора обладает более высоКим, :быстродействием,так как не содержит логических элементов с задержкой и ее быстродействие определяется толь40 ко суммой собственных задержек каскадов дешифратора.