Устройство для контроля дискретных объектов

Иллюстрации

Показать всеРеферат

СОКИ СОЖТСНИХ М Юй_#_й

РЕСПУБЛИК (19) (И) ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fO ДЕЛАМ ИЗОЬРЕТЕНИЙ И ОТНЯТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВ ГСРСИОММ СВИДЕТЕЛЬСТВУ

3(5)) G, 06 F 11/00 (21) 3412156/18-24

22) 16.03.82 (46) 30.06.83.Вюл. В 24 (7 2) A.B.аникеев и В. И. Долгов (.53) 621. 503. 55 (088. 8) (56) 1. Авторское свидетельство СССР

М 607218, кл. G 06 F 11/00, 1978.

2. Авторское свидетельство СССР и 721830, кл. 6 Об F 11/ОО, 1980 протатий).

54) (57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ДИСКРЕТНЫХ ОБЪЕКТОВ, содержащее блок памяти, блок ввода, блок управления, блок сравнения, причем группа выходов блока ввода подключена к группе инФормационных входов блока памяти, управляющий вход которого связан с пер. вым выходом блока управления, второй выход которого соединен с входом блока ввода,нервая группа информацион.ных выходов блока памяти подключе на к первой группе соответствую:щйх входов блока сравнейия, первыи . выход которого является контрольным выходом устройства, а второй вы ход связан с входом блока управле.— ния, вторая группа информационных выходов блока памяти соединена с группой соответствующих входов контролируемого блока, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия, в устройство введены комбинационный сумматор с циклическим переносом н регистр, причем первая группа информационных входов .комбинационного сумматора с циклическим переносом подключена к группе выходов контролируемого блока, вторая группа информационных входов комбинацйонного, .сумматора с циклическим переносом Q связана с группой выходов регистра, подключенных к второй группе соответ- . ствующих входов блока сравнения, груп-" па выходов комбинационного сумматора („„ с циклическим переносом соединена с группой входов регистра.. 102б143:

Изобретение относится к вычисли.тельной технике, в частности к автоматизированным системам контроля цифровых устройств, и может быть использовано для контроля цифровых устройс в5 в процессе их производства и эксплуатации.

Известно устройство для контроля цифровых блоков, содержащее блох ввода, блок памяти, коваюутатор, блок сравнения, блок управления и схему индикации неисправности 1 .

Недостатком устройства является большой расход памяти на хранеиие теС;тов и эталонов, а также неэозможность обеспечения контроля цифровых блоков, 3 5 работающих с высоким реальным быстро- действием.

Наиболее близким по технической сущнОсти к предлагаемому является устройство для контроля дискретных объектов, содержащее блок ввода, блок памяти, блок сравнения, блок управления, коммутаторы и многоэходовь и элемент ИЛИ.

Первый выход блока ввода связан с первым входом блока памяти, второй вход которого подключен к первому выходу блока- управления. Второй вы- » ,ход блока управления соединен с первым входом блока сравнения, а второй .Зо вы<од блока ввода связан с первым входом блока управления, третий выход которого подключен к входу блока ввода. Первый выход блока памяти подсоединен к второму входу блока сравнения

Второй выход блока памяти пбдеоединен к первому входу первого ксажутатора,: к второму входу которого. нодключен четвертый выход блока управления.

Выход первого коммутатора связаи с . первым входом миоговходоэого элемеи- 49 та ИХ1И, к второму входу которого под ключен первый выход второго коммута» тора. Второй выход второго коммута тора связан с третьим входом блока управления. Первый вход второго комму 35 танцора подсоединен к пятorî входу .блока управления. Выход блока сравнения подключен к второму входу блока управления. Выход миоговходоэого элемента ИЛИ и второй вход второго комму-5 татора являются соответственно выхо- . дом и входом. устройдтва. В таком устройстве по сигналу блока управления из блока памяти через коммутатор и многоэходовый элемент ИЛИ выдаются тестовые наборы на контролируемый объект. Реакции контролируемого объекта на тестовые наборы через коммутатор подаются иа блок сравнения, где сравниваются с эталонными реакциями, поступающими Н3 блока памяти. Сигнал 60 сравнения или несравнения выходных реакций с эталонными поступает s блок управления 2).

I(недостаткам этого устройства следует отнести большой объект блока памяти для хранения тестовых набрров и эталонных реакций, а также невозможность обеспечения контроля цифровых блоков, работающих с высоким реальным быстродействием из-за наличия двух обращений,к блоку памяти за тестом и эталоном, а также из-за задержки сигналов в целях коммутации.

Цель изобретения - повьхаение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля дискрет-. ных объектов, содержащее блок памяти, блоК ввода, блок управления, блок сравнейия, причем группа выходов блока ввода подключена к группе информационных входов блока памяти, урравляющий вход которого связан с первьм выхьдом блока управления, второй выход которого соединен с входом блока ввода, первая группа информационных выходов блока памяти подключена к первой группе соответствующих эходов блока сравнения, первый выход которого является контрольным выходом уст-: ройства, а второй выход связан с входом блока уиравления. вторая группа l информационных выходов блока памяти ., соединена с группой соответствующих; входов контролируемого блока, введе-, ны комбинационный сумматор с цикли- ческим переносом и регистр, причем первая группа информационных входов комбинационного сумматора с циклическим переносом подключена к группе выходов контролируемого блока, .вторая группа информационные входоэ комбинацибнного сумматора с циклическим переносом связана с группой выходов .регистра, подключенных к второй группе соответствующих входов блока срав-. нения, грунпа выходов комбинационного сумматора с циклическим переносом соединена с группой входоэ регистра.

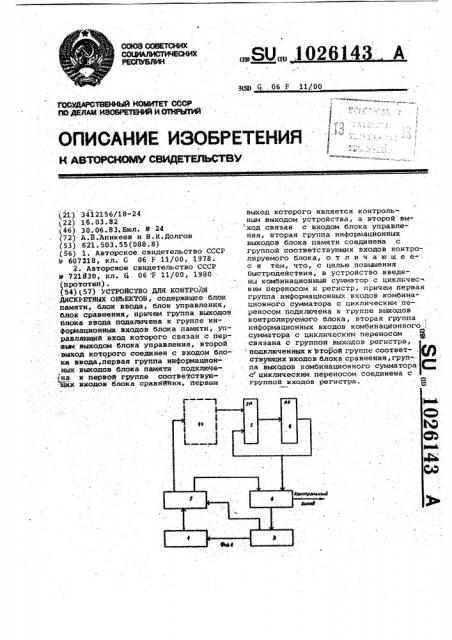

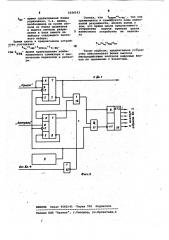

На фнг.1 представлена структурная схема устройства для контроля дискрет . ных объектов, на фиг.2 - функциональ-: на схема блока упоавлеиия.

Устройство для контроля дискретных объектов содержит блок 1 ввода, блок 2 памяти, блок 3 управления, блок 4 сравнения, комбинационный сумматор 5 с циклическим переносом; регистр.б..

Блок управления выполнен по схе-, ме управляющего автомата с "жесткой" логикой и содержит дэа С-И триггера

7 и 8; генератор 9 импульсов, двоич-.... ный счетчик.. 10, элемент 11, элемент.:

ИЛИ 12, элемент HE 13. Выход генера тора 9 импульсов подсоединен к

С-входам триггеров 7 и 8 и. к первому входу элемента И 11. Входы К и Ъ триггера 7 соединены между собой и совместно с входом ц триггера 8 являются внешними входами бЛока 3 управления. Входы 6 триггеров 7 и 8

3 10261 связаны со своими инверсными выходами, а вход К триггера 8 подключен к выходу элемента НК 13, вход которого являетСя входом блока 3 управления.

Прямые выходы триггеров 7 и 8 связа- . ны с первым и вторым входами, соот-, 5 ветственно элемента IJIH 12, выход которого подсоединен к входу Я счет.чика 10 и второму входу элемента И 11.

Выход элемента И 11 связан:со счетным входом счетчика 10. Выходы счет- К чика 10 являются вторым выходом бло .ка 3 управления и подключены к адресным шинам блока 2 памяти. Прямой выход триггера 7 подключен к входу блока 1 ввода. Кроме того, устройство содержит контролируемый цифровой блок 14. устройство работает следующим образом.

По сигналу с блока 3 управления чеблок 1 ввода в блок 2 памяти поступает тестовая информация в виде тестовых наборов. По,сигналу начала контроля, выдаваемому с блока 3 управления, блок 2 памяти начинает подавать тестовые наборы на контролируемый цифровой блок. Реакцни на тестовые наборы. поступают на сумматор 5 с циклическим переносом, где суммируются с циклической суммой, полученной s предыдущих циклах, хра- ЗО нящейся в регистре 6 и получаемой на сумматоре 5 в исходном состоянии регистр 6 в "О") . После прохождения всех тестовых наборов блок 2 памяти выдает на блок 4 сравнения 35 эталонную. контрольную сумму, которая сравнивается с контрольной суммой, полученной в результате прохож« денни тестовых наборов и хранящейся в регистре 6. Поскольку в блоке 2 па- О мяти хранятся только тестовые наборы и не хранятся эталонные реакции, это приводит к..сокращению объема блока 2 памяти для хранения тестовых эталонов в два раза.

По результатам сравнения блок 4 сравнения выдает сигнал исправности или неисправности контролируемого цифрового блока.

Таким. обРазом, Устройство работает в двух режимах в режиме приема тестовых наборов и эталонной суммы и и режйме контроля. В соответствии с этими режимами и функционирует блок 3 управления. Сигнал "Прием" поступает на вход приема триггера 7 и сохраняется на вхЬде до тех цор, пока не примется в блок 2 памяти вся тестовая информация. Триггер:7 устанавливается в единичное положение и разрешает прохождение импуль- 60 сов с выхода генератора 9 импульсов через элемент И 11 на счетный вход счетчика 10, а также выдачу тестов из блока 1 ввода s блок 2 памяти (до прихода сигнала ПРием счет, 65

43 чик обнулен нулевым сигналом с +p- вых выходов триггеров 7 и 8 через элемент KHH 1?). Счетчик 10 начинает считать и тестовая информадия, по- .. ступающая с блока 1 ввода в блок 2 памяти, записывается в массив последовательных ячеек блока 2. После записи всех тестов сигнал "Прием" снимается, и триггр 7 устанавливает- ся в " О", устанавливается в "О" и, счетчик 10.Режим "Прием" заканчивается.

В режиме "Контроль" на вход . триггера 8 поступает единичный.импульсный сигнал, который устанавливает триггер 8 в "1". Сигнал с прямого выхода триггера 8 через элементы 12, и 11 разрешает подачу импульсов на счетный вход счетчика 10. Счетчик 10 начинает считать .и блок 2 .памяти вы- дает тесты иа контролируемый (цифровой блок . После прохождения всех тео; тдв н сравнения контрольной суммы с эталонной блок 4 сравнения через элемент НЕ 13 устанавливает триггер 8 в "О", счетчик 10.сбрасывается в

"О" и режим "Контроль" заканчивается. Если контрольная и эталонная суммы не совпадают, то счетчик 10 выхо.-,. дит эа границу массива тестов что соответствует отсутствию сигнала на контрольном выходе блока. 4 сравнения и.является признаком наличия неисправности в контролируемом (цифровом) .блоке 14.

В устройстве в блоке памяти на один тестовый набор приходится одна эталонная реакция. Эта тестовая информаци занимает в блоке памяти две ячейки. В предлагаемом устройстве хранятся только тестовые наборы и одну ячейку памяти занимает контрольная сумма. Следовательно, достигается с6кращение объема памяти для хранения тестовой нн4}ормации в предлагаемом устройстве по сравнению с известным в: два раза. Это ведет к сокраще-. нию трудоемкости изготовления и стоимости блока. памяти. Время цикла, т.е. время между двумя выборками тес- товых наборов иэ блока памяти в,известном устройстве составляет ц„ аур щурл+ Рзакц сров "s1 где ц - время цикла известного устройства;

" время обращения к блоку . памяти за тестовым наборомr

- время срабатывания элементов коммутации, Ь - время реакции контроли-руемого объекта на тесто вый набор;

" время срабатывания- блока .. } ®- еравнения;

1026143

Ю ц., ц, ве 4 вч. иг.i

ВНИИПИ Заказ 4560/41 Тираж 706 Подписное

° аюеаэмвФв Фавелы

Филиал ППП "Патент" > г.ужгород, ул.Проектная,4

- время срабатывания блока в управления, т.е. spew,„ необходимое на прием сигнала из блока сравнения . и выдачи сигнала разрешения в блок памяти на выборку следующего тесто-, вого набора.

Время цикла в предлагаемом устрой стае составляет иа сВР Рао ц х-яб где 4< - время срабатывания комбинационного сумматора с цик-, лическим переносом и регист ра ° /

Считая что 4eo =tx Ro i, так как сраниваются и суммируются, коды одинаковой разрядности, делаем вывод о том, что время цикла предлагаемого / устройства, короче времени цикла

5 известного устройства на величину

Таким образом, предлагаемое устрой, ство обеспечивает более высокое быстродействие контроли цифровых блоков по сравнению с известным.