Усилитель считывания на дополняющих мдп-транзисторах

Иллюстрации

Показать всеРеферат

СООЗ СОВЕТСНИХ

О 4М

РЕСПУБЛИК 5р j11 с 7/оо

ГОСУДдРС ЩЕИНЬй НОМИТЕт СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ с Ь (21) 3359585/13-24 (22) ОВ. 12. 81 (46) 1>.07.83. Вюл. + 2á (72) В.В. Варанов, В.И. Герасимов, H,Ã. Григорьев, A.Í. Кармазинский, 6.8. 66плеэин и Э;П. CaB TsRHos (53) 681 327.6(688.8) (54) 1. Авторское свидетельство СССР

В 739á43 кл 611 С 7/ОО, 1979.

2. Иатент Англии и 2618Î76, кл (; 11 С 7/ОО, опубзщк. 1978 (прототип). (S4) (S7) vc varrsm

Q)M38%35(X И 1- С ОР Х, содержащий первый и второй ключевые

Р канальные транзисторы, соединен.ные перекрестной связью, стоки которых соединены соответственно с вксадии первого и второго ииэерторов на транзисторах и соответственно, со стоками первого.и второго нагрузочных И -канальных транзисторов, истоки которых соединены со стоком стробирующего И -канального транзистора, затвор которого. соединен с шиной строба, исток - с общей шиной, о т л и ч а ю шийся тем, что, с целью поэьпаения чувствительности усилителя, он содержит три группы ключевых транзисторов,,SU„„1029227 A каждая иэ которых содержит по два р -канальных транзистора причем истоки первого и второго транзисторов первой группы соединены с шиной питания, затворы — соответственно с выжодамя первого и второго инверто.ров, стоки - соответственно с исто камн пефвого и второго транзисторов второй группы, затворы которых

; соединены со стоками и являются соответственно первым и вторым входами усилителя считывания, которые сое.— динены соответственно с истоками первого и второго транзисторов третьей группы, стоки которых соединены соответственно со стоками первого и второго нагрузочных ss -канальных транзисторов, затворы †.с шиной строба, истоки первого и второго ключевых р -канальных транзисторов являются соответственно пер вым и вторым входами усилителя считывания, затвор первого Н -канального нагруэочного транзистора соединен со стоком второго нагрузочного И -канального транзистора, затвор которого .соединен со стоком первого нагрузочного и -канального транзистора, а истоки. транзисторов инверторов соединены с истоком стробирукщего транзистора.

1029227

Изобретени относится к вычислитеЛьной технике и может быть применено для усиления сигналов считывае,мой информации в запоминающих устройствах на дополняющих МДП-транзисторах.

Известны усилители считывания, построенные на основе триггера, потенциалы выходов в котором устанавливаются до одинакового уровня с помощью транзисторов, включенных между выходами триггера, или с помощью транзисторов, включенных между выходами триггера и одной иэ шин питания (1 ).

Недостатком таких усилителей 15 является низкая чувствительность

Наиболее близким техническим решением к изобретению является усилитель считывания на дополняющих

МДП-транзисторах, содержащий первый 2О и второй р --канальные транзисторы, соединенные по схеме с перекрестной связью, стоки которых соединены соответственно со входами первого и второго инверторов и соответствен- 25 но со стоками первого и второго нагрузочных и -канальных транзисторов, истоки которых соединены со стоком стробирующего ;. -канального транзистора, затвор которого соединен с шиной строба, исток с общей шиной, а также содержащий шину питания, первый и второй входы 2)е

Недостатком известного усилителя считывания является низкая чувствительность, обуслоВленная невозможностью изменения напряжения между истоками р --канальных транзисторов, соединенных по схеме с перекрестной связью, а также между стоками этих 4О транзисторов.

Цель изобретения - повышение чувствительности усилителя считывания на дополняющих МДП-транзисторах.

Поставленная цель достигается тем, что в усилителе считывания на дополняющих ИДП-транзисторах, содержащем первый и второй ключевые р -канальные транзисторы, соединенные перекрестной связью, стоки которых соединены соответственно со входами первого и второго инверторов на транзисторах и соответственно со стоками первого и второго нагрузочных И -канальных транзисторов, истоки которых соединены со стоком стробирующего -канального транзистора, затвор которого соединен с шиной строба, исток — с общей шиной, введены три группы ключевых 60 транзисторов, каждая из которых содержит по два р --канальных транзистора, причем истоки первого и второго транзисторов первой группы сое-, динены с шиной питания, эатворы—

I соответственно с выходами первого и второго инверторов, стоки соответ-ственно с истоками первого и второго транзисторов второй группы, затворы которых соединены со стоками и являются соответственно первым и вторым входами усилителя считывания, которые соединены соответственно с истоками первого и второго транзисторов третьей группы, стоки которых соединены соответственно со стоками первого и второго нагрузочных и -канальных транзисторов, затворы— с шиной строба, истоки первого и второго ключевых р -канальных транзисторов являются соответственно первым и вторым входами усилителя считывания, затвор первого и -канального нагрузочного транзистора соединен со стоком второго нагрузочного И -канального транзистора, затвор которого соединен со стоком первого нагрузочного r> -канального транзистора, а истоки транзисторов инверторов соединены с истоком стробирующего транзистора.

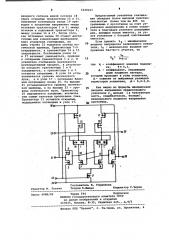

На чертеже дана принципиальная схема усилителя считывания на дополняющих МДП-транзисторах.

Усили ель содержит первый и второй ключевые Р -канальные транзисторы 1 и 2, соединенные перекрестной связью, первый инвертор на транзисторах 3 и 4, второй инвертор на транзисторах 5 и б, первый и второй нагрузочные И -канальные транзисторы 7 и 8, стробирующий и -канальный транзистор 9, первый и второй р --канальные транзисторы первой группы 10 и 11, первый и второй р -канальные транзисторы второй группы

12 и 13, первый и второй р -канальные транзисторы третьей группы 14 и 15, узлы 16 и 17, шину питания

18, первый и второй входы 19 и 20, первый и второй выходы 21 и 22, шину строба 23 и общую шину 24.

Усилитель считывания на дополняющих МДП-транзисторах работает следующим образом.

В режиме хранения и записи потенциалы шин 18-20 соответствуют ! уровню логической единицы, а на шинах 23 и 24 — уровню логического нуля. Транзисторы 3,5,10,11 и 15 открыты, а транзисторы 1,2,4,6

9,12 и 13 закрыты. При этом потенциалы в узлах 16 и 17 соответствуют уровню логической единицы, а на выходах 21 и 22 — уровню логического нуля.

В режиме считывания напряжение на входах 19 и 20 начинает изменяться. Если потенциал входа 19 уменьшается, а потенциал входа 20 остается прежним, закрытые транзисторы

12 и 13 исключают пунктирование

1029227 ч«« ф 1н + d.

Составитель В. Гордонова

Техред K,Иыцъо Корректор С.Черни

Редактор М. Товтин

Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 4988/49

Филиал ППП "Патент", r. Уж:ород, ул. Проектная, 4 входного сигнала шиной питания 18 через открытые транзисторы 10 и 11.

Изменение потенциала входа 19 приводит к появлению напряжения между истоками транзисторов 1 и 2, между истоком и подложкой транзистора 1, между узлами 16 н 17. После того, как потенциал входа 19 станет достаточным для компенсации разбалансе плеч усилителя считывания, на шину строба 23 подается сигнал логической единицы. Транзисторы 7-9 открываются, а транзисторы 14 и 15 закрываются. Потенциалы узлов 16 н 17 начинают уменьшаться, приводя к отпиранию транзисторов 1 н 2. В усилителе считывания развивается регенеративный процесс, в результате которого транзисторы 1 и 8 закрываются,. а транзисторы 2 и.7 остаются открытыми. 8 узле 16 устанавливается уровень логического нуля, а в узле 17 - потенциал близкий.потенциалу входа 20. На выходе

21 устанавливается уровень логической единицы, а на выходе 22 — уровень логического нуля. Транзистор

10 окнэывается -закрытым, исключая тем самым сквозное протекание тока.

Транзистор 11 остается открытым, пор держивая потенциал в узле 17.

Предлагаемый усилитель считывания обладает более высокой чувствительностью более чем на 40% по сравнению с прототипом за счет уп5 равления.напряжением в узлах усилителя и благодаря развязке разрядных шин, имеюших малую емкость, от узлов усилителя с большой собственной емкостью.

Если дринять Ч«„ - минимальное

«О входное напряжение заявляемого усилителя, 4y — минимальное входное напряжение базового объекта, то

15 где - коэффициент влияния подложки, « - 0,3, cL - коэФФнциеит, отражаниций

20 долю входного сигнала, который проходит в узлы усилителя, с6- зависит от выбранных размеров тиристоров усилителя, af. 0,4-1,0.

25 Как видно»»a Формулы минимальное входное напряженке предлагаемс«го усилителя Ц меньше (а чувствител»

c33oggá @ h»«, больше ), минимального входного напряжения

ЗО прототипа. °