Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий суммирующие тетрады, каждая из которых состоит из многовходовых одноразрядных сумматоров, входы i-го ((n-l) многовходового одноразрядного сумматора, где п - число разрядов входного кода, соединены с разрядными входами преобразователя, двоичные весовые эквиваленты которых содержат единицу в 2-м разряде, отличающийся тем, что, с целью повышения быстродействия, в него введены шифраторы, входы которых соединены со всеми выходс1ми соответствующих суммирующих тетрад, кроме выходов младших разрядрв, информационные выходы шифраторов соединены с выходами трех старших разрядов тетрад выходов преобразователя, выходы переноса }-го шифратора (j 1тЗ ) соединены с входами переноса (j +1) суммирующей тетр ады, выходы переноса последней суммирующей тетрады соединены со старшей тетрадой выходов преобразователя,.младшие Л разряды суммирующих тетрад соединены с младшими разрядами соответствующих декад выходов преобразователя.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11);

3(51) G 06 F 5/02

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Г)О ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITHA

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1

Т 1

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3406628/18-24 (22) 02.02.82 (46) 23.09.83. Бюл. М 35 (72) З.А.Джирквелишвили,В.Ф.Евдокимов, И.Ф.Зубенко, Р.О.Овакимов, Н.Ю.Пивень и Ю.A.Ïëþù (71) Институт проблем моделирования в энергетийе AH Украинской CCP (53) 621,32 5 (Ое88) (56) 1 ° Авторское свидетельство СССР

9 476561, кл. G 06 F 5/02, 1973.

2. Патент США М 3614403, кл. 235-155., 1971 (прототип). (54)(57) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО

КОДА В .ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий суммирующие тетрады, каждая из которых состоит из многовходовых одноразрядных сумматоров, входы l-го (1=1-, (п-1) многовходового одноразрядного сумматора, где n — число .разрядов входного кода, соединены с разрядными входами преобразователя, двоичные весовые эквиваленты которых содержат единицу в 2-м разряде, отличающийся тем, что, с целью повьыения быстродействия, s него введены шифраторы, входы которых соединены со всеми выходами соответствующих суммирующих тетрад, кроме выходов младших разрядов, информационные выходы шифраторов соединены .с выходами трех старших разрядов тетрад выходов преобразователя, выходы переноса 1-ro шиФратора (j =

=1-:(†(. ) соединены с входами пере4 носа (j+1) суммирующей тетрады, выходы переноса последней суммирующей тетрады соединены со старшей тетраФ дой выходов преобразователя, . младшие разряды суммирующих тетрзд соединены с младшими разрядами соответствующих декад выходов преобразователя.

1043627

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования кодов иэ одной системы счисления в другую.

Известен преобразователь двоично- 5

ro кода в двоично-десятичный, содер жащий суммирующие тетрады, состоящие иэ сумматоров, блоки коррекции и блоки переноса, причем выходы суммы сумматоров всех весов, кроме 10 веса 1 каждой суммирующей тетрады, соединены со входами блока коррек. ции и блока переноса той же тетрады, а выходы блока переноса каждой суммирующей тетрады соединены со входами )5 двух. младших разрядов соседней старшей суммирующей тетрады (1).

Недостаток данного преобразователя состоит в низком бцстродействии;

Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятичнь3й код, содержащий группы сумматоров, блокй переноса и блоки коррекции, входы которых соединены с выходами послед-. ней группы сумматоров, выходы блока переноса соседней старшей групмы сумматоров )2) .

Недостаток известного преобразователя состоит в относительно низком быстродействии, связанном с тем, что блок коррекции также выполнен в виде сумматора.

Цель изобретения — повышение быстродействия. 35

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий суммирующие тетрады, каж.дая из которых состоит иэ многовхо- 40 довых одноразрядных.сумматоров., причем входы i-ro (i=1 - . (n — 1) многовходового одноразрядного сумматора, где и — число разрядов BxoltHoro да, соединены с разрядными.входами преобразователя, двоичные весовые эквиваленты которых содержат единицу в 2-м разряде, дополнительно введены шифраторы, входы которых соединены со всеми выходами соответствующих суммирующих тетрад, кроме выхо дов младших разрядов, информационные выходы шифраторов соединены с выходами трех старших разрядов тетрад выходов преобразователя, выходы переноса j -го шифратора (j=l -1 †" t ) зз .4 соединены с входами переноса (j +1)-й суммирующей тетрады, выходы переноса последней суммирующей тетрады соединены со старшей тетрадой выходов преобразователя, младшие разряды 60 суммирующих тетрад соединены с младшими разрядами соответствующих декад выходов преобразователя.

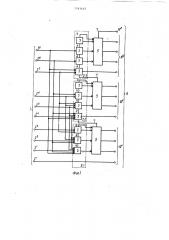

На Фиг, 1 приведена блок-схема предлагаемого преобразователя; на 65

Фиг, 2 — пример реализации пятиразрядного преобразователя.

Предлагаемый преобразователь содержит (фиг. 1) разрядные входы 1 преобразователя,,суммирующие тетради 2-1, 2-2,2-3, выполненные на многовходовых одноразрядных суммато рах 3, выходы переноса 4 суммирующих тетрад соединены со входами шифратора 5, информационные выходы которых и выход младшего разряда суммирующей

1 тетрады образуют тетраду выходов б преобразователя. Выходы переноса 7 всех шифраторов 5 кроме последнего соединены со входами переноса соседней суммйрующей тетрады.

Взаимосвязь между входными и выходными кодами шифратора 5 отображена в таблице.

Пример. При поступлении на разрядные входы 1 преобразователя двоичного кодаа(. .,=1111101000 что соответствует подаче единиц на входы с весами 2,2",2,26,2,2 и нулей на остальные входы, на выходах суммирующей тетрады 2-1 после окончания.переходного процесса, появится значение кода 01111. В соответствии с таблицей на информационных выходах шифратора 5 образуется код

000. Таким образом, общий код тетрады будет равным 0000 ° На. выходах переноса шифратора 5, в соответствии с таблицей, формируется значение кода 011.

Аналогично, на выходах суммирующей тетрады. 2-2 в соответствии со схемой соединений появляется значение кода 001010. При этом на информационных выходах шифратора 5 образуется код 000, а на выходах переноса шифратора 5 образуется код 001.

Общий код тетрады весом 10 будет равным 0000.

На выходах суммирующей тетрады

2-2 в соответствии со схемой соединений также образуется значение кода 001010, что соответствует общему коду тетрады с весом 10 равноI

9 му 0000, и коду тетрады с весом 10 равному 1.

Таким образом,в результате преобразования на выходах б преобразователя получается двоично-десятичный код 10000 0000 0000, соответствующий коду 1111101000.

На фиг. 2 представлена блок-схема первой тетрады предлагаемого преобразователя, в котором суммирующие тетрады построены с использованием трехвходовых двоичных сумматоров. Здесь проставлены времена переходных процессов.

Общее время переходного процесса (фиг. 2) для первой тетрады составляет и и

1,(5 lgIZlt + (ц (l) 1043627 где ь .„- время переходного процесса в трехвходовом двоичном сумматоре; и ь — время преобразования кода в шифраторе 5.

Далее, учитывая, что предлагаемое устройство можно рассматривать как последовательно включенные между собой аналогичные тетрады, общее время переходного процесса десятираэрядного преобразователя может быть оценено следующей формулой лл3Ф. =157, и,+3 (, „. (2)

В преобразователе (2) время преобразования пятиразрядного двоичного кода равно л

"вр =10 „, +2 и-на в (3) (4) О О О О О О

О .О

О О

1 О

2 О

3 О

4 О

О О

ОО. О 1

О О.1 О

О О О

О 0

О О

5 О

6 О

7 О

8 О

9 О

О О

О О

О О

О 1

О О

1 О

О О

О О

О О

10 О 1 О 1 О

11 О 1 О 1 1

О 1

О 1

О О

О О 1

12 О

13 О

14 О

15 О

О О

О 1

О

О 1

О 1

О 1 О

О 1 1

О О

1 1 1 О

1 1 1 1

О 1

О 1

О О

О 1

О

16 1 О О О О

17 1 О О О 1

О 1

О 1

1 О

О О

О О

1 О

1,1

О 1

О 1

1 О

1

О 1 1

1 О О

О 1 О О

О 1 О 1

О 1 1 О

О

О

О

О О

О 1

l О

1 1

О О

1 О

1 О

О 1

1 О

1 1

О О

1 О.

1 О

О

1 О

1 О О 1

1 О 1 О

О О

1 О

О 1

27 1

28 1

29 1

30 l

1 О

1 1

1 1

О О

1 О

1 О

О

1 О

1 1

О 1

1 О.1 О

1 1

О О

О О

О

31 1 1 1 1 1

О 1

l8 1

19 1

20 1

2l 1

22 1

23 1

24 1

25 1

26 1

О О О 1

О О 1 О

О О 1 1

О 1 О О

О 1 О .1

О 1 1 О

О 1 1 1

1 О О О

1 О О 1 где и — время переходного процесНВ са в схеме И-НЕ.

Для определения соотношений и л между,ц и аэн можно принять л и (ы =3 5 и-не

Тогда общее сокращение времени преобразования и в предложенном преобразователе равно л л °

Ьпр 5 g q -li5

15 известный по быстродействию.

1043627

02

ФигЛ

1043627

Составитель И. варшавский

Редактор П.Коссей Техред М,Гергель.

Корректор C.Øåêìàð

Заказ 7338/51 Тирам 706

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35р Раушская наб., д. 4/5

Подписное

Филиал IltltI Патент г. Ужгород, ул, Проектная, 4