Адресный формирователь

Иллюстрации

Показать всеРеферат

C0IO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (584 С 11 С !1/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

f10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABT0PCHOMV СЕИДЕ ГЕПЬСТВУ 4 5!pp;gg r р (21) 2898940/18-24 (22) 26.03,80 (46) 15;05.88. Бюл. Р 18 (72) А.А.Кассихин и А.О.Романов (53) 681. 327. 6 (088.8) (56) Авторское свидетельство СССР

У 296263, кл. Н 03 К 19/08, 1969.

Патент США Ф 3946369, кл. 340-173, 1976. (54)(57) АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ, содержащий десять МОП-транзисторов, затвор и исток первого транзистора подключены к стоку второго транзистора, затвор которого соединен с входной шиной, а сток соединен с затвором четвертого транзистора, сток которого подключен к затвору и истоку третьего транзистора, исток которого соединен с затвором шестого транзистора, сток которого соединен с затвором и истоком пятого транзистора, затвор седьмого транзистора подключен к стоку шестого транзистора, исток сое.динен со стоком восьмого транзистора и выходом инверсного сигнала, затвор девятого транзистора подключен к стоку четвертого транзистора, исток сое„,SU„„1047314 A динен со стоком десятого транзистора и с выходом прямого сигнала, стоки первого, третьего, пятого, седьмого и девятого транзисторов подключены к . шине питания, истоки второго, четвертого, шестого, восьмого и десятого транзисторов подключены к шине общего потенциала, о т л и ч а ю щ и й— с я тем, что, с целью повышения быстродействия адресного формирователя, он содержит одиннадцатый, двенадцатый тринадцатый и четырнадцатый МОП-транзисторы, затворы одиннадцатого и двенадцатого транзисторов соединены со стоком четвертого транзистора зат1

Щ воры тринадцатого и четырнадцатого транзисторов соединены со стоком шестого транзистора, исток двенадцатого и сток четырнадцатого транзисторов подключены к затвору восьмого транзистора, сток одиннадцатого и исток тринадцатого транзисторов подключе- ны к затвору десятого транзистора, 1 стоки двенадцатого и тринадцатого транзисторов соединены с шиной питания, истоки одиннадцатого и четырнадцатого транзисторов соединены с шиной общего потенциала.

104 7314

Изобретение относится к области вычислительной техники и может найти применение при разработке МОПинтегральных схем запоминающих уст5 ройств.

Известна адресная буферная схема, содержащая первый и второй инвертор" ные каскады с бутстрепными нагрузками, а также две пары выходных транзисторов, включенных последовательно между шиной питания и внутренней шиной земли. Затвор выходного транзистора, сток которого подключен к шине питания .в одной паре, и затвор выходного транзистора, исток которого подключен к внутренней шине земли в другой паре выходных транзисторов, подключены к выходу одного инверторного каскада с бутстрепной нагрузкой. Выход- gp ные шины подключены к общему переходу между выходными транзисторами в парных соединениях этих транзисторов.

Недостатком этой буферной схемы является низкое быстродействие, свя- 25 занное с низкой скоростью нарастания и спада потенциалов на выходных шинах из-за медленного формирования сигналов управления выходными транзисторами бутстрепными инверторными каска- щ дами, для которых эти выходные транзисторы представляют значительную емкостную нагрузку.

Наиболее близкой к предлагаемому техническому решению является адресная буферная схема, содержащая МОПтранзисторы, выходной узел, внутренние узлы, причем два последних являются также выходами схемы соответственно инверсным и прямым, шину об- 4О щего потенциала и шину питания. Первый транзистор обедненного типа., сток которого подключен к шине питания, вместе с вторым транзистором обогащенного типа, исток которого подключен 45 к шине общего потенциала, затвор - к входному узлу, сток — к истоку и затвору первого транзистора, образуют инверторный каскад. Второй инверторный каскад состоит из третьего транзистора обедненного типа, сток которого подключен к шине питания, и четвертого транзистора обогащенного типа, исток которого подключен к шине общего потенциала, затвор — к выходу первого инверторного каскада — узлу, соединяющему затвор и исток первого транзистора и сток второго транзистора, а сток подключен к затвору и истоку третьего транзистора в узле— выходе второго инверторного каскада.

Третий инверторный каскад содержит пятый транзистор обедненного типа, сток которого подключен к шине питания, и шестой транзистор обогащенного типа, исток которого соединен с шиной общего потенциала, затвор — с выходом второго инверторного каскада, сток — с затвором и истоком пятого транзистора в выходном узле третьего инверторного каскада. Выход подключен к шине питания через седьмой транзистор обедненного типа, затвор которого подключен к выходу третьего инверторного каскада, к шине общего потенциала через восьмой транзистор обогащенного типа, затвор которого соединен с выходом второго инверторного каскада. Выход подключен к шине питания через девятый транзистор .обедненного типа, затвор которого подключен к выходу второго инверторного каскада, к шине общего потенциала через десятый транзистор обогащенного типа, затвор которого соединен с выходом третьего инверторного каскада.

Недостатком этой адресной буферной схемы является низкое быстродействие.

Целью изобретения является увеличение быстродействия адресного формирователя.

Поставленная цель достигается тем, что адресные формирователь, содержащий десять MOIL-транзисторов, затвор и исток первого транзистора подключены к стоку второго транзистора, затвор которого соединен с входной шиной, а сток соединен с затвором четвертого транзистора, сток которого подключен к затвору и истоку третьего транзистора, исток которого соединен с затвором шестого транзистора, сток которого соединен с затвором и истоком пятого транзистора, затвор седьмого транзистора подключен к стоку шестого транзистора, исток соединен со стоком восьмого транзистора и выходом инверсного сигнала, затвор девятого транзистора подключен к стоку четвертого транзистора, исток соеди" нен со стоком десятого транзистора и с выходом прямого сигнала, стоки первого, третьего, пятого, седьмого и девятого транзисторов подключены к шине питания, истоки второго, четвертого, шестого, восьмого и десятого транзисторов подключены к шине об104 7314 щего потенциала, дополнительно содержит одиннадцатый, двенадцатый, тринадцатый и четырнадцатый МОП-транзисторы, затворы одиннадцатого и две- 5 надцатого транзисторов соединены со. стоком четвертого транзистора, затворы тринадцатого и четырнадцатого транзисторов соединены со стоком шестого транзистора, исток двенадцатого и сток четырнадцатого транзисторов подключены к затвору восьмого транзистора, сток .одиннадцатого и исток тринадцатого транзисторов подключены

10 к затвору десятого транзистора, стоки 15 двенадцатого и тринадцатого транзисторов соединены с шиной питания, истоки одиннадцатого и четырнадцатого транзисторов соединены с шиной общего потенциала. 20

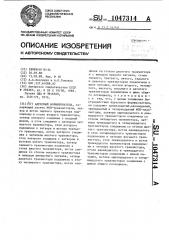

На чертеже изображена принципиаль- ная схема адресного формирователя,содержащего транзисторы 1-14, вход 1 5 формирователя, внутренние узлы 1622, причем узлы 19 и 20 являются так- 25 же выходами формирователя соответственно инверсным и прямым, шину общего потенциала 23 и шину питания 24.

Транзистор 1 обедненного типа, сток которого подключен к шине питания 24, вместе с транзистором 2 обогащенного типа, исток которого под30 кпючен к шине общего. потенциала, затвор — к входу 15, сток — к истоку и затвору транзистора 1, в узле 16 образуют первый инверторный каскад.

Второй инверторный каскад состоит из транзистора 3 обедненного типа, сток которого подключен к шине пита35 ния 24, и транзистора 4 обогащенного

40 типа, исток которого подключен к шине общего потенциала, затвор — к выходу первого инверторного каскада 16, а сток подключен к затвору и истоку транзистора 3 в узле 17 — выходе вто- 45 рого инверторного каскада. Третий инверторный каскад содержит транзистор 5 обедненного типа, сток которого. подключен к шине питания 24, и транзистор 6 обогащенного типа, исток которого соединен с шиной общего потенциала, затвор — с выходом 17 второго инверторного каскада, сток— с затвором и истоком транзистора $ в узле 18 — выходном узле третьего ин55 верторного каскада. Инверсный выход

19 подключен к шине питания 24 через транзистор 7, затвор которого .поключен к выходу третьего инверторного каскада — к узлу 18, к шине общего потенциала через транзистор 8 обогащенного типа. Прямой выход 20 подключен к шине питания 24 через транзистор 9, затвор которого подключен к выходу второго инверторного каскада — узлу 17, к шине общего потенциала через транзистор 10 обогащенного типа. Стоки транзисторов 1.2 и 13 обогащенного типа подключены к шине питания 24, истоки транзисторов 11 и 14 подключены к шине общего потенциала.

Затворы транзисторов 13 и 14 соединены между собой и со стоком транзистора 6 — выходом 18 третьего инверторного каскада. Затворы транзисторов 11 и 12 соединены межцу собой и. со стоком транзистора 4 — выходом

17 второго инверторного каскада. Исток транзистора 13 и сток транзистора 11 соединены между собой и с затвором транзистора 10 в узле 21. Исток транзистора 12 и сток транзистора !4 соединены между собой и с saтвором транзистора 8 в узле 22.

В работе формирователя цри переходе на входе от высокого к низкому и от низкого к высокому уровням нет существенного различия, поэтому ниже описаны переходные процессы формирователя, вызываемые первым переходом — при повышении напряжения на зходе 15. До повышения напряжения уровень входного напряжения низкий и . тока через транзистор 2 обогащенного типа нет. Благодаря этому выходное напряжение первого инверторного каскада в его выходном узле 16 высокое, включающее транзистор 4 - активный прибор второго инверторного каскада, который имеет поэтому низкое значение выходного напряжения, приложенного к затворам транзисторов 6, 1 1, 12, 9. Третий инверторный каскад инвертирует этот уровень и включает транзисторы 13, 14, 7. Транзисторы

7 и 9 могут быть как приборами обедненного типа, так и приборами обогащенного типа.

Для получения максимально высокого быстродействия при умеренном потреблении мощности более предпочтительным является выполнение их как приборов обогащенного типа с малым, почти нулевым пороговым напряжением и малым влиянием подложки на пороговое напряжение. В этом последнем случае транзисторы 9, 11, 12 не проводят

5 10473 тока, а транзисторы 7, 13, 14 включены К затвору транзистора 8 при проводящем транзисторе 14 и непроводящем транзисторе 12 приложено напря5 жение, равное потенциалу общей шины, при котором транзистор 8 обогащенного типа не проводит. Поскольку на затворе транзистора 7 высокий потенциал, то выходное напряжение инверсного выхода высокое. При непроводящем транзисторе l1 транзистор 13 поддерживает в узле 21 высокое напряжение; включающее транзистор 10, связанный затвором с этим узлом. Поэтому íà его 15 стоке - прямом выходе 20 — низкое напряжение уровня общей шины, поскольку тока через транзистор 9 нет.С момента появления положительного напряжения высокого уровня на затворе транзис- 20 тора 2 напряжение на его стоке падает, приближаясь по своему уровню к потенциалу общей шины. Зто падение напряжения запирает транзистор 4, вызывая, в свою очередь, возрастание выходно- 25

ro напряжения второго инверторного каскада в узле 17 до высокого значения, равного потенциалу шины питания

24. Вместе с отпиранием этим высоким напряжением транзистора 6 перестают 30 проводить ток транзисторы 13, 14, 7, управляющиеся с выхода 18 третьего инверторного.каскада со спадающим уровнем напряжения. Одновременно с этим по мере увеличения потенциала в 35 узле 17 транзисторы 11, 12, 9 вводятся в проводящее состояние. Транзистор 11 разряжает затвор транзистора 10, устраняя препятствие для заряда прямого выхода 20 транзистором 9.. 4О

Транзистор 12 заряжает затвор транзистора 8 для сброса на общую шину заряда в узле 19 — инверсном выходе адресного формирователя. Выключающ йся в это время транзистор 7 не пре- 45 пятствует этому сбросу. По истечении времени установления напряжений в узлах схемы потенциал инверсного выхода

19 низкий, а прямого выхода 20 высОкий, Величина этОГО высОкОГО пО 5О тенциала определяется пороговым напряжением транзистора 9. Поэтому для него желательно значение порогового напряжения, близкое к нулю, при котором Он еще не прОводит и низкое зна- 55 чение коэффициента влияния подложки на пороговое напряжение. Отсутствие или малая величина сквозного тока, через транзисторы 7 или 9 и 8 или 10

14 6 позволяет увеличить проводимость этих TpBHçèñторов до величины, которую требует высокое быстродействие.

При этом почти не увеличивается нагрузка на управляющий транзистором инверторный каскад, поскольку одновременно с ростом напряжения на его затворе происходит возрастание напряже-, ния на его истоке. За счет работы в течение всего заряда в пологой области характеристики затвор имеет емкость только относительно истока (если не считать небольшую емкость в области стока за счет боковой диффузии). Но, несмотря на значительную величину этой емкости, в течение заряда разность потенциалов между ее электродами почти не изменяется, происходи лишь почти параллельное смещение их в сторону высоких значений. Транзистору 3 не требуется заряжать эту полную емкость затвора транзистора 9. Более того, при небольmoM первоначальном заряде затвора транзистора 9 он становится проводящим, напряжение на его истоке за счет этого возрастает, способствуя за счет .емкости затвор — исток повышению потенциала на затворе транзистора 9. По этой же причине не вызывает замедления заряда подключение к узлу 17 транзистора 12 обогащенного типа. Благодаря усилительным свойст-. вам MOII-.òðàíçèñòîðîâ управляющий разрядом выходного узла 20 транзистор ,10 при обеспечении высокой скорости разряда имеет величину входной емкости, намного меньшую емкости выходного узла 20.

По этой же причине управляющий разрядом затвора транзистора 10 транзистор 11 может иметь также намного меньшую входную емкость при обеспечении высокой скорости разряда, чем транзистор 10. Зта маленькая емкость затвора транзистора 11 в совершенно незначительной степени увеличивает нагрузку управляющего инверторного каскада. В практическом случае она может иметь в десять раз меньшее значение, чем у транзистора 10. Зто значительно снижает емкость, связанную с выходами управляющих инверторньщ каскадов, в большей степени увеличивая как скорость нарастания, так и скорость спада напряжения в них. Благодаря увеличению этой скорости управление инверторными каскадами выход1047314

Редактор Н.Сильнягина Техр ед М. Ходаннч Корректор Л. Пилипенко

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3384

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ных транзисторов становится значительно более быстродействующим, соответственно повышающим скорость переключения в выходных узлах адресного формирователя. Дополнительно введенные транзисторы обеспечивают благодаря их усилительным свойствам большую скорость переключения напряжений на затворах разряжающих выходные узлы транзисторов при размерах их каналов,. во много раз меньших размеров каналов этих выходных транзисторов. Их конкретные размеры могут отличаться более чем в десять раз. Это не только уменьшает нагрузку на управляющие инверторные каскады, увеличивая скорость переключения на их выходах, но и вызывает только малое увеличение площади кристалла, занимаемой такими адресными формирователями.