Способ контроля ттл интегральных схем

Иллюстрации

Показать всеРеферат

СПОСОБ КОНТРОЛЯ ТТЛ ИНТЕГР7и1ЬШХ ХЕМ, включающий измерение их статических параметров при номинальном напряжении питания, отличающийся тем, что, с целью упрощения контроля, производят измерение статических параилетров интегральных схем при напряжении питания в диапазоне 3,1 - 3,2 В, определяют разность значений статических параметров, измеренных при номи;нальном и пониженном напряжениях питания и сравнивают эту разность с зталонным значением. а с СП ОГ) о 00 СХЭ

сОюз сОВетских социАлистичасних

РЕСПУБЛИН

09) ((1) 3(51) 6 01 R 31 26 господа ств(-нный комитет ссср по дклдм изов куний и отнеьпий

И АВТОРСНОМУ СВИДЕТЕЛЬСТВУ (54) (57) СПОСОБ КОНТРОЛЯ ТТЛ ИНТЕ

ГРАЛЬНЫХ СХЕМ, включающий измерение их статических параметров при номинальном напряжении питания, отличающийся тем, что, с целью упрощения контроля, производят измерение статических параметров интегральных схем при напряжении пита ния в диапазоне 3,1 - 3,2 В, определяют разность значений статических параметров, измеренных при номинальном и пониженном напряжениях питания и сравнивают эту разность с эталонным значением. (21) 3425334/18- 21 (22) 14 ° 04.82 (46) 23.11 ° 83. Бюл. Р 43 (72) В.В. Макеев и 10.Н. Кузнецов (71) Московский институт электронной техники (53) 621.382.3(088.8) (56) 1. E(ectronics fetters, 1978 14 Р 14, с. 434.

2. Арапов В.Л., Федотов Я.A.

Испытания и исследования полупроводниковых приборов. М., Высшая .школа, 1975, с. 249-250.

У

% йЮ

ЮО

Ъ 70

% N а ю

° +o

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,:

1056088

30

40 числа отбракованных ИС для двух групп заведомо годных ИС и ИС со Скрытыми

Изобретение относится к контрольно-измерительной технике в микроэлектронике и предназначено для отбраковки дефектных TTJI интегральных схем,(ИС) с номинальным напряжением питания 5 В.

Известен способ контроля ИС по цепи питания, при котором подают номинальное напряжение питания одновременно на .контролируемую и опорную

ИС на их входы подают испытательный сигнал, а о годности контролируемой

ИС судят по отличию потребляемых по цепи питания токов контролируемой и опорной ИС (lj .

Недостатком этого способа является невозможность выявления ИС со скрытыми дефектами.

Наиболее близким по технической сущности к изобретению является способ контроля полупроводниковых .приборов, включающий помещение контролируемых ИС в термокамеры, задание повышенной н пониженной температур, выдержку в течение 30 мин, измерение при каждой температуре статических параметров при номинальном напряжении питания, вынесение решения о годности ИС на основании соответствия измеренных параметров, техническим условиям (2(.

Недостатком известного способа является его сложность, связанная . с необходимостью создания темпера- . турных режимов путем выдерживания

- контролируемых ИС в термокамере.

Целью изобретения является упрощение контроля ТТЛ ИС.

Поставленная цель достигается тем, что согласно способу контроля, TTJI ИС, включающему измерение их статических параметров при номинальном напряженки питания, производят измерение статических параметров HC при пониженном напряжении., питания в диапазоне 3,1 - 3,2 В, оп1 ределяют разность значений статичес ких параметров, измеренных при номинальном и пониженном напряжениях питания и сравнивают эту разность с эталонным значением.

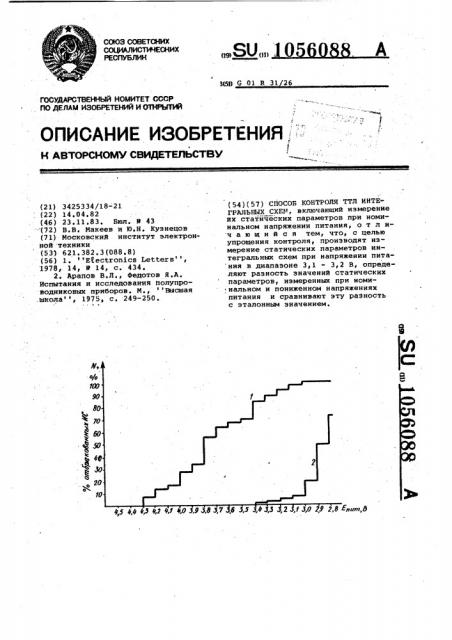

На чертеже приведены зависимости числа отбракованных ИС от величины пониженного напряжения питания (1 группа ИС годных при нормальной температуре, но из-за различных дефектов не удовлетворяющих требованиям

ТУ при крайних значениох рабочих температур (-60 и +125 С); 2 — груп- па ИС годных во всем диапазоне рабочих температур) .

В результате анализа отказов ИС при испытаниях и эксплуатации, а также анализа брака с различных контрольно-измерительных операций в производстве ИС выявлены основные виды дефектов, снижающих качество и надежность ИС. Для ТТЛ ИС наиболее 6 I часто встречающимися являются 4%факты, приводящие к утечкам между различными узлами схемы, Так при контроле ТТЛ ИС с сопротивлением утечки на подложку базы входного транзистора, равной 5 кОм, ее можно выявить лутем измерения напряжения логического нуля только при -6ООС. При более высоких температурах эта утечка не выявляется. При длительной эксплуатации вследствие протекания различных физико-химических процессов величина утечки по дефекту может меняться, что приводит к катастрофическому отказу. Поэтому такие утечки опасны с точки зрения надежности.

При уменьшении напряжения источника -питания резко повышается чувствительность выходных статических параметров ИС к внутрисхемным утечкам. С уменьшением напряжения питания увеличиваются критические величины сопротивлений утечек, приводящих к аномальным изменениям выходных параметров. При этом появляется воэможность при нормальной температуре отбраковывать ИС с дефектами, которые известными способами выявлялись лишь при изменениях температуры.

Теоретически минимальная величина напряжения питания, при которой

ТТЛ ИС еще Функционирует, составляет 2,8 В. Однако на практике, в силу разброса электрофизических параметров компонентов в пределах допусков, данная величина напряжения приводит к отбраковке большого количества годных ИС. Выбор величины пониженного напряжения питания произведен эмпирически. На чертеже показаны эмпирические распределения дефектами. При снижении напряжения питания увеличивается процент отбра- ковываемых дефектных схем. Однако при напряжении питания ниже 3,1 В начинают в значительном количестве браковаться и годные ИС. Оптимальн с точки зрения эффективности контроля и экономичности производства является диапазон 3,1 — 3,2 Ъ. Конкретное значение пониженного напряжения питания внутри данного диапазона зависит от требований ТУ, которые колеблются в зависимости от.типа

ИС, от допустимых значений риска поставщика и заказчика, от условий и целей производства.

При анализе значений выходных статических параметров годных и дефектных схем установлено, что оценку годности ИС целесообразно проводить по величине изменения параметра при изменении напряжения питания. Это дает возможность не браковать те ИС, у которых завышенные или заниженные абсолютные значения параметров,обус1056088

Составитель В. Карпов

Редактор Н. Рогулич Техред М.Костик Корректор Г. Решетник

Заказ 9294/37 Тираж 710 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 Раушская наб., д. 4/5

Филиал ППП Патент, r..Óæãîðîä, ул. Проектная, 4 ловленные не каким-либо дефектом, а получившимся соотношением электрофизических параметров компонентов, Такие ИС, не удовлетворяя по абсот лютной величине выходных статических параметров жестким требованиям метоперационного контроля, тем не менее могут отличаться хорошей стабильностью и нормально функционируют при различных режимах эксплуатации.

ДаннЫй способ опробируют в производстве биполярных ИС транзисторнотранзисторной логики при измерении выходных напряжений логического ноля и логической единицы.. При измерении статических параметров схем при комнатной температуре до разделения пластин на кристаллы измерение статических параметров проводят при двух величинах напряжения питания.

Сначала — при напряжении, равном

4,5 В, затем — при напряжении, pasном 3,2 В. При этом годными считают схемы, у которых разница выходных напряжений логического нуля измеренных при двух величинах напряжения питания не превышает 60 мВ, а разница выходных напряжений логической единицы не более 1 5 В.Например, если при питании 4,5 В выходное напряжение логического ноля равно 300 мВ, а при питании 3,2 В оно увеличивается до 340 мВ, то такая ИС считается годной. если увеличение составляет фолее 60 мВ и значение параметра равно, например, 380 мВ, то такая схема считается негодной. Аналогично для выходного напряжения логической единицы.

После разделения данных пластин на кристаллы, сборки кристаллов в корпусы и контроля статических параметров полученных схем при повышен.ной и пониженной температурах, т.е. при T=-60 С и при Т=+125 С выход годных при повышенной и пониженной температурах увеличивается по сравнению с текущей продукцией, контролируемой по известному способу, в среднем на 7,2%. Таким образом, )5 предлагаемый способ контроля нозволяет при комнатной температуре до разделения пластин на кристаллы отбраковывать ИС с низкой температурной стабильностью статических параметров.

Предлагаемый способ контроля ТТЛ

ИС проводят при комнатной температуре и может быть применен при контроле параметров схем до разделения пластин на кристаллы. Это позволит за счет отбраковки негодных схем на более раннем этапе технологического процесса избежать затрат,. связанных со сборкой этих схем в кор- пусы, а также с операциями нагрева и охлаждения ИС. Проведение контроля схем при двух напряжениях питания позволит также повысить качество выпускаемых ИС.