Суммирующее устройство

Иллюстрации

Показать всеРеферат

СУММИРУЮЩЕЕ УСТРОЙСТВО, содержащее ассоциативный запоминающий блок, первую группу элементов задержки и перву группу элементов И, первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, остальные разрядные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы - к соответствующим входам опроса первой группы ассоциативного . запоминающего блока, о т л и ч а. ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, суммирующее устройство содержит постоянный запоминающий блок, вторую группу элементов задержки, вторую и третью группы элементов И и элемент И, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства,а вторые входы - с второй шиной синхронизации , устройства, первый разрядный вьоход IS постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства ., а выход соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы (Соединены с первыми входами элелен- . Ю 05 тов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входаCD ми опроса третьей группы ассоциативного запоминающего блока.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) 3(59 (06 F 7 50

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

3 1 . ИАТЕйтйе- Ч

"- - НФ, уЯ;,ю, у Й

Н ABTGPCHOMY СВИДЕТЕЛЬСТВУ (21) 3502589/18-24 (22) 20.10.82 (46) 23.12.83. Бюл. !4 47 (72) 1 .И. Кукулиев, И.A. Айдемиров, Ш.-М.A. Исмаилов, О.Г. Кокаев

:и Т.Э. Темирханов (71). Дагестанский ордена Дружбы народов государственный универ.ситет им..В.И. )1енина и Дагестанский иолитехнический институт (53) 681.325.5 (088.8) (56) 1. Справочник по цифровой вычис.лительной технике. (электронные вычислительные машины и системы). Под ред. Б,Н. Малиновского . Киев, Техника, 1980, с. 65, рис. 2,4з °

2. Кохонен Т. Ассоциативная память. N. Мир, 1.980, с. 20, рис. 1.4 (прототип). (54) (57) СУММИРУМЦКЕ УСТРОИСТВО, содержащее ассоциативный запоминающий блок, первую группу элементов задержки и перву группу элементов И, первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, остальные разрядные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы — к соответствующим входам опроса первой группы ассоциативного запоминающего блока, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, суммирующее устройство содержит постоян ный запоминающий блок, вторую группу элементов задержки, вторую и третью группы элементов И и элемент

И, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства а вторые входы — c второй шиной синхронизации устройства, первый разрядный выход постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства, а выход соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с первыми входами элелен тов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входами опроса третьей группы ассоциатив" ного запоминающего блока.

1062б89

Изоьретение относится к вычислй" тельной технике и может использоваться в устройствах обработки цифровой информации.

Известно устройство, реализующее поразрядный способ суммирования нескольких чисел, содержащее ряды одноразрядных двоичных сумматоров, причем входы сумматоров каждого ряда соединены с выходами сумматоров предыдущего ряда (lj .

Недостатками устройства являются большой объем оборудования и неоднородность.

Известна также реализация автомата Nypa на ьазе ассоциатквной памяти,15 позволяющего осуществлять поразрядное суммирование нескольких чисел. Данное устройство содержит ассоциативное запоминающее устройство, первый выход которого является выходом суммы g0 устройства, разряды второго выхода ассоциативного запоминающего устрой" ства через первые элементы задержки соединены с первыми, вхоцами соответствующкх элементов И первой группы, вторые входы которых подключены к первок шине синхронизации устройства,. а B iõoäû - к соответствующим раз рядо ; первого входа опроса ассоциаткв;:арго запомкна|ощего устройства, разряд:. второго входа Которого соединены с входами слагаемых устройства (2) .

Недостатком устройства являются большие аппаратурные затраты, что в . ражается в большом объеме ассоцка35 тквного запоминающего устройства, раз. ряд 1ость пркзнаковой части которого равна в данном случае К + 0оО К, где

К вЂ” -исло слагаемых, а объем ассоциация:-1ок памяти равен 2 K слов. 4О

V. целью изобретения .является сокра-. щение аппаратурных затрат в суммирую1цсм чстройстве.

Поставленная цель достигается тем, ч.то суммирующее устройство, содержа- 45 щее аcc. îöèàòiiÿíèé запоминающий -блок, первую группу элементов задержки и первуо группу B3Icìåíòoâ И первык разрядник выход ассоциативного запомккаю цего блока является выходом суммы устройства, остальные разрядные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с :орвымк входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы — к соответствующим входам опроса парвой группы ассоциативного запоминающего блока, содержит также 60

I постоянный запоминающий блок, вторую,, группу элементов задержки, вторую и

1 третью группы элементов И и элемент

И, причем адресные входы постоянногО запоминающего блока соединены с выхо, 65 дами соответствующих элементов И второй группы, первые входы которых соответственно соединены с входами слагаемых устройства, а вторые входы— с второй шиной синхронизации устройства, первый разрядный выход постоянного запоминающего ьлока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства, а. выход соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы соединены с соответствующими входами опроса третьей группы ассоциативного запоминающего блока.

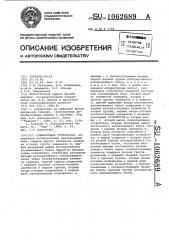

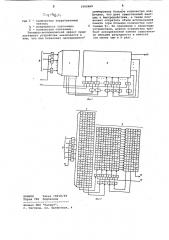

На фиг. 1 представлена структурная схема суммирующего устройства; на фиг. 2 — прошивка блоков 1 и 2 для случая суммирования пяти слагаемых. устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, группу элементов И 3, элемент И 4, группы элементов И 5 и б, группы элементов

7 и 8 задержки. На фиг. 1 также указаны информационные входы 9 устройства, выход 10 суммы, шины 11 и 12 синхронизации.

Устроиство работает следующим образом.

На информационные входы 9 устройства одновременно подаются одноименные разряды К слагаемых, которые в течение тактового импульса определяют адрес слова, считываемого из блока 1. Считанное кз блока 1 слово само является частью признака, подаваемого на пркзнаковые входы 2, причем все разряды, кроме младшего, задерживаются на один такт. Остальной часть признака являются все, кроме ста1 шего, разряды считываемые из блока 2 и задержанные на один такт.

Сформированный признак дополнительно синхронкзируется на элементах И

4 — 6.путем подачи сигнала по шине

12, передний фронт котрого начинается позже, а задний раньше тактового импульса, подаваемого по шине 11.

Эта мера вызвана неидеальностью элементов 7 и 8 задержки.

В том же такте, в котором был подан разрядный срез слагаемых, на ,выходе 10 ьлока 2 появляется одноименный выходной разряд. Таким образом, на выходе получается результат суммирования в последовательном. коде, причем количество тактов, за которое вычисляется сумма, равно

1062689 где - коли л чество затрачиваемых тактов; разрядность слагаемых;

К вЂ” количество слагаемых.

Т нико-экономический фф эффект предехни ст ойства заключается в лагаемого устр т одновременнотом, ом что оно позволяет одновре

Ouz.1

r 0

1 0

1 0 о

0 0

0

0 т в. в

1 т

Фиг 2

ВНИИПИ Заказ 10218/49

Тираж 706 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проек ктная 4

0

1

0

0

1

1 су ммировать большое коли чество опечто дает существенны ный выиг" рандов, также поэрыш в оыстродействии, а т воляет cî ократить объем используемой ла памяти при большом количестве сл

К,. По сравнению с известным ст ойство треустройством, данное устро б ет ассоциативной памят ущ и с ественует но меньшей разрядности и и емкости (не менее чем в К раз).