Приоритетное устройство для динамической памяти

Иллюстрации

Показать всеРеферат

ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ДИНАМИЧЕСКОЙ ПАМЯТИ, содержащее блок анализа запросов н регистр, причем входы запроса устройства являются входами блока анализа запросов , информационный вход регистра является кодовым входом устройства, о тли ч ающе е с я тем, что, с Целью повышения быстродействия, оно Содержит элемент И, счетчик. компаратор, генератор импульсов и элемент ИЛИ, причем выход элемента И соединен с суммирующим входом счетчика, выход счетчика соединен с первым входом компаратора, второй, вход которого соединен с выходом регистра , .выход компаратора соединен с первым входом элемента И, вто, рой вход которого соединен с выходом генератора импульсов, третий вход элемента И соединён с входом сброса счетчика и с последним входом запроса устройства, последний элемент И-НЕ блока анализа запросов соединен с первым входом элемента ИЛИ, второй вход элeмeнta ИЛИ соединен с выходом компаратора, выход элемента ИЛИ соединен с последними входсми элементов И-НЕ блока анализа запросов, кроме .последнего элемента И-НЕ,выходы блока ансшиза запросов являются выходами устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (12) 3(50 G 06 F 9/4

М

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3521164/18-24 (22)14.12.82 (46) 30.03.84. Бюл. Р 12 (72) В.A. Kóñòoâ, Р.М.Воробьев, Д.A.Áðóåâè÷ и A.Ã.Kóëèêîâ (53) 681.325(088 .8) (56) 1. Авторское свидетельство СССР по заявке Р 3342337/18-24, кл. G 06 F 9/46, 08.04.82 °

2. Авторское свидетельство СССР

Ю 879589, кл. 0 06 F 9/46, 1979 (прототип). (54)(57) ПРИОРИТЕТНОЕ УСТРОЙСТВО

ДЛЯ ДИНАМИЧЕСКОЙ ПРИЯТИ, содержащее блок анализа запросов и регистр, причем входы запроса устройства являются входами блока анализа запросов, информационный вход регистра является кодовым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит элемент И, счетчик, компаратор, генератор импульсов и элемент ИЛИ, причем выход элемента

И соединен с суммирующим входом счетчика, выход счетчика соединен с первым входом компаратора, второй: вход которого соединен с выходом регистра, выход компаратора соединен с первым входом элемеита И, вто-, рой вход которого соединен с выходом генератора импульсов, третий вход элемента И соединен с входом сброса счетчика и с последним входом запроса устройства, последний элемент

И-НЕ блока анализа запросов соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ соединен с выходом компаратора, выход элемента ИЛИ сое- Я динен с последними входами элементов

И-НЕ бЛока анализа запросов; кроме последнего элемента И-НЕ, выходы блока анализа запросов являются выходами устройства.

1083191

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления динамических запоминающих устройств, Известно многоканальное приоритетное устройство для динамической памяти, содержащее генератор импульсов, восемь элементов И-НЕ, три элемента задержки, два элемента ИЛИ, счетчик, триггер добавления единицы, три элемента НЕ, триггер срочной ре- 1О генерации, элемент И и в каждом канале два элемента И-НЕ, элемент задержки, элемент НЕ и триггер ответа..

В данном устройстве запросы на регенерацию, выцаваемые генератором импульсов, накапливаются в счетчике, откуда они поступают на обслуживание через младший по приоритету канал.

При значительной частоте обращений к памяти по другим каналам может произойти переполнение счетчика, в этом случае все накопленные запро,сы на регенерацию проходят на обслуживание через старший по приоритету канал Г13.

Недостатком укаэанного устройства является двухкратное увеличение числа циклов регенерации по сравнению с минимально необходимым, чro приводит к снижению быстродействия.

Наиболее близким по технической сущности к предлагаемому является приоритетное устройство, содержащее блок анализа запросов, элементы, И-НЕ и регистр Г23 °

В известном устройстве после при хода первого запроса по какому-либо каналу на соответствующих входах элементов И-НЕ остальных каналов воз никает низкий уровень напряжения, запрещающий прохождение других зап- )О росов к общему ресурсу. Если в качестве последнего используется динамическая память, то запросы на регенерацию следует подавать на вхоц перво го или второго по приоритету канала, 45 так как в противном случае восстанов. ление информации в заданное время не гарантируется. Это приводит к уве. личению времени обслуживания запросов по другим каналам и снижению быстродействия памяти в целом.

Цель изобретения — повышение быст родействия.

Поставленная цель достигается тем, что в приоритетное устройство для, . динамической памяти, содержащее блок анализа запросов и регистр, причем входы запроса устройства являются входами блока анализа запросов, информационный вход. регистра является кодовым входом устройства, введены 6О элемент И, счетчик, компаратор, гене ратор импульсов и элемент ИЛИ, причем выход элемента И соединен с сум мирулощим входом счетчика, выход ацутчйка соединен с первым входо 65 компаратора, второй вход которого соединен с выходом регистра, выход компаратора соединен с первым входоь элемента И, второй вход которого соединен с выходом генератора импульсов, третий вход элемента И соединен с входом сброса счетчика и с последним входом запроса устройства, последний элемент И-НЕ блока анализа запросов соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ соединен с выходом ком. паратора, выход элемента ИЛИ соединен с последними входами элементов

И-НЕ блока анализа запросов, кроме последнего элемента И-НЕ, выходы блока анализа запросов являются выходами устройства.

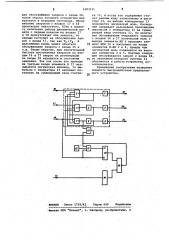

На чертеже представлена схема предлагаемого устройства.

Устройство содержит блок 1 анализа запросов, включающий элемент

И-НЕ 2, элемент НЕ 3, элемент И-НЕ 4, элемент 5 задержки, элемент HE 6, элемент И-НЕ 7, элемент 8 задержки и элемент HE 9. Устройство содержит также элемент ИЛИ 10, элемент И 11, счетчик 12, компаратор 13, регистр 14 и генератор 15 импульсов, запросные входы 16-18, выходы 19-21, кодовый вход 22 устройства.

Приоритетное устройство работает следующим образом.

В исходном состоянии запросы к динамической памяти по входам 16-18 отсутствуют и на этих входах находятся логические нули, на выходах элементов И-НЕ 2,4 и 7 и на выходах эле ментов 5 и 8 задержки — логические единицы, а на выходах 19-21 устройства — логические нули. Ноль с входа 18 устанавливает в ноль счетчик

12 и одновременно запрещает прохожде. ние на его суммирующий вход импульсов с генератора 15 через элемент

И 11, В регистре 14 по входу 22 запи сан код, определяющий максимальное время ожидания обслуживания запро» сов на регенерацию. В общем случае этот код ненулевой, поэтому на выходе компаратора 13 присутствует логическая единица, которая поступает на выход элемента ИЛИ 10.

Предположим, что на вход 16 устройства поступает запрос к динамической памяти. Тогда на всех четырех входах элемента И-HE 2 окажутся логи ческие единицы, а на его выходе— логический ноль ° Величины задержек элементов 5 и 8 и ь сравнимы с

8 задержкой распространения сигнала: через элементы И-НЕ и удовлетворяют соотношению Г8 > " . Поэтому логический ноль окажется на входах элементов И-НЕ 4 и 7 и запретит их срабатавание при возйожном поступлении запросов с входов 17 и 18. На выхо- де 19 установится единица, означаю1083191

I .ЯЯККПК Заказ 755/43 . Тираж 699 Подписное

;Филиал ППП "Патент", г. ужгород, ул.Проектная, 4 щая обслужиЭание запроса с входа 16, после сброса которого устройство возвратится в исходное состояние. Обслу. живание запросов с .входов 17 и 18 . происходит аналогично. Если к моменту окончания работы динамической памяти с первым каналом на входах 17 и 18 присутствуют оба запроса, то первым поступит на обслуживание запpqc с входа 17, так как Г (ie . В дальнейшем вновь может начаться обслуживание запроса с входа 16 и т.д. Таким образом, при значительной частоте поступления запросов по входам 16 и 17 запрос на регенерацию на входе 18 находится в состоянии ожидания. Так как после его прихода на третьем входе элемента И 11 ока- зывается логическая единица, то импульсы с генератора 15 начинают поступать на суммирующий вход счетчи- 0 ка 12, и когда его содержимое станет равным коду записанному в регистре 14, на выходе компаратора 13 появляется логический ноль. Последний запрещает дальнейшее прохождение импульсов с генератора 15 на суммирующий вход счетчика 12. По окончании обслуживания очередного запроса с входов 16 и 17 логический ноль с выхода элемента НЕ 6 проходит элемент ИЛИ 10 и поступает на входы элементов И-НЕ 2 и 4, прежде чем логический ноль появляется на выходах элементов 2 и 5. Поэтому следующим обслуживается запрос с входа 18, по окончании которого счетчик 12 обнуляется и работа устройства возобновляется.

Применение изобретения позволяет повысить быстродействие предлагаемого устройства.