Устройство для вычисления логических выражений @ переменных

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ П ПЕРЕМЕННЫХ, содержащее универсальный логический модуль, информационные входы которого подключены к tn информационным входам устройства () отличающееся , что, сцелью его упрощения, введены блок памяти, адресные входы которого подключены к (П -т) информационным входам устройства , выходы блока памяти подключены к 2 управляющим входам универсального логического модуля состЬетственно , выход которого является выходом устройства, входы записи и считывания блока памяти подключены к входам записи и считывания устройства соответственно. (Л с

СОЮЗ СОВЕТСКИХ

СО,Н ЛЮПФ

РЕСПУБЛИК

69) (111

ГОСУД СТВЕККЫй КОМИТЕТ СССР

tlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOIVIV СВИДЕТЕЛЬСТВУ

ЗЯ6 G 06 F 7/00

X 1 (21) 3404872/18-24 (22) 17.03.82 (46) 07.04.84. Вюл. 9 13 (72) В.Д.Козюминский, В.А.Мищенко и А.В.Гурьянов (53) 681.3(088.8) (56) 1. Якубайтис Э.А. Универсальные логические элементы. - Автоматика и

II вычислительная техника, 1973, В 5, с. 14.

2. Малев В.A.Ñòðóêòóðíàÿ избыточность в логических устройствах. М., Связь, 1978, с.124, рис.2.8 (прототип) ° (54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ и ПЕРЕМЕННЫХ содержащее универсальный логический модуль, информационные входы которого подключены к ln информационным входам устройства (tnt ) о т л и— ч а ю щ е е с я тем, что, с целью

его упрощения, введены блок памяти, адресные входы которого подключены к (и -m) информационным входам уст- ройства, выходы блока памяти подключены к 2 управляющим входам универtTl сального логического модуля соответственно, выход которого является выходом устройства, входы записи и считывания блока памяти подключены к входам записи и считывания устройства соответственно.

1084782

Изобретение относится к вычисли. тельной технике, предназначено для вычисления значения логической функ ции на входном наборе ее аргументов и может использоваться при построе, нии комбинационных узлов цифровых ав- 5 томатов.

Известно устройство, которое исйользуется для вычисления логических выражений, содержащее И информационных входов и 2п управляющих входов, б элементов НЕ, 26 элементов И и элемент ИЛИ, выход которого является выходом устройства, а его вхо» ды подключены к выходам элементов И, первые входы которых управляющие, а 15 остальные и входов каждого элемента

И подключены соответствующим образом к выходам элементов НЕ и информационным входам модуля..

Устройство путем настройки реа- 70 лиэует любые логические функции 0 переменных flJ .

Недостатком устройства является большая сложность.

Наиболее близким по технической 25 сущности к предлагаемому является устройство, которое имеет каскадную структуру и содержит 2 универсальных логических модулей, информацион ные входы которых подключены к (О -m) информационным входам устройства, а нх управляющие .входы являются управляющими входами устройства, выХЬды универсальных логических модулей подключены к входам. коммутатора, управляющие входы которого подключены к остальным и информационным входам модуля, выход коммутатора является выходом устройства (2g .

Недостатком известного устройства является его сложность, что не по- 40 зволяет использовать его при обработке многоразрядной информации.

Например, при П = 10 xN =5 и использовании универсальных логических модулей с двухъярусной канонической 45 структурой схема устройства имеет сложность, по Квайну равную 7590.

Целью изобретения является упро щение устройства для вычисления логических выражений.

50 . Поставленная цель достигается тем, что устройство для вычисления логических выражений rl переменных, содержащее универсальный логический модуль, информационные входы которого подключены к m информационным входам устройства (mcus)< содержит блок памяти, адресные входы которого подключены к (q -m) информационным входам устройства, выходы блока па- 60 мяти подключены к 2 и управляющим вхо дам универсального логического модуля соответственно, выход которого является выходом устройства, входы ,записи и считывания блока памяти иод- 65 ключены к входам записи и считывания устройства соответственно.

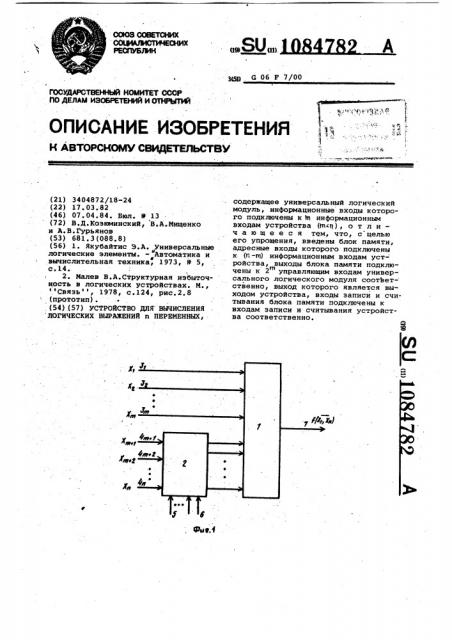

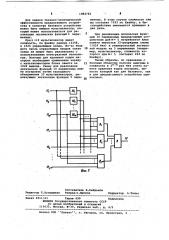

На фиг.l представлена схема устройства1 на фиг.2 - схема универ<ульного логического модуля.

Устройство содержит универсальный логический модуль 1, блок 2 памяти, группу Ф информационных входов 34 -3, группу (з-m) информационных вхоцов

4 в« -4э, входы 5 записи, входы 6 считывания, выход 7 устройства. Выход универсального логического модуля 1 подключен к выходу 7 устройства, информационные входы модуля 1 подключены к группе информационных входов

3 устройства, а управляющие входы модуля 1 подключены к информационным выходам блока 2 памяти, адресные входы которого подключены к группе уп- . равляющих входов устройства 4, входы записи и управления блока 2 памяти подключены к входам 5 и 6 устройства соответственно.

Универсальный логический модуль с двухъярусной канонической структурой (фиг.2) содержит 2 элементов И 8, элемент ИЛИ 9, Ф элементов

НЕ 10,щ информационных входов ll, 2" управляющих входов 12,выход 13

Устройство для вычисления логических выражений и переменных работает следующим образом.

В блок 2 памяти заносят 2" кодов настроек универсального логического

l модуля, Для универсального логического модуля с двухъярусной канонической структурой эти коды настроек сов. падают со значениями реализуемой логической функции на соответствующих наборах входных переменных. Для одной реализуемой функции емкость блока памяти составляет 2 бит. Для определения значения функции И переменных на некотором наборе входных переменных часть переменных (переменные Х„, Х,..., Хю) подается на информационные входы 3 -3 универсального логического модуля 1, а другая часть переменных (переменные Y, „,..., Х ) подается по входам 4,-4 д на адресные входы блока 2 памяти По сигналу считывания, подаваемому иа входы 6 блока памяти, производится считывание. кода настроек, который поступает с выходов блока памяти на управляющие входы универсального логического модуля. В результате универсальный логический модуль реализует логическую функцию m переменных, вид которой задается считанным из блока памяти кодом настройки. Значения этой логической функции соответствуют значениям реализуемой логической функции п переменных на заданном наборе входных переменных. Результат снимается с выхода 7 устройства.

1084782

Составитель В.Кайданов

Редактор Т.Кугрышева Техред C ..Легеэа Корректор: A.Òÿñêî

Заказ 2011/43 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушикая наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4

3 °, 4

Для оценки технико-экономической менных. В этом случае сложность схе эффективности предлагаемого устрой- мы составит 7392 по Квайну, а быства в качестве базового устройства стродействие уменьшится примерно в может. быть выбран мультиплексор, ко- два.раза. торый может использоваться для реализации логических функций tt пере- При реализации.логических функменных. ций 10 переменных предлагаемым устПри tl =10 мультиплексор имеет ройством для Ф= 5 потребуется блок сложность, по Квайну равную 12248, памяти емкостью 32-разрядных слова и 1024 управляющих входа. Иэ-эа боль. (1024 бит) и универсальный логичесщого числа управляющих входов такая 10 кнй модуль на 5 переменных (наприсхема не может быть реализована с мер, мультиплексор, сложность коиспользованием интегральной техноло- торого при ttl= 5 составит 224 по гии. Поэтому для хранения кодов на- Квайну). строек необходимо применение наряду . Таким образом, по сравнению с с мультиплексором блока памяти на )5 базовым объектом получен выигрыш в

1024 выхода. Схему для реализации сложности в 2" раз беэ учета палогических функций 10 переменных мож- мяти хранения кодов настроек., емно построить путем каскадного . кость которой как для базового, так объединения 33 мультиплексоров, ре- и для предлагаемого устройства одиализукщих логические функции 5 пере- наковая.