Сумматор

Иллюстрации

Показать всеРеферат

СУММАТОР на МДП-транзисторах , содержащий элемент ИЛИ-НЕ, первый , второй и третий входы которого подключены к соответствукядим входным шинам устройства, два повторителя, инвертор и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-НЕ, отличающийс я тем, что, с целью упрощения и повышения быстродействия, выход элемента .ИЛИ-НЕ подключен к входам первого и второго повторителей, выход первого повторителя подключен к входу инвертора , а выход второго - к второму входу элемента И-ИЛИ-НЕ, третий вход которого подключен к выходу инвертора , являющегося выходом перенос устройства, выход элемента Й-ИЛИ-НЕ является выходом сумма устройо to ства ,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (1I) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3540950/18-21 (22) 17.01.83 (46) 07.07.84. Бюл. Р 25 (72) A.Е. Бобров, A.Н.Горкунов, Г.Д. Дроздова, В.A. Журкин, С.Л. Кушнаренко, 3.Б. Иейдин и 10.А ° Шишкин (71) Ленинградский ордена Ленина институт инженеров железнодорожного транспорта им. акад. В.Н.Образцова (53) 621.374(088.8) (56) l. Сумматор F 4008/34008, M0S/CCD ДАТА ВООК, Fairchild Semiconductor, 1975, с.4-50. (54)(57) СУММАТОР на МДП-транзисторах, содержащий элемент ИЛИ-НЕ, первый второй и третий входы которого

3 (51) G 06 F 7/50; Н 03 K 19 094 подключены к соответствующим входным шинам устройства, два повторителя, инвертор и элемент И-ИЛИ-НЕ, первый вход Koi oðoão подключен к выходу элемента ИЛИ-НЕ, отличающийся тем, что, с целью упрощения и повышения быстрьдействия, выход элемента .ИЛИ-НЕ подключен к входам первого и второго повторителей, выход первого повторителя подключен к входу инвертора, а выход второго — к второму входу элемента И-ИЛИ-НЕ, третий вход которого подключен к выходу инвертора, являющегося выходом перенос устройства, выход элемента И-ИЛИ-HE является выходом сумма устройства.

110181 б

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки информации для реализации функций суммы и переноса трех двузначных слагаемйх.

Известен сумматор„ содержащий ллементы И-ИЛИ-НЕ, И-НЕ, ИСКЛ)ЮЧАРЖ!ЕЕ

ИЛИ, инвертор, четыре повторителя и два элемента ИЛИ-НЕ, входы первого элемента ИЛИ-НЕ и элемента И-НЕ подключены, соответственно, к первой и второй входным нинам устройства, выход первого элемента ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и к первому входу элемента И-ИЛИ-НЕ, выход которого через первый повторитель с инверсным входом подключен к выходу перенос устройства, а второй, третий и четвертый входы соответственно — к первой, второй и третьей входным шинам, выход элемента И-НЕ через второй повторитель с инверсным входом подключен к второму входу второго элемента

ИЛИ-НЕ, выход которого подключен к первому входу элемента ИСКЛ(ОЧА1011ЕЕ

ИЛИ, второй вход которого подключен через инвертор и третий повторитель с инверсным входом к третьей входной шине, а выход через четвертый повторитель с инверсным входом — к выходу сумма устройства (1).

Недостатком известного устройства является его сложность, а также низкое быстродействие из-за большого числа последовательно включенных элементов.

Белью изобретения является улро= щение и повышение быстродействия устройства.

Для достижения поставленной цели, э сумматоре на МДП-транзисторах, содержащем элемент ИЛИ-НЕ, первый, второй и третий входы которого подключены к соответствующим входным шинам устройства, два повторителя, лнвертор и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу элемента ИЛИ-НЕ, выход элемента

ИЛИ-HE подключен к входам первого и зторого повторителей, выход первого повторителя подключен к входу инвертора, а выход второго — к второму входу элемента И-ИЛИ-НЕ, третий вход которого подключен к выходу инвертора, являющегося, выходом перенос устройства, выход элемента И-ИЛИ-НЕ является выходом сумма устройства.

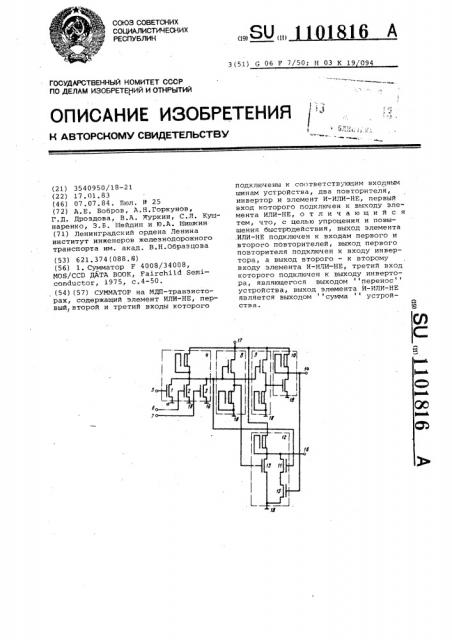

На чертеже представлена электрическая принципиальная схема сумматора на М11П-транзисторах.

Затворы ключевых МДП-транзисторов

1-3, элемента ИЛИ-НЕ 4 с многозначным выходоМ подключены соответственно к первой 5, второй б и третьей 7 входным шинам устройства, выход элемента ИЛИ-НЕ 4. подключен последовательно к выходам первого 8, и второго 9 повторителей (выход второго повторителя 9 подключен к входу инвертора 10) и к затвору ключевого МДПтранзистора 11 (первый вход элемента

И-ИЛИ-НЕ 12) . Последовательно с ключевым МДП-транзистором 11 включен

МДП-транзистор 13, затвор которого является вторым входом элемента

10 И-ИЛИ-НЕ 12 и подключен к выходу инвертора 10, выход которого является одновременно выходом 14 перенос устройства.

Параллельно МДП-транзисторам 11 и 13 включен ключевой МДП-транзистор

15, затвор которого, являющийся третьим входом элемента И-ИЛИ-НЕ 12, подключен к выходу повторителя 8.

Выход элемента И-ИЛИ-HE 12 является выходом 16 сумма устройства. Выводы питания всех элементов устройства подключены соответственно к к шине 17 питания и к общей шине 18.

Устройство работает следующим образом.

В зависимости от числа открытых ключевых МДП-транзисторов 1-3 элемента 4 (если устройство выполнено на и-канальных транзисторах, то в зависимости от числа единиц на вход30 ных шинах 5-7) напряжение на выходе элемента 4 принимает одно из четырех значен:rt (зйачность структурного алфавита равна четырем) . Размеры МДПтранзисторов 1-3 оди. аковы и выбраны так, что если скисло единиц на входе

N=- «0,1,2,3 >, то íà — ðÿæåíèå на выходе принимает значения Цз Ц 2 U1

Ug )р при этом . o с (1" (Цс Цлор Ц 3 — Е где Цп,р — пороговое напряжение МДП-транзистора с индуцированным каналом; Š— напряжение питания.

Соотношение между размерами нагрузочных и ключевых. транзисторов повторителей Ы и 9 выбрано так, что

45 напряжение на выходе повторителя 8 принимает значения с Ц, Ц, Ц,, Ц ), а на выходе повторителя 9 с Ц, Ц, Ц,>, где t. — напряжейие, величина которого больше, чем Ц

При этом на выходе инвертора 10

H соответственно на выходе 14 устройства реализуется функция переноса (Uo Ц от ц; Ц 3) в соответствии с количество.;: едийиц на входе (0,1,2,.3 ) . Уровень U< соответствует уровню напряжения логического нуля, а уровень U — уровню напряжения логической единицы.

Размеры нагрузочного и ключевых

МДП-транзисторов элемента И-ИЛИ-НЕ

12 выбраны таким образем, что когда открыт МДП-транзистор 15 или МДПтранзисторы 11 и 13, напряжение на выходе lб равно t) . При этом на выходе 1б реализуется функция сум1101816

Составитель Л.Петрова

ТехредИ. Асталош Корректор В.Синицкая

Редактор В.Данко

Заказ 4767/32

Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, М-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4 мы СП, U, U, U ) в соответствии с количеством едийиц на входе

N = (0,1,2,3> .

Для уменьшения потребляемой мощности и расширения диапазона представления многозначного сигнала нагрузочные транзисторы элементов устройства являются МДП-транзисторами со встроенным каналом, а ключевые транзисторы — МДП-транзисторами с индуцированным каналом. Сумматор имеет один выход "перенос",что сокраща- ет задержку формирования переноса при построении многораэрядньгс сум". маторов на 2, где "-среднее время перезаряда нагрузочной емкости через МДП-транзистор, при этом коли5 .чество МДП-транзисторов в каждом разряде устройства уменьшается на пять °

Таким образом, технико-экономический эффект изобретения заключается в

10 упрощении и повышении быстродействия устройства.