Усилитель считывания

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий переключающие транзисторы, резисторы , диоды, усилительный, управляющие и нагрузочные транзисторы, причем базы первого и второго переключающи.х транзисторов являются соответственно первым и вторым входами устройства, выходом которого является коллектор усилительного транзистора , эмиттеры переключающих транзисторов соединены с первым выводом первого резистора , а коллекторы подключены соответственно к базе первого управляющего и коллектору первого нагрузочного трназисторов и к базе второго управляющего и коллектору второго нагрузочного транзисторов, коллекторы первого и второго управляющих транзисторов соединены с шиной питания, а эмиттеры подключены соответственно к аноду первого и к аноду второго диодов, катоды которых соединены соответственно с базой первого нагрузочного транзистора и первым выводом второго резистора и с базой второго нагрузочного транзистора и первым выводом третьего резистора, второй вывод которого подключен к первому выводу четвертого резистора, базе усилительного транзистора , эмиттеру первого нагрузочного транзистора и коллектору третьего управляющего транзистора, база которого соединена с вторым выводом второго резистора и первым выводом пятого резистора, второй вывод которого подключен к щине нулевого потенциала , эмиттеру третьего управляющего транзистора, второму выводу четвертого резистора и эмиттеру усилительного транзистора , коллектор которого соединен с эмиттером второго нагрузочного транзистора, от® личающийся тем, что, с целью снижения потребляемой усилителем мощности, в него введены диоды с третьего по шестой, причем аноды третьего и пятого диодов соединены с вторы.м выводом первого резистора и щиной питания, а катоды - соответственно с анодами четвертого и щестого диодов, катоды которых подключены соответственно к базе первого и к базе второго переключающих транзисторов, при этом тип проводимости переключающих транзисторов противоположен типу проводимости усилительного, уп равляющих и нагрузочных транзисторов. сд 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК зсмк G 11 С 700

<7F (f

««t

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

54 1ы ьА

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3586482/18-24 (22) 29.04.83 (46) 23.07.84. Бюл. № 27 (72) И. В. Черняк и А. С. Попель (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР № 640365, кл. G 11 С 7/00, 1976.

2. Авторское свидетельство СССР № 617844, кл. Н 03 К 19/00, 1976 (прототип). (54) (57) УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий переключающие транзисторы, резисторы, диоды, усилительный, управляющие и нагрузочные транзисторы, причем базы первого и второго переключающих транзисторов являются соответственно первым и вторым входами устройства, выходом которого является коллектор усилительного транзистора, эмиттеры переключающих транзисторов соединены с первым выводом первого резистора, а коллекторы подключены соответственно к базе первого управляющего и коллектору первого нагрузочного трназисторов и к базе второго управляющего и коллектору второго нагрузочного транзисторов, коллекторы первого и второго управляющих транзисторов соединены с шиной питания, а эмиттеры подключены соответственно к аноду первого и к аноду второго диодов, катоды которых соединены соответствен но с базой

ÄÄSUÄÄ 1104581 A первого нагрузочного транзистора и первым выводом второго резистора и с базой второго нагрузочного транзистора и первым выводом третьего резистора, второй вывод которого подключен к первому выводу четвертого резистора, базе усилительного транзистора, эмиттеру первого нагрузочного транзистора и коллектору третьего управляющего транзистора, база которого соединена с вторым выводом второго резистора и первым выводом пятого резистора, второй вывод которого подключен к шине нулевого потенциала, эмиттеру третьего управляющего транзистора, второму выводу четвертого резистора и эмиттеру усилительного транзистора, коллектор которого соединен с эмиттером второго нагрузочного транзистора, отличаюи ийся тем, что, с целью снижения пот- ф ребляемой усилителем мощности, в него вве-,д дены диоды с третьего по шестой, причем аноды третьего и пятого диодов соединены с вторым выводом первого резистора и шиной питания, а катоды — соответственно с анодами четвертого и шестого диодов, катоды которых подключены соответственно к базе первого и к базе второго переключающих транзисторов, при этом тип проводимости переключающих транзисторов противоположен типу проводимости усилительного, управляющих и нагрузочных транзисторов. «Вь

1104581

Изобретение относится к вычислительной технике и может быть использовано в интегральных схемах запоминающих устройств в качестве усилителя считывания.

Известен усилитель который содержит дополнительно к основным каскадам цепь разрешения считывания для уменьшения потребляемой мощности (1).

Недостатком этого усилителя является

его сложность.

Наиболее близким техническим решением к изобретению является усилитель считывания, содержащий дифференциальный каскад, состоящий из первого и второго транзисторов, эмиттеры которых соединены между собой и через резистор подключены к шине нулевого потенциала, базы подключены к входам устройства, две аналогичные цепи, каждая из которых состоит из третьего транзистора, коллектор которого подключен к шине питания, а база упомянутого транзистора первой и второй цепи подключена к коллектору первого и второго транзистора дифференциального каскада соответственно, четвертого транизстора, коллектор которого соединен с базой третьего транзистора, эмиттер — с коллектором пятого транзистора, эмиттер которого подключен к общей шине, а база — к средней точке делителя напряжения, состоящего, например, из двух резисторов, который одним концом подключен к общей шине, а другим — к точке соединения базы четвертого транзистора и разделительного элемента, например диода, второй конец которого подключен к эмиттеру третьего транзистора, кроме того, коллектор пятого транзистора второй цепи подключен к выходу устройства, а база — к коллектору пятого транзистора первой цепи (2).

Недостатком известного усилителя является то, что при работе всегда одна из двух аналогичных цепей оказывается включенной и по цепи питания потребляется могцность.

Целью изобретения является снижение потребляемой усилителем мощности без существенного усложнения его и при сохранении высокого быстродействия.

Поставленная цель достигается тем, что в усилитель считывания, содержащий переключающие транзисторы, резисторы, диоды, усилительный, управляющие и нагрузочные транзисторы, причем базы первого и второго переключающих транзисторов являются соответственно первым и вторым входами устройства, выходом которого является коллектор усилительного транзистора, эмиттеры переключающих транзисторов соединены с первым выводом первого резистора, а коллекторы подключены соответственно к базе первого управляющего и коллектору первого нагрузочного транзисторов и к базе второго управляющего и коллектору второго нагрузочного транзисторов, коллекторы перS

ЗО

55 вого и второго управляющих транзисторов соединены с шиной питания, а эмиттеры подключены соответственно к аноду первого и к аноду второго диодов, катоды которых соединены соответственно с базой первого нагрузочного транзистора и первым выводом второго резистора и с базой второго нагрузочного транзистора и первым выводом третьего резистора, второй вывод которого подключен к первому выводу четвертого резистора, базе усилительного транзистора, эмиттеру первого нагрузочного транзистора и коллектору третьего управляющего транзистора, база которого соединена с вторым выводом второго резистора и первым выводом пятого резистора, второй вывод которого подключен к шине нулевого потенциала; эмиттеру третьего управляющего транзистора, второму выводу четвертого резистора и эмиттеру усилительного транзистора, коллектор которого соединен с эмиттером второго нагрузочного транзистора, введены диоды с третьего по шестой, причем аноды третьего и пятого диодов соединены с вторым выводом первого резистора и шиной питания, а катоды — соответственно с анодами четвертого и шестого диодов, катоды которых подключены соответственно к базе первого и к базе второго переключающих транзисторов, при этом тип проводимости переключающих транзисторов противоположен типу проводимости усил ительного, управляющих и нагрузочных транзисторов.

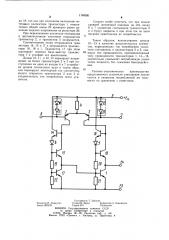

На чертеже представлена принципиальная схема предложенного усилителя считывания.

Усилитель считывания содержит усилительный транзистор 1, первый 2 и второй 3 переключающие транзисторы, первый резистор 4. На чертеже обозначены шина 5 питания, первый 6 и второй 7 входы усилителя. Усилитель содержит также диоды с первого по шестой 8 — 13, первый управляющий транзистор 14, первый нагрузочный транзистор 15, второй 16 и третий 17 управляющие транзисторы, второй нагрузочный транзистор 18, резисторы со второго по пятый !

9 — 22, общую шину 23 и выход 24.

Усилитель считывания работает следующим образом.

При поступлении на вход 6, например уровня логической единицы, а на вход 7— уровня логического нуля, транзистор 2 будет закрыт, а транзистор 3 — открыт. Соответственно с этим ток, протекающий в коллекторной цепи транзистора 3, вызовет открывание транзистора 16, эмиттерный ток которого, протекая по цепи, состоящей из диода 9 и резисторов 20 и 21, создает на резисторе. 21 напряжение, открывающее транзистор 1, коллектор которого подключен к выходу 24. Степень насыщения транзистора 1 ограничивается с помощью транзисто1104581

Составитель Т. Зайцева

Редактор Н. Данкулич Техред И. Верес Корректор А. Зимокосов

Заказ 5028/39 Тираж 575 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий! !3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ра 18, так как при описанном включении потенциал коллектора транзистора 1 относительно общей шины 23 примерно равен величине падения напряжения на резисторе 20.

При переключен ии усилителя считыва ния в противоположное состояние открывается транзистор 2, а транзистор 3 закрывается.

Соответственно этому открываются транзисторы 14, 15 и 17 и закрываются транзисторы 16, 18 и 1. Транзистор 17 при этом шунтирует переход база-эмиттер транзистора 1 и ускоряет его выключение.

Диоды 10, 11 и 12, 13 нормируют напряжение на базах транзисторов 2 и 3 при поступлении на один из входов 6 и 7 устройства уровня логического нуля и таким образом нормируют эмиттерный ток соответствующего открытого транзистора 2 или 3 и, следовательно, ток потребления всего усилителя.

Следует особо отметить, что при подаче уровней логической единицы на оба входа

6 и 7 усилителя считывания транзисторы 2 и 3 будут закрыты и при этом ток по цепи питания практически не потребляется.

Таким образом, использование диодов

10 — 13 в качестве разделительных элементов, нормирующих ток потребления- усилителя считывания, и транзисторов 2 и 3, име-!

О ющих тип проводимости, противоположный типу проводимости транзисторов 1, 14 — 18, значительно уменьшает потребляемую усилителем мощность без снижения быстродействия.

Технико-экономическое преимущество предложенного усилителя считывания заключается в снижении потребляемой им мощности по сравнению с известным.