Устройство для контроля сумматора

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СУММАТОРА, содержащее регистры первого и второго слагаемых, три блока формирования остатка по модулю |Y. , сумматор слагаемых, сумматор остатков , схему сравнения, причем информационные входы регистров первого и второго слагаемых являются соответственно входами первого и второго слагаемых устройства, выходы регистров первого и второго слагаемых соединены соответственно с первым и вторым информационными входами сумматора слагаемых и входами первого и второго блоков формирования остатка по модулю m , выходы которых соедийены соответстпенно с первым и вторым информацнояными входами сусумматора остатков, выходы которото соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами третьего блока формирования остатка по модулю т, входы которого соединены с выходами сумматора слагаемых , выход схемы сравнения является выходом ошибки устройства, отлиi чающееся тем, что, с целью повьш1ения достоверности контроля, в (Л него введена группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы сумма,тора слагаемых соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы,вторые входы которых объединены и соединены с выходом схемы сравнения, входом переноса сумматора слагаемых и управляющими входами регистров первого и второго слагаемых, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы являются выа ходами результата устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК <511 ?? 06 f 11>

f 3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOAIIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЬ1Й КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21). 3583168/18-24 (22) 25.04.83 (46) 30.08.84. Вюл. N 32 (72) M.Ã.Ëóêàøåâè÷, В.А.Остафин и А.Ф,Соловей (71) Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (53) 681. 3 (088 ° 8) (56) 1. Авторское свидетельство СССР

Ф 387362, кл. G 06 F 11/10,G06 F 7/38, t 970.

2. Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. M.,"Mèð", с. 144, фиг. 8. 1(прототип). (54) (57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

СУММАТОРА, содержащее регистры первого и второго слагаемых, три блока формирования остатка по модулю Ю., сумматор слагаемых, сумматор остатков, схему сравнения, причем информационные входы регистров первого и второго слагаемых являются соответственно входами первого и второго слагаемых устройства, выходы регистров первого и второго слагаемых соединены соответственно с первым и

„„SU„„1111167 . А вторым информационными входами сумматора слагаемых и входами первого и второго блоков формирования остатка по модулю pl выходы которых соедийены соответственно с первым и вторым информационными входами сусумматора остатков, выходы которо.го сбединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами третьего блока формирования остатка по модулю т, входы которого соединены с выходами сумматора слагаемых, выход схемы сравнения является выходом ошибки устройства, о т л ич а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введена группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы сумматора слагаемых соединены с первыми входами соответствующих элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых объединены и соединены с выходом схемы сравнения, входом переноса сумматора слагаемых и управляющими входами регистров первого и второго слагаемых, выходы элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы являются выходами результата устройства.

1111167

Изобретение относится к области вычислительной техники и может быть использовано в ЦВМ и устройствах обработки цифровой информации повы-. шенной надежности. 5

Известно арифметическое устройство с контролем и коррекцией ошибок, в котором для контроля логических операций производится сравнение результатов,полученных одновременно на сумматоре прямых значений кода и сумматоре инверсных значений кода, содержащее четыре регистра, четырнад«. цать групп вентилей прямой и инверсной передачи кодов, два сумматора, схему кодирования, схему сравнения, блок формирования признаков ошибок и блок сверток С11.

Недостатком указанного устройства является его сложность и невь1сокая достоверность контроля из-за большого количества контрольного обору" дования.

Наиболее близким по технической сущности к предлагаемому является

15 сумматор, контролируемый с помощью остаточного кода, содержащий два регистра слагаемых, выходы каждого из которых подключены к соответствующим входам сумматора слагаемых и соответственно к входам первого и второго блоков вычисления остатка по модулю vn, причем выходы первого и второго блоков вычисления остатка по модулю & подключены к входам сум- 35 матора остатков, выход которого подключен к первому входу схемы,сравнения, второй вход схемы сравнения соединен с выходом третьего блока вычисления остатка по модулю vn, 40 вход которого подключен к выходу сусумматора слагаемых, который является выходом результата сумматора, выход схемы сравнения является выходом ошибки сумматора. При m =3 в . " 45 сумматоре обнаруживаются все одиночные ошибки С21.

Недостатком данного устройства является невозможность корректирования результата при обнаружении ошибок.50

Цель изобретения повышение достоверности контроля.

Поставленная цель достигается тем, что В устройство для контроля сумма тора, содержащее регистры первого и второго слагаемых, три блока формирования остатка по модулю m,,сумматор слагаемых, сумматор остатков, схему сравнения, причем информационные входы регистров первого и второго слагаемых являются соответственно входами первого и второго. слагаемых устройства, выходы регистров первого и второго слагаемых соединены соответственно с первым и вторым информационными входами сумматора слагаемых и входами первого и второго блоков формирования остатка по модулю ь, выходы которых соединены соответственно с первым и вторым информационными входами сумматора остатков, выходы которого соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами трзтьего блока формирования остатка по модулю т, входы ко": торого соединены с выходами сумматора слагаемых, выход схемы сравнения является выходом ошибки устройства, введена группа элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ, причем выходы сумматора слагаемых соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ группы, вторые входы которых обьедииены и соединены с выходом схемы сравнения, входом переноса сумматора слагаемых и управляющими входами регистров первого и второго слагаемых, выходы элементов ИСКЛЮЧАЮЩЕЕ

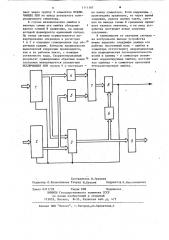

ИЛИ группы являются выходами результата устройства, На чертеже изображена функциональная схема устройства для контроля сумматора, который содержит регистр

1 первого слагаемого, регистр 2 второго слагаемого, сумматор 3 слагаемых, блоки 4-6 формирования остат-, ка по модулю ъ, сумматор 7 остатков, схему 8 сравнения, группу 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Информационные входы регистров

1,2 первого и второго слагаемых являются соответственно входами первого и второго слагаемых контролируемого сумматора, выходы регистров

1,2 соединены соответственно с первым и вторым входами сумматора 3 слагаемых и входами первого и второго блоков 4,5 формирования остатка но модулю hl., Выходы сумматора 3 слагаемых соединены с входами третьего блока 6 формирования остатка по модулю п и первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9, выходы которых являются выходом результата контролируемого Г

1111167 сумматора. Выходы блоков 4 и 5 соединены с соответствующими информационными входами сумматора 7 остатков.

Выходы сумматора 7 остатков и третьего блока 6 формирования остатка по модулю м соединены соответственно с первой и второй группами входов схемы 8 сравнения, выход которой является выходом ошибки контролируемого сумматора и соединен с вторы10 ми входами всех элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ, входом переноса сумматора 3 слагаемых и управляющими входами регистров 1,2.

Регистры 1 и 2 могут быть построены на триггерах со счетчным входом, подключенным к управляющему входу регистра, либо на Ь -триггерах и содержать элементы ИСКЛЮЧАЮШЕЕ ИЛИ, первые входы которых соединены с прямыми выходами разрядных триггеров, а вторые — с управляющим входом регистраь Схема 8 сравнения должна обладать внутренней задержкой на один такт, реализуемой на Ъ-триггерах.

Для обеспечения правильного корректирования ошибок необходимо,.чтобы отказы в схеме формирования суммы и переносов вызывали асимметричные 30

;ошибки, т.е. ошибки постоянного типа.

С этой целью сумматор 3 слагаемых, а также сумматор 7 остатков могут быть построены на элементах И, ИЛИ, НЕ, 35

При корректировании операции сложения используются следующие соотношения между прямыми и инверсными кодами операндов: А+А С, В+В=Сп, А и  — прямые -разрядные двоичные коды слагаемых; А,  — инверсные

И-разрядные двоичные коды слагаемых;

Си 11 ° ...1. Словим почленно первое и второе уравнения (А + В)

+ (А + В) = 2Cn. Так как 2С„=11...10, 45 и то, прибавив к левой и правой частям последнего равенства единицу, получим (А + В) + (А + В + 1) = Се+ где Ch+h = 11 1 1 .Отсуда c epyeò 50

ИМ что А + В = А + В + 1.

Указанное свойство используется . для корректирования ошибок в контролируемом сумматоре.

Ошибки, возникающие в сумматоре в результате неисправностей, вызваны неисправностью схемы формирования суммы или неисправностью схемы формирования переносов. Неисправность, возникающая в схеме формирования

i-го разряда суммы, приводит к одиночной ошибке типа S; = S, .

Поскольку неисправности в сумматоре вызывают. асимметричные ошибки, то после подачи на входы сумматора инверсных значений слагаемых на всех его выходах установятся инверсные значения вектора суммы, при этом разряд суммы с ошибкой совпадает с инверсным значением суммы в этом разряде т,. е. удовлетворяется зависимость Sion =$,. После инверсии значения суммы на входе блока управляемых инверторов устанавливается скорректированный прямой код резуль" тата суммирования.

Неисправность, возникающая в схе- ме формирования переноса ь, в зависимости от кода слагаемых может вызвать групповую ошибку в последующих разрядах. При этом Cion =С . Однако поскольку в сумматоре после подачи на его входы инверсных значений слагаемых вектор переноса инвертируется, то удовлетворяется условие

С щ.= с, следовательно, осуществляется коррекция указанной ошибки и не происходит ее распространения в стастаршие разряды. После инвертирования значения суммы на выходе устройства получаем скорректированный прямой код результата суммирования.

Следует отметить, что кратность корректируемых ошибок в контролируемом сумматоре определяется обнаруживающей способностью остаточного кода и при модуле ю =3 равна единице.

Устройство работает следующим образом. Слагаемые. с выходов регистров 1 и 2 поступают на соответствующие входы сумматора 3, а также на входы блоков 4,5 формирования остатка по модулю w . Соответствующие коды остатков с выходов блоков 4 и 5 поступают на вход сумматора 7 остатков. Блоком 6 формирования остатка по модулю Ф производится определение остатка по модулю ю суммы входных операндов. Схема 8 сравнения осуществляет сравнение кодов на выходах сумматора 7 и блока 6..

При правильном функционировании сумматора 3 на выходе схемы 8 сравнения вырабатывается нулевой сигнал, по которому код суммы операндов с выхода сумматора 3 без изменения посту1111167

Составитель В,Гречнев

Редактор О.Колесникова Техред М.Кузьма Корректор M.Максимишинец

Заказ 6311/39 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д, 4/5

Филиал ППП "Патент", г.Ужгород,ул.Проектная,4 пает через группу 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ на выход результата контролируемого сумматора.

В случае возникновения ошибки в векторе суммы эта ошибка обнаруживается схемой 8 сравнения, на выходе которой формируется единичный сигнал.

По этому сигналу осуществляется инвертирование операндов в регистрах

1 и 2 и операция суммирования над об--10 ратными кодами. Контроль правильности выполненной коррекции производится, как и на рабочем такте, с помощью остаточного кода. Скорректированный результат суммирования обратных кодов 1 слагаемых инвертируется элементами, ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9 и поступает— на выход сумматора. Если коррекция-..

I произведена правильно, то через время задержки, равное одному такту, сиг нал на выходе схемы 8 сравнения принимает нулевое значение, и на вход уст" ройства поступают новые значения слагаемых.

В зависимости от значения сигналана контрольном выходе устройства можно выделить следующие режимы его работы: постоянный нуль - ошибки в сумматоре отсутствуют; апериодическая или периодическая последовательность нулей и единиц — в сумматоре возникают корректируемые ошибки; постоянная единица — в сумматоре произошла некорректируемая ошибка.