Запоминающее устройство

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее рабочие и вспомогательный блоки памяти, элементы И, первую группу коммутаторов, сумматор, причем выходы рабочих блоков памяти соединены с входами первой группы входов коммутаторов первой группы, о тли чающееся тем, что, с целью повышения быстродействия устройства оно содержит вторую группу коммутаторов и схему сравнения, первый вход которого соединен с управляющими входами коммутаторов и является первым управлякицим входом устройства, второй вход схемы сравнения являетсявторым управлягацим входом устройства, выходы одних коммутаторов первой группы являются числовыми выходами первой группы входов устройства, а выходы других коммутаторов первой группы соединены с входами первой группы входов сумматора, входы второй группы входов которого, соединены с выходами элементов И, выходы сумматора являются числовыми выходами второй группы выходов устройства, входы первой группы входов элементов И соединены с выходами вспомогательного блока памяти, а входы второй группы входов - с выходом схемы сравнения , выходы коммутаторов второй группы соединены с входами Соответствующих рабочих блоков памяти, входы второй группы входов коммутаторов первой группы соединены с соответствующими вькодами рабочих блоков памяти , входы первой группы входов коммутаторов второй группы являются со- Q ответствующими адресными входами устройства, входы второй группы входов коммутаторов второй группы соединены to с соответствующими адресными входами 4 устройства, входы вспомогательного блока памяти соединены с входами вто00 00 рой группы входов коммутаторов второй группы.

СОКИ СОВЕТСНИХ

CtNHM

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21 ) 3630074/24-24 (22) 28.07.83 (46) 15.11.84. Бюл. У 42 (72) В.А.Шастин, В.П.Петровский и И.И.Клепиков .(53) 621.327.6(088.8) (56) 1. Авторское свидетельство СССР

В 953669, кл. G 11 С 29/00, 1981.

2. Авторское свидетельство СССР

У 936034, кл. G 11 С 29/00, 1980 (прототип) ° (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее рабочие и вспомогательный блоки памяти, элементы И, первую группу коммутаторов, сумматор, причем выходы рабочих блоков памяти соединены с входами первой группы входов коммутаторов первой группы, о тл и ч а ю щ е е с ятем, что, с целью повьпнения быстродействия устройства, оно содержит вторую группу коммутаторов и схему сравнения, первый вход которого соединен с управляющими входами коммутаторов и является первым управляющим входом устройства, второй вход схемы сравнения являетсявторым управляющим входом устройства, выходы одних коммутаторов первой груп„SU„„1124380 A (д) G 11 С 11/00 G 11 С 29/00 пы являются числовыми выходами первой группы входов устройства, а выходы других коммутаторов первой группы соединены с входами первой группы входов сумматора, входы второй группы входов которого- соединены с выходами элементов И, выходы сумматора являются числовыми выходами второй группы выходов устройства, входы первой группы входов элементов

И соединены с выходами вспомогательного блока памяти, а входы второй группы входов — с выходом схемы сравнения,. выходы коммутаторов второй группы соединены с входами соответствукицих рабочих блоков памяти, входы ф второй группы входов коммутаторов первой группы соединены с соответствующими выходами рабочих блоков памяти, входы первой группы входов коммутаторов второй группы являются соответствующими адресными входами уст- ройства, входы второй группы входов м ь коммутаторов второй группы соединены вы с соответствующими ацресными входами Я устройства, входы вспомогательного блока памяти соединены с входами вто- р рой группы входов коммутаторов вто- О1 рой группы.

1 11243

Изобретение относьтся к вычислительной технике и может бить использовано в многопрофессорных вычислительных системах в качестве постоянной памяти.

Известно запоминающее устройство, содержащее блоки памяти, коммутаторы, группы элементов И, схемы сравнения(1).

Недостаток известного устройства обусловлен низким быстродействием, fo обусловленным наличием конфликтов при одновременном обращении нескольких процессоров к одному блоку памяти.

Наиболее близким к изобретению является запоминающее устройство, содержащее рабочие и вспомогательный блоки памяти, сумматоры,. коммутаторы, элементы И (2).

Однако и данное устройство характеризуется низким быстродействием, обусловленным наличием конфликтов при одновременном обращении к одному блоку памяти нескольких процессоров.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что запоминающее устройство, содержа- щее рабочие и вспомогательный блоки

30 памяти, элементы И, первую группу коммутаторов, сумматор, причем выходы рабочих блоков памяти соединены с входами первой группы входов коммутаторов первой группы, дополнительно содержит вторую группу коммутато- З5 ров и схему сравнения, первый вход которой соединен с удравляющими входами коммутаторов и является первым управляющим входом устройства, вто 1 рой вход схемы сравнения является вторым управляющим входом устройства, выходы одних коммутаторов первой группы являются числовыми выходами первой группы входов устройства, а выходы других коммутаторов первой группы соединены с входами первой группы входов сумматора„ входы второй группы входов которого соединены с выходами элементов И, выходы сумматора являются числовыми выхода- 5О ми второй группы выходов устройства, входы первой группы входов. элементов

И соединены с выходами вспомогательного блока памяти, а входы второй группы входов -с выходом схемы срав" 55 нения, выходы коммутаторов второй группы соединены с входами соответствунхцих рабочих блоков памяти, вхо80 2 ды второй группы входов коммутаторов первой группы соединены с соответствующими выходами рабочих блоков памяти, входы первой группы входов коммутаторов второй группы являются соответствующими адресными входами устройства, входы второй группы входов коммутаторов второй группы соединены с соответствующими адресными входами устройства, входы вспомогательного блока памяти соединены с входами второй группы входов коммутаторов второй группы..

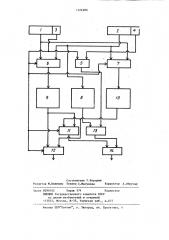

На чертеже представлена блок-схема предлагаемого устройства.

Запоминающее устройство подключается к регистрам 1 и 2 адреса, которые имеют дополнительные разряды 3 и 4, выходы которых подключаются соответственно к,первому и второму входам схем 5 сравнения и являются соответственно первым и вторым управляющим.входом устронства, коммутаторы

6 и 7 второй группы,.входы первой и второй групп которых соединены с соответствукщими выходами регистров

1 и 2 адреса и являются адресными входами устройства, вспомогательный блок 8 памяти, входы которого соединены с выходом регистра 2 адреса, рабочие блоки 9 и 10 п.=мяти, входы которых соединены с выходами соответствукицих коммутаторов 6 и 7, коммутаторы 11 и 12 первой группы, входы первой и второй группы которых соединены с соответствующими выходами рабочих блоков 9 и 10 памяти, элементы И 13, входы первой и второй групп которых соединены соответственно с выходами вспомогательного блока

8 памяти и схемы 5 сравнения, входы сумматора 14 соединены с соответствующими выходами коммутаторов 11 и элементов И 13, выходы коммутаторов

12 и сумматора 14 являются соответственно первыми и вторыми выходами устройства, управляющие входы коммутаторов 6,7, 11 и .12 соединены с дополнительным 3 разрядом регистра 1 адреса.

Устройство работает следующим образом.

При одновременном обращении к устройству ло двум каналам адреса требуемых ячеек записываются в соответствующие регистры 1 и 2 адреса.

В разряды 3 и 4 заносятся признаки обращения к первому 9 или второму 10 блокам памяти.

3 1124

Если обращение по первому регистру

1 адреса производится к первому блоку 9 памяти, а по второму регистру

2 адреса — к второму блоку 10 памяти "О" в разряде 3 регистра. 1 адреса и "1" в разряде 4 регистра 2 адреса, то через первые входы коммутатора 6 на адресные входы первого блока 9 памяти поступает информация первого регистра 1 адреса, а на ад- 10 ресные входы второго блока 10 памяти поступает через первые входы коммута-, тора 7 информация второго регистра 2 адреса. На адресные входы вспомогательного блока 8 памяти поступает ин- 15 формация с второго регистра 2 адреса. Информация из первого блока 9 памяти через первые входы коммутатора 12 поступает на первые выходы устройства.

Одновременно информация, считанная из второго блока 10 памяти, через первые входы коммутатора 11 поступает на первые входы сумматора

14.

Вследствие подачи на входы схемы

5 срав нения различной информации на ее выходе формируется сигнал, запрещающий прохождение через группу элементов И 13 на вторые входы сумматора 14 информации вспомогательного блока 8 памяти. При этом с выхода сумматора 14 на вторые выходы устройства выдается информация второго рабочего, блока 10 памяти.

Если производится одновременное об-З5 ращение к второму блоку 10 памяти, 380 . 4 го на выходе разряда 3 регистра 1 адреса появляется сигнал, вызывающий переключение коммутаторов 6, 7, 11 и 12; При этом на выходы данных коммутаторов поступает информация с вторых входов, а на выходе схемы 5 сравнения сформируется сигнал "Совпадение", разрешающий прохождение информации.с выходов вспомогательного блока 8 памяти на вторые входы сумматора 14. На первые выходы устройства с вторых входов коммутатора 12 посту пает информация, считанная as второго блока 10 памяти. Одновременно на вторые выходы устройства с выходов сумматора 14 поступает информация, рав« ная поразрядной сумме информации. соответствующих ячеек первого 9 и вспомогательного 8 блоков памяти которая равна требуемой информации (информации соответствующей ячейки второго блока 10 памяти), при.этом кон-. фликт.при обращении к устройству не возникает.

Аналогичным образом устройство работает и при других сочетаниях сигналов на разрядах 3 и 4 регистров 1 и 2 адреса,. а такке при обращении к устройству только по одному из регистров адреса (1 или 2).

Таким образом, использование изобретения. позволяет по сравнеHHIo с известными исключить возникновение конфликтных ситуаций при обращении к устройству и повысить его быстродействие;

1124380

Составитель Г.Бородин

Редактор М.Келемеш Техред С.Мигунова

Корректор А.Обручар

Подписное

Филиал ППП"Патент", г. Ужгород, ул. Проектная, 4

Заказ 8290/42 Тираж 574

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5