Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

1. РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее регистр адреса, один из выходов которого соединен с входами первого и второго рабочих и резервного блока памяти, первый и второй коммутаторы, информационные входы которых соединены с выходами соответствующих рабочих блоков памяти, а управляющие входы - с другим выходом регистра адреса, первый сумматор, одни из входов которого соединены с выходами резервного блока памяти, отличающееся тем, что, с целью повыщения надежности устройства. в него введены второй резервный блок памяти , первый и второй преобразователи кодов, третий коммутатор, второй и третий сумматоры и блок выборки информации, выходы которого являются выходами устройства, а входы соединены соответственно с выходами первого коммутатора,первого, второго и третьего сумматоров, другие входы первого сумматора соединены с выходами первого преобразователя кодов, входы которого соединены с выходами второго коммутатора и одним из входов второго сумматора, другие входы кото рого соединены с выходами третьего коммутатора и одними из входов третьего сумматора , другие входы которого соединены с выходами первого резервного блока памяти, входы которого соединены с входами второго резервного блока памяти, выходы которого (Л соединены с одними из входов третьего коммутатора и входами второго преобразователя кодов, выходы которого соединены с другими входами третьего коммутатора, управляющий вход которого соединен с другим вы ходом регистра адреса. ю со О5 ел 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (Н) 3 (5D

ОПИСАНИЕ ИЗОБРЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3637283/24-24 (22) 22,08.83 (46) 15.12.84. Бюл. № 46 (72) В. А. Шастин, В. П. Петровский и И. И. Клепиков (53) 681.327 (088.8) (56) 1. Авторское свидетельство СССР № 940241, кл. G 11 С 29)00, 1980.

2. Авторское свидетельство СССР № 881875, кл. G 11 С 29)00, 1979 (прототип). (54) (57) 1. РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮ1ЦЕЕ УСТРОЙСТВО, содержащее регистр адреса, один из выходов которого соединен с входами первого и второго рабочих и резервного блока памяти, первый и второй коммутаторы, информационные входы которых соединены с выходами соответствующих рабочих блоков памяти, а управляющие входы — с другим выходом регистра адреса, первый сумматор, одни из входов которого соединены с выходами резервного блока памяти, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй резервный блок памяти, первый и второй преобразователи кодов, третий коммутатор, второй и третий сумматоры и блок выборки информации, выходы которого являются выходами устройства, а входы соединены соответственно с выходами первого коммутатора, первого, второго и третьего сумматоров, другие входы первого сумматора соединены с выходами первого преобразователя кодов, входы которого соединены с выходами второго коммутатора и одним из входов второго сумматора, другие входы которого соединены с выходами третьего коммутатора и одними из входов третьего сумматора, другие входы которого соединены с выходами первого резервного блока памяти, входы которого соединены с входами второго резервного блока памяти, выходы которого соединены с одними из входов третьего коммутатора и входами второго преобразователя кодов, выходы которого соединены с другими входами третьего коммутатора, управляющий вход которого соединен с другим выходом регистра адреса.

1129658

2. Устройство по и. 1, отличающееся тем, что блок выборки информации содержит блоки сравнения с первого по третий, элемент

ИЛИ и четвертый коммутатор, выходы которого являются выходами блока, одни из информационных входов соединены с первыми входами блоков сравнения, вторые входы

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств высоконадежных вычислительных систем.

Известно резервированное запоминающее устройство с самоконтролем, содержащее дублированные блоки памяти, регистры адреса и числа, блоки аппаратурного контроля по модулю, коммутаторы, блок управления. В устройстве достоверность выдаваемой информации обеспечивается за счет использования блоков аппаратурного контроля по модулю и перехода на резервный блок памяти при обнаружении неисправности (1).

Недостаток известного устройства — невысокая достоверность выдаваемой информации вследствие низкой эффективности обнаружения неисправностей аппаратурным контролем по модулю.

Наиболее близким техническим решением к изобретению является резервированное запоминающее устройство, содержащее регистр адреса, один из разрядов которого служит для занесения признака обращения к первому или второму рабочим блокам памяти, резервный блок памяти, в который занесена сумма по модулю два информации с одинаковыми адресами из рабочих блоков памяти, первый и второй коммутаторы, информационные входы которых соединены с выходами рабочих блоков памяти, а управляющие входы — с выходом одного из разрядов регистра адреса, блок контроля по модулю, поразрядный сумматор, третий коммутатор, генератор тактовых импульсов, схему сравнения, группу элементов К (2).

К недостатку данного устройства следует отнести выдачу потребителю недостоверной информации при неисправности одного из рабочих блоков памяти (в случае необнаружения неисправности блоком аппаратурного контроля по модулю), что снижает надежность устройства.

Цель изобретения — повышение надежности устройства за счет увеличения достоверности выдаваемой информации.

Поставленная цель достигается тем, что в резервированное запоминающее устройсткоторых являются одним из входов блока, а выходы соединены с входами элемента

ИЛИ, выход которого соединен с управляющим входом четвертого коммутатора, другие информационные входы которого и второй вход первого блока сравнения являются другим входом блока. во, содержащее регистр адреса, одни из выходов которого соединены с входами первого и второго рабочих и резервного блоков памяти, первый и второй коммутаторы, информационные входы которых соединены с выходами соответствующих рабочих блоков памяти, а управляющие входы — с другим выходом регистра адреса, первый сумматор, одни из входов которого сое о динены с выходами резервного блока памяти, введены второй резервный блок памяти, первый и второй преобразователи кодов, третий коммутатор, второй и третий сумматоры и блок выборки информации, выходы которого являются выходами устройства, а вхо15 ды соединены соответственно с выходами первого коммутатора, первого, второго и третьего сумматоров, другие входы первого сумматора соединены с выходами первого преобразователя кодов, входы которого соединены с выходами второго коммутатора и одним из входов второго сумматора, другие входы которого соединены с выходами третьего коммутатора и одними из входов третьего сумматора, другие входы которого соединены с выходами первого резервного

25 блока памяти, входы которого соединены с входами второго резервного блока памяти, выходы которого соединены с одними из входов третьего коммутатора и входами второго преобразователя кодов, выходы которого соединены с другими входами третьего коммутатора, управляющий вход которого соединен с другим выходом регистра адреса.

Блок выборки информации содержит блоки сравнения с первого по третий, элемент ИЛИ и четвертый коммутатор, выходы которого являются выходами блока, одни из информационных входов соединены с первыми входами блоков сравнения, вторые входы которых являются одним из входов блока, а выходы соединены с входами эле40 мента ИЛИ, выход которого соединен с управляющим входом четвертого коммутатора, другие информационные входы которого и второй вход первого блока сравнения являются другим входом блока.

1129658

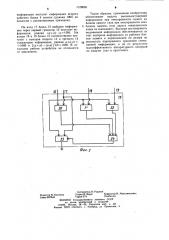

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 то же, блока выборки информации.

Устройство (фиг. 1) содержит регистр 1 адреса, один из разрядов 2 которого служит для занесения признака обращения к первому 3 или второму 4 рабочим блокам памяти, первый резервный блок 5 памяти, в который занесена информация, равная сумме кодов, содержащихся в одноименных ячейках первого 3 и второго 4 рабочих блоков памяти, второй резервный блок 6 памяти, в который занесена информация, равная разности кодов, содержащихся в одноименных ячейках первого 3 и второго 4 рабочих блоков памяти, первый коммутатор 7, первый преобразователь 8 кодов, второй коммутатор 9, третий коммутатор 10, второй преобразователь 11 кодов, первый 12, второй 13 и третий 14 сумматоры, блок 15 выборки информации, имеющий входы 16 — 19.

Блок 15 выборки информации (фиг. 2) содержит первый 20, второй 21 и третий 22 блоки сравнения, четвертый коммутатор 23, элемент ИЛИ 24.

Работа устройства происходит следующим образом.

Адрес ячейки к которой необходимо обратиться, записывается в регистр 1, в один из разрядов 2 которого заносится признак обращения к первому 3 или второму 4 рабочим блокам памяти.

Если обращение производится к первому рабочему блоку 3 памяти, то считанная с него информация (например, a) через первый коммутатор 7 поступит на вход 16 блока 15 выборки информации.

Одновременно на один вход первого сумматора 12 через второй коммутатор 9 и первый преобразователь 8 кодов поступит обратный код информации (например, в), содержащейся во втором рабочем блоке 4 памяти, на другой вход этого сумматора поступит информация из первого резервного блока 5 памяти, равная сумме кодов информации первого и второго рабочих блоков памяти (а+в). На один вход второго сумматора 13 через второй коммутатор 9 поступит информация в второго рабочего блока 4 памяти, на другой вход второго сумматора 13 поступит через третий коммутатор 10 информация из второго резервного блока 6 памяти, равная разности кодов одноименных ячеек первого 3 и второго 4 рабочих блоков памяти (a-в). На один вход третьего сумматора 14 поступит информация с выходов первого резервного блока 5 памяти (a+ s ), на другой вход третьего сумматора 14 поступит через третий коммутатор 10 информация с выходов второго резервного блока 6 памяти (а-в). При этом на вход 17 блока 15 выборки информации с выходов первого сумматора 12 поступит информация, равная: (а+в)-в=а. На вход

18 блока 15 выборки информации с выходов второго сумматора 13 поступит информация, равная: в+ (а-в)=а. На выходах, третьего сумматора 14 будет сформирована и нформация, равная: (a+ в) + (а-в) = 2а.

На вход 19 блока 15 выборки информации с выходов третьего сумматора 14 подается информация второго и последующих разрядов, т. е. результат суммирования деленный на 2 и равный а.

Так, например, если: а = 0101; в = 1000, то а+в=01101 (старший разряд знаковый); а — в =00101 + 1000 = 11100 (слагаемое в и результат сложения в обратном коде) .

При этом на выходах первого сумматора

12 будет сформирован код (а + в)-в= 01101

+ 10111 = 00101 (с учетом переноса из знакового разряда); на выходах второго сумматора 13 — код в+ (а — в) =01000+ 11100=

= 00101 (с учетом переноса из знакового разряда); на выходах третьего сумматора 1420 код: (а +в) + (а — в) = 01101 + 11100 =01010 (с учетом переноса из знакового разряда).

На вход 16 блока 15 выборки информации с выходов первого коммутатора 7 поступает код 0101. На вход 17 и 18 блока 15 с выZs ходов соответствующих сумматоров 12 и 13 поступают все разряды результата суммирования, за исключением старшего (знакового) разряда, т. е. код 0101. На вход 19 блока 15 с выходов третьего сумматора 14 подаются все разряды информации, за

ЗО исключением младшего разряда, т. е. код

0101.

Таким образом, на входы блоков 20, 21 и 22 сравнения и входы коммутатора 23 при отсутствии неисправностей в рабочих

3, 4 и резервных 5, 6 блоках памяти поступает одинаковая информация, равная информации выбранного (в данном случае первого 3) рабочего блока памяти. В случае сравнения информации, поступающей в блок

15 по входу 16, с информацией, поступаю4п щей по любому из других входов (17, 18 и 19), она считается достоверной и выдается через коммутатор 23 по управляющему сигналу с выхода элемента ИЛИ 24 на выход устройства.

В случае несравнения информации, пос4 тупающей по входу 16 блока 15, с информацией, поступающей по другим входам, с выхода элемента ИЛИ 24 на управляющий вход коммутатора 23 поступает сигнал, производящий переключение коммутатора 23. б При этом вместо неисправной информации с входов 16 на выходы устройства поступит информация с входов 17 блока 15 выборки информации, т. е. восстановленная информация.

Если обращение производится к второму рабочему блоку 4 памяти, то происходит переключение коммутаторов 7, 9, 10 и через коммутатор 7 на вход 16 блока 15 выборки

1129658

Составитель В. Рудаков

Техред И. Верес Корректор М. Макснмишинец

Тираж 574 Подйисное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор М. Келемеш

Заказ 8975 41 информации поступит информация. второго рабочего блока 4 памяти (равная 1000, по аналогии с рассмотренным примером).

На вход 17 блока 15 выборки информации через первый сумматор 12 поступит информация, равная (а+ в) — а = 1000. На входы 18 и 19 блока 15 соответственно поступит с выходов второго 13 и третьего 14 сумматоров информация, равная а-(а-a) =

= 1000 и ((a+ в) — (а- s) ) 1/2 = 1000. В остальном работа устройства не отличается от описанного.

Таким образом, применение изобретения обеспечивает выдачу высокодостоверной информации при неисправности одного из блоков памяти (или при неисправности всех

5 блоков памяти, если адреса отказавшихся ячеек не совпадают). Высокая достоверность выдаваемой информации обеспечивается за счет контроля информации из рабочих блоков памяти и переключения на резерв по результату поразрядного сравнения считываемой информации, а не по результату малоэффективного аппаратурного контроля по модулю (как в прототипе).