Усилитель считывания

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий первый и второй транзисторы , коллекторы которых подключены к шине питания, эмиттер первого транзистора подключен к аноду первого диода, третий и четвертый транзисторы, эмиттеры которых подключены к общей шине, база третьего транзистора подключена к средней точке первого резистивного делителя, I один яэ выводов которого подключен |к общей шиНе, коллектор четвертого транзистора подключен к выходной шине , а его база через резистор соединена с общей шиной, отличающийся тем, что с целью повышения быстродействия при включении и увеличения нагрузочной способности в состоянии логического нуля на выходе , в него введены с пятого по ВОСЬМОЙ транзисторы, тиристор и диоды, причем эмиттер пятого транзистора подключен к другому выводу первого резистивного делителя, коллектор подключен к катоду первого диода и резистору, второй вывод которого подключен к базе пятого транзистора и к аноду второго диода, катод которого подключен к коллектору третьего транзистора, анод тиристора подключен к эмиттеру второго транзистора и к резистору, второй вывод которого подключен к управляющему электроду тиристора и -к аноду третьего диода, катод которого подключен к кол хектору третьего транзистора , управляющий электрод тиристора соединен через цепь из последовательно включенных диодов с выi ходной шиной, катод тиристора соединен с общей шиной через второй резистивный делитель, средняя точW ка которого подключена к базе шестого транзистора, эмиттер которого соединен с общей шиной, а коллектор - с управляющ11М электродом тиристора и базой седьмого тразистора, эмиттер которого соединен через генератор тока с общей шиной и подключен к базе восьмого : го : транзистора, эмиттер которого подключен к базе четвертого транзистора , коллекторы седьмого и восьмого транзисторов подключены к шине питания , базы первого и второготранзисторов подключены к входным шинам .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 3(59 Н 03 .К 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕПЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ. ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3634234/24-21 (22) 09.08.83 (46) 30.12.84. Бюл. Р VB (72) М.О.Ботвиник, Ю.Н.Еремин, A.C.Ôåäoíèí и И.В.Черняк

f(53) 621,374(088.8), (56) 1. Патент Англии Р 1351037, кл. Н 3 Т, 1978.

2. Авторское свидетельство СССР

М 617844, кл. Н-03 К 19/092, 1977 (прототип). (54)(57) УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий первый и второй транзисторы, коллекторы которых подключены к шине питания, эмиттер первого ° транзистора подключен к аноду первого диода, третий. и четвертый транзисторы, эмиттеры которых подключены к общей шине, база третьего транзистора подключена к средней точке первого резистивного делителя, ;один из выводов которого подключен

,к общей шине, коллектор четвертого транзистора подключен к выходной шине, а его база через резистор соединена с общей шиной, о т л и ч а юшийся тем, что с целью повышения быстродействия при включении и увеличения нагрузочной способности в состоянии логического нуля на выходе, в него введены с пятого по восьмой транзисторы, тиристор и диоды, причем эмиттер пятого транзистора подключен к другому выводу первого резистивного делителя, коллектор подключен к катоду первого диода и резистору, второй вывод которого подключен к базе пятого транзистора и к аноду второго диода, катод которого подключен к коллектору третьего транзистора, анод тиристора подключен к эмиттеру второго транзистора и к резистору, второй вывод которого подключен к управляющему электроду тиристора и -к аноду третьего диода, катод которого подключен к коллектору третьего транзистора, управляющий электрод тиристора соединен через цепь из последовательно включенных диодов с выходной шиной, катод тиристора соединен с общей шиной через второй резистивный делитель, средняя точка которого подключена к базе шестого транзистора, эмиттер которого соединен с общей шиной, а коллектор — с управляющим электродом тиристора и базой седьмого тразистора, эмиттер которого соединен через генератор тока с общей шиной и подключен к базе восьмого транзистора, эмиттер которого подключен к базе четвертого транзистора, коллекторы седьмого и восьмого транзисторов подключены к шине питания, базы первого и второго транзисторов подключены к входным шияам.

1132364 Изобретение относится к импульсной технике, в частности к микроэлектронике, и может быть использовано в качествЕ усилителя считывания для запоминающих устройств.

Известен усилитель, в котором применены два охваченных обратными связями двухкаскадных выпрямителя, связь входов которых осуществляется через резисторы (1) .

Однако известный усилитель характеризуется высоким потреблением мощности и снижением скорости за счет уменьшения коэффициента передачи, Наиболее близким техническим решением к изобретению является

ТЛЭС-ТТЛ преобразователь, содержащий первый и второй транзисторы, базы которых подключены к входам устройства, коллекторы соединены с шиной пи- 20 тания через соответствующие резисторы, а эмиттеры объединены и соединены через резистор с общей шиной, и две аналогичные цепи, состоящие каждая из транзистора, подключенного ба- 75 зой к коллектору, соответственно первого или второго упомянутых транзисторов,эмиттеры транзисторов аналогичных цепей связаны с общей шиной через цепи из последовательно включенных диодов и резистивного делителя, к средней точке которого подключена база транзистора, эмиттером подключенного к общей шине, а коллектором к выходу для первой цепи и к базе выходного транзистора для второй цепи P2) .

Недостатком известного устройства. является то, что в цепи базы выходного транзистора включен резистор, ограничивающий быстродействие при 40 включении и нагрузочную способность в состоянии логического нуля на выходе.

Цель изобретения — повышение быстродействия при включении и повышение 45 нагрузочной способности в состоячии .логического нуля на выходе.

Укаэанная цель достигается тем, что в усилитель считывания, содержащий первый и второй транзисторы, кол. лекторы которыХ подключены к шине питания, эмиттер первого транзистора .подключен к аноду первого диода, третий и четвертый транзисторы, эмит-. теры которых подключены к общей шине, 55 база третьего транзистора подключена к средней точке первого реэистивного делителя, один иэ выводов которого подключен к общей шине, коллектор четвертого транзистора подключен 60 к выходной шине, а его база через резистор соединена с общей шиной, введены с пятого по восьмой транзисторы, тиристор и диоды, причем эмиттер пятого транзистора подключен к другому выводу первого резистивного делителя, коллектор подключен к катоду первого диода и к резистору, второй вывод которого подключен к базе пятого транзистора и к аноду второго диода, катод которого подключен к коллектору третьего транзистора, анод тиристора подключен к эмиттеру второго транзистора и к резистору, второй вывод которого подключен к управляющему электроду тиристора и к аноду третьего диода, катод которого подключен к коллектору третьего транзистора, управляющий электрод тиристора соединен через цепь из последовательно включенных диодов с выходной шиной, катод тиристора соединен с общей шиной через второй резистивный делитель, средняя точка которого подключена к базе шестого транзистора, эмиттер которого соеди нен с общей шиной, а коллектор — с управляющим электродом тиристора и базой седьмого транзистора,эмиттер которого соединен через генератор тока с общей шиной и подключен к базе восьмого транзистора,эмиттер которого подключен к базе четвертого транзистора, коллекторы седьмого и восьмого транзисторов подключены к шине питания, базы первого и второго транзисторов подключены к входньж шинам.

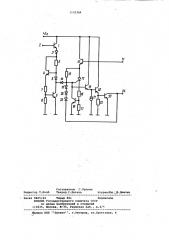

На чертеже изображен усилитель считывания.

Усилитель содержит транзистор 1, база которого подключена к входу 2, коллектор — к шине питания, а эмиттер — к аноду диода 3, катод которого подключен к коллектору транзистора 4 и к одному выводу резистора 5. . Второй вывод резистора 5 подключен к базе транзистора 4 и к аноду диода 6. Эмиттер транзистора 4 через . резистивный делитель иэ резисторов

7 и 8 соединен с общей шиной. К средней точке делителя подключена база транзистора 9, эмиттер которого подключен к общей шине, а коллектсрк катоду диода 6. Кроме того, в схеме имеется транзистор 10, коллектор которого подключен к шине питания, база — к входу 11, а эмиттер — к аноду тиристора 12 и резистору 13. Второй вывод резистора 13 подключен к управляющему электроду тиристора 12 и анодам диодов 14 и 15.

Катод диода подключен к коллектору транзистора 9. Катод тиристора 12 соединен с общей шиной через резистивный делитель из резисторов 16 и

17.

К средней точке делителя подключена база транзистора 18, эмиттер которого подключен к общей шине, а коллектор — к управляющему электроду тиристора 12 и к базе транзистора

19, коллектор которого подключен к

1132364 шине питания, а эмиттер — к базе транзистора 20 и соединен через источник тока 21 с общей шиной.Коллектор транзистора 20 подключен к шине питания, а эмиттер соединен с общей шиной через резистор 22 и подключен к базе транзистора 23. Эмиттер транзистора 23 подключен к общей шине, а коллектор — к выходу 24 и к катоду диода 25. Анод диода 25 подключен к катоду диода 26, анод которого подключен к катоду диода 15.

Устройство работает следующим образом.

Если на вход 2 подан низкий уровень напряжения, не превышающий ве- 15 личину 4 Ug где Ug — прямое падение напряжения на диоде, а на вход

11 подан высокий уровень напряжения, по величине близкий к напряжению питан .я, то транзистор 9 закрыт, так gp как входного напряжения недостаточно для отпирания транзисторов 1, 4 и 9 и диода 3.

Высокое напряжение на входе 11 приведет к отпиранию тиристора 12 через транзистор 10 и резистор 13.

Катодный ток тиристора 12 протекает через цепь из последовательно включенных резисторов 16 и 17 и включает транзистор 18, который осуществляет отрицательную обратную связь по току.

Таким образом, на управляющем элек" троде тиристора 12 устанавливается напряжение у . . g+, которое под (Ь 1

R3 „)

35 бором величины резисторов 16 и 17 устанавливается несколько большим величины 3(/g . Это напряжение привоводит к ускоренному включению транзисторов 19, 20 и 23, а следовательно, к повышению быстродействия при включении.

При включении транзистора 23 напряжение на его коллекторе снижается,, и когда оно снизится на величину, равную 3 0 по отношению к управляю- 45 щему электроду тиристора 12,включаются диоды 15, 26 и 25, осуществляя глубокую отрицательную обратную связь по току, охватывающую весь тракт ускоренного включения выходного транзис- 50

;тора 23.

На выходе 24 будет сформировано низкое напряжение логического нуля.

В случае роста нагрузочного тока в состоянии логического нуля на выходе 24 напряжение возрастет. Это приведет к повышению напряжения на управляющем электроде тиристора 12 и к увеличению базовых токов соответственно транзисторов 19, 20 и 23. Рост базового тока транзистора 23 приведет к увеличению его коллекторного тока и к снижению напряжения на его коллекторе до прежней величины. Таким образом, нагрузочная способность устройства в состоянии логического нуля на выходе существенно увеличивается, так как рост коллекторного тока транзистора 23 автоматически приводит к росту его базового тока.

При подаче на входы 2 и 11 обратных напряжений, т.е. на вход 2 высокого напряжения, а на вход 11 — низкого, транзисторы 1, 4 и 9 открываются через цепь из диода 3 и резисторов 5, 7 и 8. На коллекторе транзистора 9 сформировано напряжение, равное.

Uüý 1

Это напряжение выбирается примерно равным 1,5 0 . Через диод 14 на управляющий электрод тиристора 12 подается напряжение, примерно равное 2,5 Ugз . Отсутствие анодного питания и одновременное понижение напряжения на управляющем электроде приводит к быстрому включению тиристора 12 и к прекращению базового тока транзистора 19, который таким образом выключается, прекращая протекание базового тока транзистора 20.

Наличие источника тока 21 способствует более быстрому выключению транзистора 20 и прекращению базового тока транзистора 23. Наличие шунтирующего резистора 22 приводит к быстрому выключению транзистора

23.

Усилитель считывания применен в микросхеме памяти, что позволило повысить быстродействие при включении до 30 нс и обеспечить нагрузочную способность в состоянии логического нуля на выходе не менее 8 мА ,в рабочем диапазоне температур.

1132364

Составитель С.Пронин

Техред С.Легеэа

КоррекМЬр М.Демчик

Редактор Т.Колб филиал ППП . Патент, г.ужгород, ул.Проектная, 4

Закаэ 9805/44 Тира>к 861 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5