Четверичный сумматор

Иллюстрации

Показать всеРеферат

ЧЕТВЕРИЧНЫЙ СУММАТОР, содержащий три элемента РАВНОЗНАЧНОСТЬ и И, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с входом инверсного значений; младшего разряда первого слагаемого четвертичного сзпдаатора, второй вход соединен с входом прямого значения младшего разряда второго слагаемого, а третий вход с входом переноса четвертичного сумматора, входы второго элемента РАВНОЗНАЧНОСТЬ соединены соответственно с входом прямого значения старшего разряда первого слагаемого и с входом инверсного значения старшего разряда второго слагаемого четвертичного сз№Я4атора, а выход соединен с первым входом элемента И, первый вход третьего элемента РАВНОЗНАЧЮСТЬ соединен с входом Ефямого значения младшего разряда первого слагаемого четвертичного сумматора, отличающ и и с я тем, что, с целью упрощения , он дополнительно содержит три сумматора по модулю два, причем второй и третий входы третьего элемента РАВНОЗНАЧНОСТЬ соединены с входами инверсного значения старшего разряда первого слагаемого и прямого значения старшего разряда второго слагаемого четвертичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с перBbJM входом первого сумматора по модулю два и с вторал входом элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторьм входом первого сумматора по модулю два, третий вход которого соединен с входом прямого значения старшего разряда первого слагаемого четвертичного сумматора, а выход подключен к вЕлходу младшего разряда суммы четвертичного с матора, входы второго сумматора по модулю два соединегал соответственно с входами значений младшего разряда второго слагаемого и переноса 4 СО lN9 4 четвертичного сумматора, выход второго сзгмматора по модулю два соединен с выходом старшего разряда суммы четвертичного сумматора, выход элемента И соединен с первьм входе третьего сумматора по модулю два, второй вход которого подключен к выходу третьего элeмeнta РАВНОЗНАЧНОСТЬ , а третий вход соединен с входом прямого значения старшего разряда первого слагаемого четвертичного сумматора, выход третьего сумматора по модулю два соединен с выходом переноса четвертичного сумматора.

„„SU„„1149247 A

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУВЛИН

qeg с о6 Р 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и отнРытий (21) 3624978/24-24 (22) 39.07.83 (46} 07 04.85. Нюл. (72) А.П. Кириллов, А.И. Аспидов, С.Н. Огороднов и В.Т. Селетников (53) 681.325.5(088.8) (56) 1. Авторское свидетельство по заявке В 3603435!24, кл. G 06 Р 7/50, 3983.

2. Авторское свидетельство СССР

5 1023322, кл. 6 06 Р 7/50, 3981 (прототип). (54)(57) ЧЕТВЕРИЧНЦЯ СУИИАТОР, содержащий три элемен а РАВНОЗНАЧНОСТЬ и элемент И, причем первый вход первого элемекта РАВНОЗНАЧНОСТЬ соединен с входои инверсного значения младшего разряда первого слагаемого четвертичного сумматора, второй вход соединен с входом прямого значения младшего разряда вто- рого слагаемого, а третий входс входои перекоса четвертичного сумматора, входы второго элемента

РАВНОЗНАЧНОСТЬ соединены соответственно с входом прямого значения старшего разряда первого слагаемого и с входом инверсного значения старшего разряда второго слагаемого четвертичного сумматора, а выход соединен с первым входом элемента И, первый вход трегьего элемента РАВНОЗНАЧНОСТЬ соединен c sxoдои прямого значения младшего разряда первого слагаемого четвертичного суииатора, о т л и ч а юшийся тем, что, с целью упрощения, он дополнительно содержит три сумматора по модулю два, причем второй и третий входы третьего элемента РАВНОЗНАЧНОСТЬ соединены с входами инверсного значения старmего разряда первого слагаемого и прямого значения старшего разряда второго слагаемого четвертичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом первого сумматора по модулю два и с вторьм входом элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторьаа входом первого сумматора по модулю два, третий вход которого соединен с O входом прямого значения старшего разряда первого слагаемого четвертичного сумматора, а выход подключен к выходу младшего разряда суммы четвертичного сумматора, входы второго сумматора по модулю два соединены соответственно с входами прямых значений младшего разряда второго слагаемого и переноса р четвертичного сумматора, выход второго сумматора по модулю два соединен с выходом старшего разряда сум- © мы четвертичного сумматора, выход элемента И соединен с первым входом третьего суиматора по модулю два, второй вход которого подключен к выходу третьего элемента РАВНОЗНАЧНОСТЬ, а третий вход соединен с входом прямого значения старшего . В разряда первого слагаемого четвертичного сумматора, выход третьего сумматора по иодулю два соединен с выходом переноса четвертичного сумматора.

1 f 49247

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки цифровой информации.

Известен четвертичный сумматор, содержащий семнадцать элементов

РАВНОЗНАЧНОСТЬ и осуществляюпий сложение двух двухразрядных чисел (t j.

Недостатком сумматора является сложность конструкции.

Наиболее близким к предлагаемому по технической сущности является четвертичный сумматор, содержащий три элемента РАВНОЗНАЧНОСТЬ и элемент И, причем первый вход первого элемента РАВНОЗНАЧНОСТЬ соединен с входом инверсного значения млад"

mего разряда первого слагаемого четвертичного сумматора, второй вход соединен с входом прямого значения младшего разряда второго слагаемого, а третий вход - с входом переноса четвертичного сумматора, входы. второго элемента РАВНОЗНАЧНОСТЬ соединены соответственно с входом прямого значения старшего разряда первого слагаемого и с входом инверсного значения старшего разряда второго слагаемого четвертичного сумматора,;а выход соединен с первым входом элемента И, первый вход третьего элемента РАВНОЗНАЧНОСТЬ . соединен с входом прямого значения младшего разряда, первого слагаемого четвертичного сумматора.

Сумматор содержит также дополнительно восемь элементов РАВНОЗНАЧНОСТЬ и четыре элемента И „2).

Недостатком известного сумматора является сложность конструкции, выражающаяся в большом числе логических элементов.

Цель изобретения - упрощение четвернчного> сумматора«

Поставленная цель достигается тем, что четверичный сумматор, со" держащий три элемента РАВНОЗНАЧ-

НОСТЬ и элемент И, причем первый . вход первого элемента РАВНОЗНАЧНОСТЬ соединен с входом инверсного зна" чения младшего разряда первого слагаемого четвертичного сумматора, второй вход соединен с входом прямого значения младшего разряда второго слагаемого, а третий вход — с входом переноса четвертичного сумматора, входы второго элемента

РАВНОЗНАЧНОСТЬ соединены аоответстИ

И

2S

5О

55 венно с входом прямого значения старшего разряда первого слагаемого и со входом инверсного значения старшего разряда второго слагаемого четвертичного сумматора, а выход соединен с первым входом элемента И, первый вход третьего элемента РАВНОЗНАЧНОСТЬ соединен с входом прямого значения младшего разряда первого слагаемого четвертичного сумматора, дополнительно содержит три сумматора rro модулю два, причем второй и третий входы третьего элемента РАВНОЗНАЧНОСТЬ соединены с входами инверсного значения старmего разряда первого слагаемого н прямого значения старшего разряда.второго слагаемого четвертичного сумматора, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом первого сумматора по модулю два и с вторьм входом элемента И, выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторым входом первого сумматора по модулю два, третий вход которого соединен с входом прямого значения старшего разряда первого слагаемого четвертичного сумматора, а выход подключен к выходу младшего разряда суммы четвертичного сумматора, входы второго сумматора по модулю два соединены соответственно с входами прямых значений младmего разряда первого слагаемого, младшего разряда второго слагаемого и переноса четвертичного сумматора, выход второго сумматора по модулю два соединен с выходом старmего разряда суммы четвертичного сумматора, выход элемента И соединен е первым входом третьего сумматора но модулю два, второй вход которого подключен к выходу третьего элемента РАВНОЗНАЧНОСТЬ, а третий вход соединен с входом прямого значения старшего разряда первого слагаемого четвертичного сумматора, выход третьего сумматора по модулю два соединен с выходом переноса четвертичного сумматора.

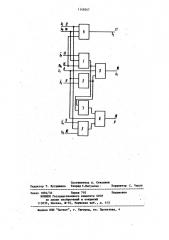

На чертеже представлена Функциональная схема четверичность сумматора.

Сумматор содержит элементы

РАВНОЗНАЧНОСТЬ t-З, сумматоры по модулю два 4-6 и элемент И 7. На

149247 4

Выходы 16 и 17 являются соответственно выходами старшего и младшего разрядов суммы, а выход 18 — выходом переноса.

В таблице представлены следующие значения: Х и Х вЂ” значения стар3 1 3

mH< разрядов Х и Х+ — младших разрядов первого и второго слагаемых, $„и S — значения старшего

30 и младшего разрядов суммы, à Pпереноса.

3 1 входы 8 и 9 поступают прямое и инверсное значения старшего разряда первого слагаемого, на входы 10 и

11 — прямое и инверсное значения старшего разряда второго слагаемого, на входы 12 и 13 — прямое н инверсное значения младшего разряда первого слагаемого, на вход 14— прямое значение младшего разряда второго слагаемого, на вход 15— прямое значение входного переноса.

t11t 1111

1111 t111

Х, ÎÎÎÎ ÎÎÎÎ ОООО ОООО 1111

1111- 0000 0000

ОООО 1111 OOOO

0011 0011 0011 0011 0011

0101

0101 0101 0101 0101

S 0001 1110 0111 1000 1110 0001 1000 0111

S 0110 Ît 10 1001 1001 01 10 Î110 t001 100t

Р 0000 0001 0000 Îf 11 0001 1111 0111 1111

По сравнению с известивши предлагаемый сумматор содервит вдвое меньшее количество логических элементов. Кроме того, он обладает меньшей задержкой формирования суммы, 3S

Х 0000 ОООО 1111

ХЗ 0000 f111 0000 х 00t 1 0о11 0011

P „0101 0101 0101 которая составляет и, где t- srL-- дернка элемента типа РАВНОЗНАЧНО-.

СТЬ > тогда как у известного сумматора эта задержка составляет Зi

1149247

Подписное

Закае 1894/34 Тираа 73Î

ВНИИПИ Государствеимого комитета СССР по делам изобретений и открытий

3t3035, Москва, %-35, Рауискаа иаб., д. 4/5 филиал ППП "Патент", г. Узйчзрод, ул. Проектная, 4

Составитель А. Степанов

Редактор Т.. Kyrpaaaesa Техред С.Мигунова i Корректор С, Черни.4