Устройство для выборки информации из блоков памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДПЯ ВЫБОРКИ ИНФОРМАЦИИ ИЗ БЛОКОВ ПАМЯТИi содержащее ключевые элементы на ЩЩ-транзисторах, причем стоки первого и второго транзисторов первого типа проводимости соединены с истоками соответственно третьего и четвертого транзисторов дополняющего типа проводимости и являются первыми и вторыми выходами устройства, стоки третьего и четвертого транзисторов являются разрядными выходами устройства, затворы третьего и четвертого транзисторов объединены и являются адресным входом устройства, затворы первого и второго транзисторов являются первым и вторым входами записи устройства , а истоки первогс и второго транзисторов объединены, отличающееся тем, что, с целью снижения потребляемой мощности, в устро.йство введены инвертор на дополняющих МДП-транзисторах, включенных между общей шиной и шиной питания, затворы которых подключены к адресном входу устройства , и дополнительный ключевой эле (Л мент на МДП-транзисторе, исток которого подключен к общей шинеу затвор - к объединенным стокам дополнякпцих МДП-транзисторов, а стокк объединенным истокам первого и второго транзисторов.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

53357 А (19) SU(I() 4(5(1 G 11 С Э 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ. И ОТНРЫТИЙ (21) 3699440/24-24 (22) 09.02.84 (46) 30.04.84. Бюл. Р 16 (72) В.В.Баранов,П.Б.Поплевин, Э.П.Савостьянов, Д.М.Барановский и С.В.Проворов (53) 681. 327, 6 (088. 8) (56) Патент CUIA У 4 91951, кл. 365-203, опублик. 1978. Авторское свидетельство СССР

У 1014029, кл. G 11 С 7/00,1983. (54)(57) УСТРОЙСТВО ДЛЯ ВЫБОРКИ

ИНфОРИАЦИИ ИЗ БЛОКОВ ПАМЯТИ, содержащее ключевые элементы на

: ИДП-транзисторах, причем стоки перного и второго транзисторов первого типа проводимости соединены с истоками соответственно третьего и -четвертого транзисторов дополняющего типа проводимости и являются первыми и вторыми выходами устройства, стоки третьего и четвертого транзисторов являются разрядными выходами устройства, затворы третьего и четвертого транзисторов объединены и являются адресным входом устройства, затворы первого и второго транзисторов являются первым и BTOpbM входами записи устройства, а истоки первого и второго транзисторов объединены, о т л и— ч а ю щ е е с я тем, что, с целью снижения потребляемой мощности, в устройство введены инвертор иа дополняющих МДП-транзисторах, включенных между общей шиной и шиной питания, затворы которых подключены к адресному входу устройст ва, и дополнительный ключевой элемент на ИДП-транзисторе., исток которого подключен к общей шине,: затвор — к объединенным стокам дополняющих МДП-транзисторов, а стокк объединенным истокам первого и второго транзисторов.

115335

Изобретение относится к электронной технике и может быть использовано при построении микромощных интегральных схем запоминающих устройств на дополняющих .МДП- 5 транзисторах.

Цель изобретения — снижение потребляемой мощности устройства.

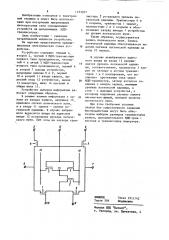

На чертеже представлена принципиальная электрическая схема уст- 10 ройства.

Устройство содержит первый 1, второй 2, третий 3 МДП-транзисторы первого типа проводимости, четвертый 4 и пятый 5 МДП-транзисторы второго типа проводимости, первый 6 и второй 7 выходы устройства, разрядные выходы 8 и 9, первый

lO и второй 11 входы записи, ад— ресный вход 12 устройства, выход

13 инвертора, шину 14 питания и общую шину 15, Устройство выборки информации работает следующим образом.

В режиме записи информации к од— ному из входов записи, например 10, приложен сигнал логического нуля, а к входу 11 записи — сигнал логической единицы. В случае выбранного адресного входа на адресном входе 12 установлен уровень логиче1 ского нуля. При этом на затворе тран7 1 зистора 3 установлен уровень логической единицы, Транзисторы 4 и

5 открыты, транзистор 1 закрыт л транзисторы 2 и 3 открыты и обеспечивают разряд выхода 7 устройства до уровня логического нуля.

Таким образом, осуществляется запись логического нуля. Запись логической единицы обеспечивается подачей сигнала логической единицы на вход 10 записи.

В случае невыбранного адресного входа на входе 12 удерживается уровень логической единицы, соответственно, транзистор 3 закрыт по затвору и истоки транзисторов 1 и 2 изолированы, что исключает протекание тока через

МДП-транзистор, затвор которого соединен с входом записи, имеющим уровень логической единицы, а сток — с выходдм устройства, к которому подключен, элемент памяти накопителя шиной, имеющей уровень логического нуля, При этом требуемые условия записи без существенного снижения быстродействия могут быть обеспечены выбором размеров транзисторов записи, дополнительного МДП-тран .— зистора и транзисторов инвертора.

ВНИИПИ .. Заказ 2511/42

Тираж 584 Поддисное

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4