Устройство для сложения многоразрядных @ -ичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ МНОГОРАЗРЯДНЫХ q-ИЧНЫХ ЧИСЕЛ, содержащее в каждом q-ичном разряде . первый матричный сумматор и первый блок переноса, причем первые входы первого матричного сумматора соеди иены с первой группой входов первого слагаемого данного q-ичного ряда устройства, вторые входы первого матричного сумматора соединены с первой,группой входов второго слагаемого данного q-ичного разряда устройства, а выходы суммы соединены с информационными входами первого блока переноса, информацион ные выходы которого соединены с первой группой выходов суммы данного q-ичного разряда устройства, отличающееся тем, что, с цепью повышения быстродействия, оно содержит в каждом q-rt4HOM разряде матричные сумматоры с второго по п-й и блоки переноса с второго по п-й, а также блок .хранения констант, сумматор „нулевизации, первый, второй , и третий элементы И, первый и второй элементы ИЛИ, причем первые и вторые входы матричных сумматоров с второго по п-й соединены с .входами соответствующих групп входов соответ ственно первого и второго слагаемых данного q-ичного разряда устройства, выходы матричных сумматоров с второго по (п-1)-й соединены с информационными входами соответствующих блоков переноса, информационные выходы которых соединены с соответствующими группами выходов суммы, данного q-ичного разряда устройства, адресные входы блока хранения констант соединены с выходами матричных сумматоров с первого по (п-1)-й, а СЛ С выход соединен с первым входом сумматора нулевизации, второй вход которого соединен с выходом п-го матричного сумматора, первые входы первого и второго элементов И соединены с соответствующими выходами п-го матричного сумматора, а вторые входы подключены к инверсному выходу сумматора нулевизации, прямой выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выходы первого элемента И и первого элемента ИЛИ соединены с соответствующими информационными входами п-го блока переноса, выходы старших цифр матричных сумма торов с первого по (п-1)-й соединены с соответствующими входами третьего элемента И, (п-1)-й вход которого подключен к выходу первого элемента И, а п-й вход - к выходу второго элемента ИЛИ предыдущего q-ичного разряда устройства, выход третьего

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСИИХ

РЕСОУБЛИН ((9) (l l) 4(51) 4 06 E 7/49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙ (21) 3603690/24-24 (221 14 ° 06.83 (461 23.06.85. Бюл. У 23 (72) В. Г. Евстигнеев и О, В. Евстигнеева (71) Московский институт инженер в, гражданской авиации (531 681 . 325. 5 (088. 8 ) (56) Авторское свидетельство СССР

1(478304, кл. Q 06 F 7/50, 1975.

Оранский А. M. Аппаратные методы в ЦВТ. Минск, изд-во БГУ, 1977, с, 27, рис ° 1.7 (прототип ). (54)(57) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ

МНОГОРАЗРЯДНЫХ q-ИЧНЫХ ЧИСЕЛ, содержащее в каждом q-ичном разряде первый матричный сумматор и первый блок переноса, причем первые входы первого матричного сумматора соединены с первой группой входов первого слагаемого данного q-ичного pasряда устройства, вторые входы перваго матричного сумматора соединены с первой группой входов второго слагаемого данного q-ичного разряда устройства, а выходы суммы соединены с информационными входами первого блока переноса, информацион" ные- выходы которого соединены с первой группой выходов суммы данного

q-ичного разряда устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит в каждом q"é÷íoì разряде матричные сумматоры с второго по . и-й и блоки переноса с второго по п-й, а также блок, хранения констант, сумматор,нулевизации, первый, второй. и третий элементы И, первый и второй элементы ИЛИ, причем первые и вторые входы матричных сумматоров с второго по и-й соединены с .входами соответствующих групп входов соответственно первого и второго слагаемых данного q-ичного разряда устройства, выходы матричных сумматоров с второго по (n-1)-й соединены с информационными входами соответствующих блоков переноса, информационные выходы которых соединены с соответствующими группами выходов суммы, данного

q-ичного разряда устройства, адресные входы блока хранения констант соединены с выходами матричных сумматоров с первого по (n-l)-й, а выход соединен с первым входом сумматора нулевизации, второй вход которого соединен с выходом и-го матричного сумматора, первые входы первого и второго элементов И соединены с соответствующими выходами и-го матричного сумматора, а вторые входы подключены к инверсному выходу сумматора нулевизации, прямой выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И,.выходы первого элемента И и первого элемента ИЛИ соединены с соответствующими информационными входами n-ro блока переноса, выходы старших цифр матричных сумматоров с первого по (n-1)-й соединены с соответствующими входами третьего элемента И, (n-1)-й вход которого подключен к выходу первого элемента

И, à и-й вход — к выходу второго элемента ИЛИ предыдущего q-ичного разряда устройства, выход третьего

116332! п-му входу второго элемента ИЛИ следующего q-ичного разряда устройства и к управляющему входу блоков переноса того же q -ичного разряда устройства.

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств ЭВМ, Цель изобретения - повышение быстродействия.

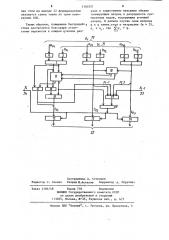

Fh чертеже представлена структурная схема одного q-ичного разряда устройства для сложения многоразрядных q-ичных чисел для п 3, !6

Устройство содержит матричные сумматоры 1-3 с входными дешифратора" ми 4-9, блок 10 хранения констант, сумматор 11 нулевизации, блоки 12-14 переноса, элементы И 15-17 и ИЛИ 18 . 1 и 19. Устройство имеет три группы входов 20 первого слагаемого, три группы входов 21 второго слагаемого, три группы выходов 22 суммы, вход

23 переноса и вход 24 переноса в 26 следствующий q-ичный разряд.

Устройство работает следующим образом.

Пусть исходные числа А и В представлены в позиционно-остаточной си- 2 стеме счисления в виде где а},, (О;- q-1 ; ЬЕ О, q-1 ; 2q.

-бр,, }г1 где P - основания системы остаточных

} классов, (СОК);

n — количество основан «й СОК в представлении q-ичной цифры, Ээ

m — количество q-ичных разрядов чисел В и А.

Поразрядная сумма SI слагаемых а; и Ь. в общем случае образуется по

1 правилу Ю с с„"a +b.+V;, c;, V, О, если с; (с 5 с! "q, Ч} 1, если а,. y q элемента И соединен с первым входом второго элемента ИЛИ, второй выход которого подключен к прямому вьгходу сумматора нулевиэации, а выход - к

In I11

А * Q a qI В = 2Ьq -"

-; 1 I%1

В предлагаемом устройстве каждый

q-ичный разряд выполнен в виде совокупности матричных сумматоров 1-3 по и основаниям системы СОК, между которыми переносы отсутствуют.

Блок 10 хранения констант нулевизации представляет собой обычный блок постоянной памяти, в котором каждому сочетанию входных значений вычетов (каждому адресу) соответ— сгвует на выходе строго определенная константа.

Сумматор 11 нулевизации может быть выполнен табличным или комбинационным, он выполняет роль вычитателя константы нулевизации из результата суммирования по первому (четному) основанию СОК. В простейшем случае первое основание СОК

P = 2. тогда сумматор 11 нулевизаг ции работает по модулю два. Если результат сумматора l нулевизации равен нулю, то на выход через элементы И, 15 и 16 и ИЛИ 18 выдается результат сумматора 1 (."0" или "1").

Если результат сумматора ll нулевизации равен единице, то на выход через элемент ИЛИ 18 выдается нуль, т.е.

О, если с„= О н с, = Оили с}}=!

l, еслис„ I èñII =0

Блоки 12-1 4 пе рено са о суще ст вляют увеличение на единицу соответствующих сумм с, с д и с в зависимости

Р1 Р от наличия переноса в следствующий разряд f. на выходе элемента ИЛИ 19, 1

Такое увеличение на единицу легко выполняется при позиционно-унитарном кодировании чисел на выходах матричных сумматоров.

Исходные числа в позиционно-остаточном коде поступают на входы 20 и 2 1 каждого разряда устройства, 3 1163321 4 при этом на выходе 22 формирователя ряде и существенно меньшему объему находится сумма также по трем осно- . суммирующих матриц и разрядности сумваниям С0К. мируемых кодов, кодирующих q-ичный разряд. В данном случае одна матрица

Таким образом, повышение быстродей-.5 q x q замен..ется и матрицами (n 3), ствия достигается благодаря отсут- q. х q,, где q = q.

1 1 ствию переносов в каждом q-ичном разСоставитель А.. Степанов

Редактор С. Саенко . Техред H.Àñòàëoø .Корректор А, Обручаро

Заказ 4104/48 Тираж 710.. Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,. Ж-З5, . Раушская наб., д. 4/5

Филиал ППП "Патент", г . Ужгород, ул. Проектная, 4