@ -ичный сумматор

Иллюстрации

Показать всеРеферат

(J -ИЧНЫЙ СУММАТОР, содержащий группу сумматоров по модулю из (п+1) сумматоров

((9) (! !)!

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИМ

4(s)) G 06 F 7/49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСМОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTHA (21) 3603689/24-24 (22) 14.06.83 (46) 07.07.85. Бюл. 1) - 25 (72) В.Г.Евстигнеев и О,В.Евстигнеев@ (71) Московский институт инженеров гражданской авиации (53) 683.3(088.8) (56) 1. Авторское свидетельство СССР

Ф 488206, кл. С 06 F 7/49, 1974.

2. Авторское свидетельство СССР.

У 570052, кл. С 06 Р 7/49, 1975.

3. Авторское свидетельство СССР .У 454550, кл. G 06 F 7/39, 1972 (прототип). (54)(57) q -ИЧНЫЙ СУММАТОР, содержащий группу сумматоров по модулю из

1l ())+1) сумматоров (2q = Р - Z р;; р;модуль), два сумматора по модулю, два коммутатора, блок формирования переноса, содержащий первый элемент ИЛИ, причем входы первого и вто-. рого слагаемых о -ичного сумматора соединены с соответствующими входами сумматоров по модулю группы, выходы первого и второго сумматоров по модулю соединены соответственно с первыми информационными входами первого и второго коммутаторов, вторые информационные входы которых соединены соответственно с выходами первого и последнего сумматоров по модулю группы, первые управляющие входы первого и второго коммутаторов соединены с выходом первого элемента ИЛИ блока формирования переноса и выходом пере-.. носа() -ичного сумматора, о т л и— .ч а ю щ к и с я тем, что, с целью повышения быстродействия, блок форми- . рования переноса содержит узел памяти констант нулевизации, вычитатель по модулю и второй элемент ИЛИ, причем выходы сумматоров по модулю группы, кроме первого, соединены соответ-ственно с адресными входами узла памяти констант нулевизации, выход которого и выход первого сумматора по модулю группы соединены соответственно с входами вычитаемого и уменьшаемого вычитателя по модулю блока формирования переноса 4 = e (t -(,2,„, р), ) и г= е (г= О ) Р, -,1,..., н, < ), выходы С которого соединены соответственно с входами первого и второго элементов ИЛИ блока формирования переноса, выход второго элемента ИЛИ блока фор" мирования переноса соединен с вторыми управляющими входами первого и второго коммутаторов, выходы первого коммутатора, сумматоров по модулю группы, кроме первого и последнего, и второго коммутатора являются выходом суммы () -ичного сумматора, sxoды первого и последнего сумматоров по модулю группы соединены с соответствующими входами первого и второго сумматоров,по модулю. Э

1166097

Изобретение относится к вычислигельной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих в позиционно-остаточной сис- 5 теме счисления (ПОСС).

Известно устройство для сложения, состоящее из последовательно соединенных в кольцо шинами. переноса дво-. ично-десятичных декад сумматоров эле-10 ментов задержки, узлов анализа .переполнения декады, элементов И, элементов ИЛИ, триггеров и соответствующих связей $1$, Однако данное устройство может 15 работать только в десятичной системе счисления.

Известен сумматор по модулю, содержащий позиционный и непозиционный сумматоры, блок инвертирования, блок 20 переполнения, коммутатор f2) .

Недостатком этого устройства является работа только в системе остаточных классов.

Наиболее близким к изобретению по 25 .технической сущности является многоразрядный сумматор, содержащий два. сумматора, два вычитателя, два ком-. мутатора, блок формирования переноса, группу элементов И, причем входы пер 30 вого и второго слагаемых соединены с соответствующими входами сумматоров, выходы которых соединены с входами соответствующих вычитателей с первыми информационными входами соответствующих коммутаторов и входами блока формирования переноса, выход которого соединен с управляющими входами коммутаторов, вторые информационные входы которых соединены с BbI-40 ходами соответствующих вычитателей, а выходы — с выходами элементов И группы, выходы которых являются выходами суммы (3) .

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — повышение быст. родействия..

Поставленьая цель достигается 50 тем,.что в q-ичный сумматор, содер. жащий группу сумматоров по модулю из (n+1) сумматоров (2q=P= f P;;

Р; - модуль), два сумматора "по модулю, два коммутатора, блок форми- 55 рования .переноса, содержащий первый ,элемент ИЛИ, причем входы первого и ,второго слагаемых q ного сумматора соединены с соответствующими входами сумматоров по модулю грчппы, выходы первого и второго сумматоров по модулю соединены соответственно с первыми информационными входами первого и второго коммутаторов, вторые информационные входы которых соединены соответственно с выходами первого и последнего сумматоров по модулю группы, первого и последнего сумматоров по модулю группы, первые управляющие входы первого и второго коммутаторов соединены с выходом первого элемен-. та ИЛИ блока формирования переноса и выходом переноса q-ичного сумматора, блок, формирования переноса содержит узел памяти контакт нулевизаФ ции, вычитатель по модулю и второй элемент ИЛИ, причем выходы сумматоров по модулю группы, кроме первого, соединены соответственно с адресными входами узла памяти констант нулевизации, выход которого и выход первого сумматора по модулю группы соединены соответственно с входами вычитаемого и уменьшаемого вычитателя по модулю блока формирования переноса t-e (t=1, 2,...,Р / ) и, r=e (r=O, P)-Л,...,Р„) +

+1), выходы которого соединены соответственно с входами первого и второго элементов ИЛИ, блока формирования переноса, выход второго элемента ИЛИ блока формирования переноса. соединен с вторыми управляющими входами первого и второго коммутаторов, выходы первого коммутатора, сумматоров по модулю группы, кроме первого и последнего, и второго коммутатора являются выходом суммы q-ичного сумматора,. входы первого и последнего сумматора по модулю группы соединены с соответствующими входами первого и второго сумматоров по модулю.

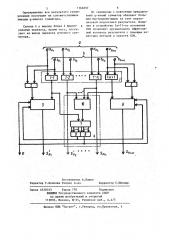

На чертеже дана схема q-ичного сумматора, q-ичный сумматор содержит группу 1 сумматоров по модулю, сумматоры 2 и 3 по модулю, блок 4 формирования переноса, коммутаторы 5 и 6, вычитатель 7 по модулю, элементыИЛИ 8 и 9, узел 10 памяти констант нулевизации.

В основу работы q-ичного сумматора положено представление каждого операнда в коде СОК по совокупности иэ и рабочих и одного контрольного (и+1). оснований. При сложении операнpos А и В, лежащих в диапазоне q

1166097,о,у„„), 20

-(О,Р1(. ) ° . °,Р,! +1, если g =(1, 2, и S=C-q в СОК имеет следующий

Н=(У„О,. тогда, если то П =О и 8=с, Р » то 0 =1 онстанта q код

q=(1,0,...,0, У ).

Сумматоры 2 и.3 по модулю формируют величины С,=(С -q}P и С„, =(С„, -

q) „ . Кодировка узла 10 памяти констант нулевизации выполняется соглас-З0 но следующей таблице (для Р =4, Ря3, :P =5, Р =7, q=30).

О

О О

1 О

2 0

40

45

1 1

2 1

О 2

1 2

50

2 2

0 3

1 3 промежуточный результат С может достичь величины 2q.

В этом случае сумма S и перенос Il равны. Если C

Теория COK рекомендует одно из ос-. нований СОК выбрать четным, в общем случае целесообразно выбирать Р =2 е

Факт переполнения, т. е. выходы результата суммирования за диапазон q 10 обычно обнаруживается с помощью нулевнзации. Нулевизацию целесообразно проводить по основаниям P» ..., Р„, а факт переполнения определять по вычету основания Р . Это дает значительное повышение быстродействия.

Пусть в результате нулевиэации получено число

Продолжение таблицы

3 0

2 3

О 4

1 4

2 4

О

Блок 4 формирования переноса содержит модульный вычитатель 7, работающий по основанию Р, и может быть как комбинационным, так и табличным.

Результат данного модульного вычитателя должен быть в коде 1 из Р . Его можно получить с помощью дешифратора при комбинационном вычитателе 7 либо непосредственно (при табличном вычитателе 7).

q-ичный сумматор работает следую-, щим образом.

Исходные числа в виде двоичных кодов вычетов по всем основаниям СОК поступают на входы сумматоров 1-3.

Сумматоры 1 формируют сумму чисел по соответствующим основаниям. Сумматоры 2 и 3 формируют значения сумм по основаниям Р, и, P уменьшенные

n+1 на величины вычетов числа q no соответствующим основаниям. Результат суммировайия по основаниям с Р по

Р„,, с сумматоров 1 в виде адреса по- ступает на адресные входы узла 10 хранения констант нулевизации, в котором производится выборка константы нулевизации по основанию Р и подача ее на вход вычитаемого вычитателя 7 блока 4 формирования переноса. На вход уменьшаемого вычитателя 7 блока

4 поступает результат суммирования с первого модульного сумматора 1 группы. В результате срабатывания вычитателя 7 и одного из элементов ИПИ 8 или 9 на выходе блока 4 формирования переноса появится либо сигнал Д (было переполнение), либо сигнал П (переполнения не было). Эти сигналы, поступая на управляющие входы первого 5 и второго 6 коммутаторов, осуществляют . через них передачу на выход либо сумм по основаниям Р и Р„, либо уменьшенных сумм по тем же основаниями

66097

Составитель А.Клюев

Редактор Г.Волкова Техред А.Ач Корректор С.Шекмар

Заказ 43:,10/43 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5 филиал ППП. "Патент", r.Óæãîðîä, ул.Проектная, 4

5 11

Одновременно все результаты суммирования поступают на соответствующие выходы ц"ичного сумматора.

Сигнал и:с выхода блока 4 формирования переноса, кроме того, поступает на выход переноса q-ичного сумматора

По сравнению с известным предлагаемый ц-ичный сумматор обладает большим быстродействием за счет параллельной подготовки результата. Наличие в устройстве (n+1)-ro основания

С0К позволяет организовать эффективный контроль результата с помощью известных методов и средств СОК.