Ассоциативное суммирующее устройство

Иллюстрации

Показать всеРеферат

АССОЦИАТИВНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО, содержащее ассоциативный запоминающий блок, постоянный запоминающий блок, первую и вторую группы элементов И, первую и вторую груп пы элементов задержки, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И первой группы , первые входы которых подключены к первому входу синхронизации устройства , первый разрядный выход ассоциативного запоминающего блока соединен с выходом суммы устройства, а остальные разрязные выходы подключены к входам соответствующих эле ментов задержки первой группы, выходы элементов И второй группы подключены к соответствующим входам опроса ассоциативного запоминающего блока, первые входы элементов И второй группы соединены с вторым входом синхронизации устройства, разрядные выходы постоянного запоминающед о блока, кроме выхода младшего разря да , соединены с входами соответствующих элементов задержки второй группы, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит первый и второй преобразователи двоичного кода уплотненный код, причем входы первого преобразователя (Л двоичного кода, уплотненный код соединен -с входами слагаемых устройства , а выходы подключены к вторым входам соответствующих элементов И первой группы, входы второго преобразователя двоичного кода в уплотненный код соединены соответственно с выходом младшего разряда постоянно4;: го запоминающего блока, с выходами СО ND элементов задержки первой группы и с выходами элементов задержки второй группы, а выходы подключены к .вторым входам соответствующих элементов И второй группы.

СОЮЗ СОВЕТСНИХ

С014ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5!) 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

rI0 ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ (21) 3632515/24-24 (22) 12.08.83 (46) 23.08.85. Бюл. N - 31 (72) Ш.-M.À.Èñìàèëîâ, О.M.Îìàðîâ и И.А.Айдемиров (71) Дагестанский политехнический институт (53) 681.325(088.8) (56) Кохонен Т. Ассоциативная память. М: Мир, 1980, с.20, рис.1.4

Авторское свидетельство СССР

Ф 1062689, кл. G 06 F 7/50, I982. (54) (5 7) АССОЦИАТИВНОЕ СУММИРУЮЩЕЕ

УСТРОЙСТВО, содержащее ассоциативный запоминающий блок, постоянный запоминающий блок, первую и вторую группы элементов И, первую и вторую груп" пы элементов задержки, причем адресные входы постоянного запоминающего блока соединены с выходами соответствующих элементов И первой группы, первые входы которых подключены к первому входу синхронизации устройства, первый разрядный выход ассоциативного запоминающего блока соединен с выходом суммы устройства, а остальные разрязные выходы подключены к входам соответствующих эле" ментов задержки первой группы, вы„„SU„„1!?4920 А ходы элементов И второй группы подключены к соответствующим входам опроса ассоциативного запоминающего блока, первые входы элементов И второй группы соединены с вторым входом синхронизации устройства, разрядные выходы постоянного запоминающего блока, кроме выхода младшего разря— да, соединены с входами соответст.вующих элементов задержки второй группы, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит первый и второй преобразователи двоичного кода в уплотненный код, причем входы первого преобразователя двоичного кода, уплотненный код со-" единен с входами слагаемых устройства, а выходы подключены к вторЫм входам соответствующих элементов И первой группы, входы второго преобразователя двоичного кода в уплотненный код соединены соответственно с выходом младшего разряда постоянного запоминающего блока, с выходами элементов задержки первой группы и с выходами элементов задержки второй группы, а выходы подключены к . вторым входам соответствующих элементов И второй группы.

1 11

Изобретение относится к области вычислительной техники и может быть использовано s устройствах обработки массивов чисел.

Целью изобретения является сокращение аппаратурных затрат в ассоциативном суммирующем устройстве.

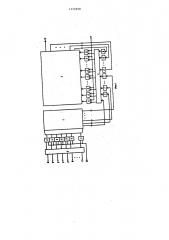

На фиг.l представлена структурная схема ассоциативного суммирующего устройства; на фиг.2 — размещение информации в постоянном и ассоциативном запомннающих блоках для сЛучая суммирования семи операндов, Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, преобразователи

3 и 4 двоичного кода в уплотненный код, группы элементов И и 6, группы элементов 7 и 8 задержки, информационные входы 9, входы 10 и ll синхронизации и выход 12 суммы.

Устройство работает следующим образом.

На входы 9 поступают одно".менные разряды всех слагаемых, начиная с младших разрядов. Преобразователь

3 преобразует поступающий на его входы двоичный код в уплотненный код, который через элементы И 5 поступает на адресный вход запоминающего блока в течение тактового импульса по входу 10. Считанное из блока 1 слово является частью ассо- циативного признака для ассоциатив-. ного запоминающего блока 2. Второй частью признака являются. все, кроме первого, разряды кода, считанного из блока 2. Обе части признака поступают на преобразователь двоичного кода в уплотненный код 4 через элементы 7 и 8 задержки, причем младший разряд слова, считанного из блока 1, поступает на преобразователь 4 без задержки. Сформированный на выходе преобразователя 4 признак дополнительно сннхронизируется импульсом по входу 11 с помощью элементов И 6. Такая синхронизация исключает влияние неидеальности элементов 7 и 8 задержки. На выходе 12 формируется очередной разряд суммы,, Общее число тактов вычисления суммы равно

m= п + (log>Nj где п - разрядность слагаемых, К вЂ” количество слагаемых, 74920 2

Пусть необходимо просуммировать следующие семь слагаемых: 010110;

101011 011011! }11}11! 101110

110011; 101010.

Обрабатываемые срезы на входе преобразователя 3 имеют вид

0111010; 1111111; 1001100;0111101

1011010; 0101111.

На выходе преобразователя 3 обра-. батываемые срезы имеют вид

00011!1 1111111 0000111 00}11!1

0001111; 0011111.

В течение первого тактового импульса, поданного на вход 10 синхронизации, на адресный вход блока 1 подаются с выхода преобразователя 3 младшие разряды слагаемых, т.е. адрес 0001111.

По указанному адресу из блока 1 считывается в том же такте слово

0011, первый разряд которого "0" без задержки подаетСя на первый вход преобразователя 4, а остальные через элементы 7 задержки — на соответствующие входы того же преобразователя.

Так как в первом такте из блока 2 ничего не считывается, то к приходу первого испульса по входу ll синхронизации на все входы преобразователя

4 подаются нули.

Сформированный признак с выхода преобразователя 4 кода — 0000000, с приходом тактового импульса по входу 1.1 поступает на признаковые входы блока 2. Следовательно, в первом такте из блока 2 считывается слово 0000, первый разряд которого "0" является младшим разрядом искомой суммы.

В течение второго импульса, поданного на вход 10 синхронизации, на вход адреса 1 с выхода преобразователя 3 подается второй разрядный срез слагаемых, т.е. адрес 1111111.

По указанному адресу из блока 1 считывается слово }ill. На входе преобразователя 4 формируется слово

1011000 соответственно на .его выходе

0000111, которое по приходу импульса по входу 11 поступает на признаковые входы блока 2, из которого считывается слово 0011, первый разряд которого "1" является вторым разрядом искомой суммы.

В течение третьего импульса, поданного на вход 10 синхронизации, на вход адреса блока 1 с выхода преобразователя 3 подается третий обрабатываемый срез 00001}l.

По указанному адресу из блока 1 считывается слово 1001. На входе преобразователя 4 формируется слово

1111001, соответственно íà его выходе — 001I111, которое при приходу импульса по входу 11 поступает на признаковый вход блока 2, из которого считывается слово 0111, первый

1174920 4 разряд которого "1" является третьим разрядом искомой суммы.

Аналогичным образом предлагаемое устройство продолжает работу до получения десятого разряда суммы. Код суммы при этом 100-100110. В восьмом и девятом тактах на вход преобразователя 3 поступают нулевые коды.

1l74920

1174920

Составитель А.Степанов

Техред N.Ëàðîöàé

Корректор А.Обручар

Редактор Л.Гратилло

Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4

Заказ 5201/50 Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,4/5