Дешифратор на кмдп-транзисторах

Иллюстрации

Показать всеРеферат

ДЕШИФРАТОР HA ЩЦП-ТРАНЗИСТОРАХ , содержащий параллельную группу транзисторов первого типа проводимости , стробируюпщй транзистор первого типа проводимости, установочный транзистор второго типа, проводимости , фиксирующий транзистор второго типа проводимости и выходной каскад , состоящий из первого и второго транзисторов второго тийа -проводимости и третьего транзистора первого типа проводимости, истоки транзисторов параллельной группы соединены со стоком стробирующего транзистора, затворы с соответствующими входами дешифратора, а стоки со стоками установочного и фиксирующего транзисторов и затворами первого и третьего транзиьторов выход 1ого каскада, стоки которых объединены и подключены к затвору фиксирующего транзистора , стоку второго транзистора выходного и выходу дешифратора,истоки первого и второго транзисто ров выходного каскада соединеныс шиной источника питания и истоками установочного и фиксирующего транзисторов , затвор второго транзистора выходного каскада соединен Стак (Л товой шиной и затвором стробируюс щего транзистора, исток которого соединен с общей шиной, отличающийся тем, что, с целью повышения быстродействия, исток третьего транзистора выходного каскада соединен с истоками транзисторов параллельной группы, а затвор установочного транзистора подключен к 00 тактовой шине. о ;о iti

СО)ОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (! 9) (I)) (5))4 С 11 С 8 00

ОПИСАНИЕ ИЗОБРЕТЕНИ

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3602829/24-21 (22) 09.06.83 (46) 23.09.85. Бюл. ¹ 35 (72) В.В.Баранов, IO.M.Ãåðàcèìîâ»

Н.Г.Григорьев, А.Н.Кармазинский, .

П.Б.Поплевин и Э.П.Савостьянов (53) 621.327.6(088.8) (56) Авторское свидетельство СССР № 798997, кл, С 11 С 8/00» 1979.

0hoytna А., à.î. CMOSHk» Static, RAM., Toshiba Review № 110, Jul-Aug»

1977, р. 24, fig. 4. (54)(57) ДЕШИФРАТОР НА ИЩП-ТРАНЗИСТОРАХ, содержащий параллельную группу транзисторов первого тина проводимости, стробирующий транзистор первого типа проводимости, установочный транзистор второго типа проводимости, фиксирующий транзистор второго типа проводимости и выходной каскад, состоящий из первого и второго транзисторов второго типа проводимости и третьего транзистора первого типа проводимости, истоки транзисто- ров параллельной группы соединены со стоком стробирующего транзистора, затворы с соответствующими входами дешифратора, а стоки - со стокамй установочного и фиксирующего транзисторов и затворами первого и треть"

его транзисторов выходного каскада, стоки которых объединены и подключены к затвору фиксирующего транзистора, стоку второго транзистора выходного каскада и выходу дешифратора, истоки первого и второго транзисторов выходного каскаДа соединены с шиной источника питания и истоками установочного и фиксирующего транзисторов, затвор второго транзистора выходного каскада соединен с-тактовой шиной и затвором стробирующего транзистора, исток которого соединен с общей шиной, о т л и ч аю шийся тем, что, с целью повышения быстродействия, исток третьего транзистора выходного каскада соединен с истоками транзисторов параллельной группы, а затвор уста новочного транзистора подключен к тактовой шине.

11809

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на КМДП-транзисторах для дешифрации адресных сигналов. 5

Цель изобретения — повышение быстродействия устройства.

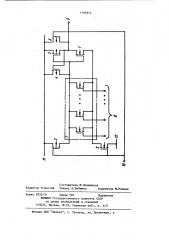

На чертежЕ представлена принципиальная электрическая схема дешифра-тора. 10

Дешифратор содержит группу 1 соединенных параллельно транзисторов первого типа проводимости, стробируюпщй транзистор 2 первого типа проводимости,установочныйтранзистор .15

3 второго типа проводимости, фиксирующий транзистор 4 второго типа проводимости, выходной каскад, состоящий из первого и второго транзисторов 5 и 6 второго типа проводимости 2п, и третьего транзистора 7 первого типа проводимости, входы 8, выход 9, тактовую шину 10, шину 11 источника питания, и общую шину 12, причем истоки транзисторов параллельной груп- 25 пы 1 соединены со стоком стробирующего транзистора 2, затворы — с входами 8 дешифратора, стоки — со сто" ками установочного и фиксирующего транзисторов 3,4 и затворами первого 30 и третьего транзисторов 5 и 7 выходного каскада, стоки которых соединены с затворами фиксирующего транзистора 4, стоком второго транзистора 6 выходного каскада и выходом 9 дешифратора, истоки первого и второ го транзисторов 5 и 6 выходного каскада соединены с шиной 11 источника питания и истоками установочного и фиксирующего транзисторов 3 и 4, О затвор установочного транзистора 3 соединен с тактовой шиной 10 и затвором стробирующего транзистора 2, исток которого соединен с общей шиной 12, исток третьего транзистора 7 45 выходного каскада соединен с истока» ми транзисторов группы 1, а затвор второго транзистора 6 выходного каскада соединен с тактовой шиной 10.

Дешифратор работает следующим об- 5О разом.

В режиме хранения (статический режим) на тактовую шину 10 подают потенциал логического нуля. На шине

11 источника питания поддерживают потенциал логической единицы, а

74 2 на общей шине 12 — потенциал логи- . ческого нуля. При этом стробирующий транзистор 2 закрыт, а установочный транзистор 3 — открыт. В результате независимо от состояния транзисторов группы 1 на стоке установочного транзистора 3 устанавливается потенциал логической единицы. При этом первый транзистор 5 выходного каскада оказывается закрытым по затвору, а транзистор 7 — закрытым по истоку.

Поскольку потенциал тактовой шины

10 равен логическому нулю, то второй транзистор 6 выходного каскада оказывается открытым. В результате на выходе 9 дешифратора устанавливается потенциал логической единицы.

В режиме выборки информации на тактовую шину 10 подают потенциал логической единицы, а на всех выходах

8 дешифратора поддерживают потенциалы логического нуля. При этом установочный транзистор 3, второй транзистор 6 выходного каскада и все транзисторы группы 1 оказываются закрытыми, а стробирующий транзистор 2 — открытым.

В результате потенциал на стоке установочного транзистора 3 остается на прежнем уровне, а потенциал на стоке стробирующего транзистора

2 уменьшается до уровня логического нуля. При этом открывается третий транзистор 7 выходного каскада,,и . потенциал на выходе 9 дешифратора уменьшается до нуля. фиксирующий транзистор 4 открывается, и потенциал на стоке этого транзистора 4 фиксируется на уровне логической ,единицы.

В режиме невыборки информации на тактовую шину 10 и хотя бы на один из входов 8 дешифратора пода-. ют логический потенциал логической единицы. При этом открывается хотя бы один из транзисторов группы 1, и уменьшение потенциала на стоке стробирующего транзистора 2 приводит к уменьшению потенциала на стоке установочного транзистора 3.

В результате открывается первый транзистор 5 выходного каскада, и выход .9 дешифратора оказывается подключенным к шине 11 питания.

1180974

Составитель Ю.Плужников

Редактор П.Коссей Техред А.Бабинец Корректор M.Ðoçìàí

Заказ 5932/51 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 и филиал ППП "Патент", r. Ужгород, ул, Проектная, 4