Управляемый логический модуль

Иллюстрации

Показать всеРеферат

УПРАВЛЯЕМЫЙ-ЛОГИЧЕСКИЙ МОДУЛЬ , содержащий первый и второй триггеры, пять элементов И, три элемента ИЛИ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, единичный выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, второй вход второго элемента И соединен с первым управляющим входом модуля, второй управляющий вход которого сое-динен с первыми входами первого и четвертого элементов И, вторые входы которых соединены соответственно с первым и вторым информационными входами модуля, второй вход первого элемента ИЛИ соединен с третьим управляющим входом модуля, первый и второй выходы которого подключены соответственно к единичному и нулевому выходам второго триггера, единичный вход которого соединен с выходом второго элемента ИЛИ, а нулевой вход второго триггера соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, первый i. вход которого Соединен с нулевым (Л выходом первого триггера, первый вход третьего-элемента И соединен с четвертым управляющим входом модуля , пятый управляющий вход которого соединен с вторым входом пятого элемента И, шестой управляющий вход модуля соединен с вторым входом со третьего элемента ИЛИ, отличающийся тем, что, с целью упрощеО ) 00 ния, выход четвертого элемента И соединен с единичным входом первого сд триггера, нулевой выход которого соединен с вторым входом третьего элемента И.

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1196851 5р 4 С 06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21} 3787385/24-24 (22) 28.06.84 (46) 07.12.85. Бюл. У 45 (7 1) Груэинский ордена Ленина и ордена Трудового Красного Знамени политехнический институт (72) Г.С. Цирамуя, Л.Ш, Имнаишвили и Л.И. Гочиташвили (53) 681.3(088.8) (56) Авторское свидетельство СССР

1Ф 1062688, кл. G 06. F 7/38, 1982.

Авторское свидетельство СССР

У 962923, кл. G 06 F 7/38, 1980. (54)(57) УПРАВЛЯЕМЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ, содержащий первый и второй триггеры, пять элементов И, три эле" мента ИЛИ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, единичный выход которого соединен с.первым входом второго элемента И, выход которого соединен с первым входом второго элемента

ИЛИ, второй вход которого подключен к выходу третьего элемента И, второй вход второго элемента И соединен с первым управляющим входом модуля, второй управляющий вход которого сое-. динен с первыми входами первого и четвертого элементов И, вторые входы которых соединены соответственно с первым и вторым информационными входами модуля, второй вход первого элемента ИЛИ соединен с третьим управляющим входом модуля, пер- . вый и второй выходы которого подклю-. чены соответственно к единичному и нулевому выходам второго триггера, единичный вход которого соединен с выходом второго элемента ИЛИ, а нулевой вход второго триггера соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом пятого элемента И, первый а

Ю вход которого соединен с нулевым выходом первого триггера, первый вход третьего. элемента И соединен с четвертым управляющим входом мо- С дуля, пятый управляющий вход которо го соединен с вторым входом пятого элемента И, шестой управляющий вход модуля соединен с вторым входом третьего элемента ИЛИ, о т л и ч а юшийся тем, что, с целью упроще- ф ния, выход четвертого элемента И соединен с единичным входом первого р. триггера, нулевой выход которого соединен с вторым входом третьего элемента И.

1 119

Изобретение относится к вычислительной технике и предназначено для .реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним и большим уровнем интеграции.

Целью изобретения является сокращение Количества оборудования.

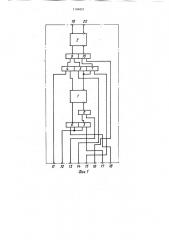

На фиг. 1 представлена схема управляемого логическога модуля; на .. фиг. 2 — схема управляемого логического регистра, состоящего из предложенных модулей.

Управляемый логический модуль (фиг. 1) содержит триггеры 1 и 2, эле— менты И 3-7, элементы ИЛИ S- lO, управляющие входы 11-16, информацион— ные входы 17 и 18, выходы 19 и 20.

Управляемый логический регистр (фиг. 2) содержит входы 1-24 выходы

25-32, входы 33-34, триггеры 35 первой группы, триггеры 36 второй группы, элементы И 37 первой группы, элементы И 38 второй группы, элементы

И 39 третьей группы, элементы И ч0 четвертой группы, элементы И 41 пятой группы, элементы ИЛИ 42 первой группы, элементы ИЛИ 43 второй группы, элементы ИЛИ 44 третьей группы.

Х Х (входы 17, 18) — разряды операн— дов; У (входы 11) — дизъюнкция содержимого триггеров 1 и 2; У, (вход

12) — прием информации в первый триггер 1; У, (вход l3) — установка.первого триггера 1 в ноль; У (вход 14)— .дизъюнкция инверсного значения содержимого триггера 1 и содержимого триггера 2; У (вход 15) — конъюнкция содержимого первого и второго триггеров; У (вход 16) — установка второго триггера 2 в ноль.

Функционирование управляемого логического модуля проиллюстрируем на примере четырехразрядного управляемого логического регистра, функциональная схема которого представлена на фиг. 2. Каждый разряд управляемого логического регистра представляет собой предлагаемый логический модуль, совокупность которых образует в управляемом логическом регистре основной и дополнительныи регистры.

С помощью одного управляемого логического регистра на основе управляемого логического модуля, в зависимости от коммутации, можно реализовать ÇS различных логических, ариф6851 метических и специальных вычислительных функций.

В качестве примера рассмотрим выполнение функций поразрядной конъюнкции сложения по модулю два и двоич9 ного суммирующего счетчика.

Функция поразрядной коньюнкции двух двоичных чисел выполняется следующим образом. Произведем коммутацию первого, второго и пятого управляющих входов в следующем порядке

4-10-16-22, 1-7-13-19 и 6-12-18-24, которые образуют соответственно управляющие входы УВх1, УВх2 и УВхЗ.

Операнд Х=Х Х Х Х поразрядно подается на группу вторых информационных входов 3,9,15 и 2 1 всех разрядов управляемого логического регистра, и сигналом на управляющий вход УВх1 через четвертую группу элементов И 40 заносится в триггеры 35 группы. После этого управляющий сигнал подаетФункция "Сложения по мой 2" двух двоичных операндов Х и У выполняется следующим образом: производится коммутация первых и вторых информа" ционных, первых и пятых управляющих и первых и вторых выходов управляемого логического модуля в следующем порядке: 1-6-7-12-13-18-19-24, 3-26,9 — 28,.11-27„15-30,17-29,21-32, 5О 2"-31,5-25. Сигналами по входам 33 и 34 триггеры 35 первой и 36 второй . групп устанавливаются в нуль. Операнд Х подается поразрядно на входы

4,l0,16,22 (12) управляемого логи55 ческого регистра и через четвертую группу элементов И 40 подается на прямые входы первых триггеров 35.

В результате чего в первых триггерах ся одновременно на управляющие входы УВх2, УВх3, открываются группы элементов И 38 и 41 и операнд переписывается в триггеры 36 группы. Операнд У=У У У У, подается также на группу вторых информационных входов

3,9,15 и 21 и сигналом на входе УВх1 заносится в триггеры 35 группы. Для осуществления операции конъюнкции подается сигнал УВхЗ и содержимое первых. триггеров 35 с инверсных выходов через пятую группу элемен35 тов И 41 и третью группу элементов

ИЛИ 44 переписывается во вторые триггеры 36. Результаты конъюнкции двух операндов получаем с прямых выходов

;вторых триггеров 36.

1196851 устанавливается сумма X90 . Сигналом УВх2 4 УВхЗ содержимое первых триггеров 35 через вторую 38 и пятую 41 группы элементов И и вторую

43 и третью 44 группы элементов ИЛИ переписывается во вторые триггеры 36.

После этого на входы 4,10,16,22 управляемого логического регистра подается операнд У и через первые элементы 37 и первые элементы ИЛИ 1О

42 или через четвертые элементы И

40 подается на инверсные или прямые (в зависимости от значения операнда

Х) входы первых триггеров 35, в результате чего в них устанавливается 15 сумма ХЮУ. Сигналом УВх2 Ь УВхЗ содержимое первых триггеров 35 переписывается во вторые триггеры 36.

На первых выходах 25-31 управляемого логического регистра устанавливает- 20 ся сумма. для реализации функции двоичного суммирующего счетчика производится коммутация управляющих информацион- д ных входов и выходов управляемого логического регистра в следующем порядке: 5-25-10,3-26-7-12 11-27-16;

9-28-13-18;1.7-29 22 ь15 30 " 9 24

21-32,23-31. Счетчик работает как обычный двухтактный суммирующий счетчик с последовательным переносом.

Двоичный счет осуществляется после установки в ноль первых 35 и вторых

36 триггеров сигналами по входам 33 и 34. До начала счета на вход 4 первого разряда подается низкий уровень парафазного импульса счета, а высокий уровень импульса счета подается на входы первого разряда 1. В первом щ .полупериоде импульс счета (высокий уровень импульса) через элемент И 40 первого разряда управляемого логического регистра подается на единичный вход триггера первого разряда 35 и переводит в единичное состояние, В это время второй триггер 36 первого разряда управляемого логического регистра не изменяет свое состояние.

Во втором полупериоде низкий уровень парафазного импульса счета подается на второй управляющий вход 4, и первый триггер 35 первого разряда остается в единичном состоянии, а высокий уровень парафазного импульса счета подается на входы 1 и 6 и через второй элемент И 38 и второй элемент ИЛИ 43 первого разряда подается на прямой вход второго триггера

36 данного разряда, который устанавливается в единичное состояние. Высокий уровень потенциала с первого выхода первого разряда управляемого логического регистра 25 поступает на вход второго разряда управляемого логического регистра 10.и через элемент И 40 данного разряда подается на единичный вход первого триггера

35 второго разряда управляемого логического регистра и переводит его в единичное состояние. После подачи первого полупериода второго парафазного импульса счета первый триггер первого разряда 35 переходит в нулевое состояние, а во втором полупериоде высокий уровень импульса счета через пятый элемент И 41 и элемент ИЛИ 44 данного разряда подается на нулевой вход второго триггера 36 и переводит

его в нулевое состояние. Высокий уровень потенциала с второго выхода первого разряда управляемого логического регистра 26 подается на входы

7 и 12 второго разряда управляемого логического регистра и через элементы И 38 и ИЛИ 43 подается на единичный вход второго триггера 36 второго разряда управляемого логического регистра. Триггер 36 переходит в единичное состояние, которое в свою очередь переводит первый триггер 35 третьего разряда управляемого логи- ческого регистра в единичное состояние и т.д.

1196851

fl 12 1Р 14 1Х 16 П 18

Фиг. 1

I 196851

1П

11

Редактор

Корректор Е. Сирохман

Заказ 7564/47 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

g

4

Е

f4

16

17

1Ó

Ю

?1 гг

Л

Ð4

Составитель А. Клюев

С. Патрушева . Техред М.Надь