Устройство для моделирования процессов движения поездов

Иллюстрации

Показать всеРеферат

yGTPOfiGTBO ДЛЯ МОДЕЛИРОВАНИЯ nPOUECGOB ДВИЖЕНИЯ ПОЕЗДОВ, содержащее группу генераторов случайных напряжений, группу сумматоров , группу запоминающих блоков, интегратор, запоминающий блок, источник опорных напряжений, пять групп элементов И по три элемента И в каждой, элемент НЕ, две схемы, сравнения, первый и второй триггеры, элемент задержки, два элемента И, группу амплитудных дискриминаторов, дифференциальный усилитель, первый выход источника опорных напряжений подключен к первьв входам сумматоров группы, выходы генераторов случай ных напряжений соединены с вторыми, входами сумматоров группы, входы которых соединены соответственно с прямьми входами элементов И первой группы, инверсные входы которых соединены с выходом элемента задержки , первыми входами первого и второго элементов И, выходы элементов И первой группы подключены к входам соответствующих запоминающих блоков группы, выходы которых соединены с первь1ми входами элементов И второй группы, вторые входы которых подключены соответственно к выходам элементов И третьей группы, выходы элементов И второй группы соединены с входом интегратора, выход которого подключен к первому входу дифференциального усилителя, второй вход которого соединен с первым выходом запоминающего блока и первым входом первой схемы сравнения, второй вход которой подкхпочен к второму выходу источника опорных напряжений н первому входу второй схемы сравнения, вход разрещения считьюания запоминающего блока подключен к первому W выходу первого триггера и входу элемента задержки, вход запрещения считывания запоминающего блока соединен § с вькодом второй схемы сравнения и вторьм входом второго элемента И, второй выход запоминающего блока соединен с первьм входом первого тригсо о; гера, второй вход которого является входом запуска устройства, первые с входы элементов И четвертой группы о со соединены с выходом элемента задержки , выходы элементов И четвертой группы подключены соответственно к Первым входам элементов И третьей группы, вторые входы которых соединены с первым выходом второго триггера, второй выход которого подключен к второму входу первого элемента И, выхйд которого соединен с вторым входом третьего элемен1а И второй группы ,, выход дифференциального усилителя соединен с входами амплитудных дискриминаторов группы, выходы кото

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (!в (и) (504 06 7 52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И 0THPbfAO

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ВСЕСОЮЗВАЯ

gg 1!ф(1 1 1 !(" (21) 3792370/24-24 (22) 08.06.84 (46) 07.12.85. Вюл. У 45 (71) Московский ордена Ленина и ордена Трудового Красного Знамени институт инженеров железнодорожного транспорта (72) Г.В. Дружинин, Л.А. Карпов и В.И. Грибков (53). 681 .322(088 .8) (56) Авторское свидетельство СССР

Ф 451104, кл. О 06 F 15/20, 1971.

Авторское свидетельство СССР

9 1018130, кл. G 06 G 7/52, !982. (54)(57) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССОВ ДВИЖЕНИЯ ПОЕЗДОВ, содержащее группу генераторов случайных напряжений, группу сумматоров, группу запоминающих блоков, интегратор, запоминающий блок, источник опорных напряжений, пять групп элементов И по три элемента

И в каждой, элемент НЕ, две схемы. сравнения, первый и второй триггеры, элемент задержки, два элемента И, группу амплитудных дискриминаторов, дифференциальный уснлитель, первый выход источника опорных напряжений подключен к первым входам сумматоров группы, выходы генераторов случайных напряжений соединены с вторыми входами сумматоров группы, входы которых соединены соответственно с прямыми входами элементов И первой группы, инверсные входы которых соединены с выходом элемента задержки, первыми входами первого и второго элементов И, выходы элементов И первой группы подключены к входам соответствующих запоминающих блоков ю группы, выходы которых соединены с первыми входами элементов И второй группы, вторые входы которых подключены соответственно к выходам элементов И третьей группы, выходы элементов И второй группы соединены с входом интегратора, выход которого подключен к первому входу дифференциального усилителя, второй вход которого соединен с первым выходом запоминающего блока и первым входом первой схемы сравнения, второй вход которой подключен к второму выходу источника опорных. напряжений и первому входу второй схемы сравнения, вход разрешения считьвання запоминающего блока подключен к первому выходу первого триггера и входу элемента задержки, вход запрещения считьвания запоминающего блока соединен с выходом второй схемы сравнения и вторьм входом второго элемента И, второй выход запоминающего блока соединен с первым входом первого триггера, второй вход которого является . входом запуска устройства, первые входы элементов И четвертой группы соединены с выходом элемента задерж- ки, выходы элементов И четвертой .группы подключены соответственно к первым входам элементов И третьей группы, вторые входы которых соединены с первым выходом второго триггера, второй выход которого подключен к .второму входу первого элемента И, выхбд которого соединен с вторым вхо.дом третьего элемента И второй группы,, выход дифференциального усилителя соединен с входами амплитудных дискриминаторов группы, выходы которых подключены соответственно к первым входам элементов И пятой группы, вторые входы которых соединены с выходом первой схемы сравнения и входом элемента НЕ, выход которого соединен с вторым входом третьего элемента И четвертой группы элементов И, выходы элементов И пятой группы соединены с вторыми входами элементов И четвертой группй соответственно, выход второго элемента И является выходом устройства, счетный вход второго триггера является входом переключения режимов работы устройства, о т— л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, оно дополнительно содержит третью схему сравнения, третий элемент И, 196909 сумматор, причем первый вход третьей схемы сравнения подключен к выходу интегратора, второй вход третьей схемы сравнения соединен с вторым выходом источника опорных напряжений, выход третьей схемы сравнения подключен к первому входу третьего элемента И, второй вход которого соединен с выходом интегратора, выход третьего элемента И соединен с первым входом сумматора, второй вход которого соединен с вторым выходом источника опорных напряжений, выход сумматора подключен к информационному входу запоминающего блока н второму входу второй схемы сравнения.

Изобретение относится к вычислительной технике и может быть использовано при моделировании сложных процессов движения транспортных средств, а также при составлении графиков движения поездов.

Цель изобретения — повышение точности, моделирования.

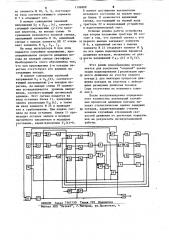

На чертеже представлена схема устройства для моделирования процессов движения поездов.

Устройство содержит группу генераторов 1 случайных напряжений, группу сумматоров 2, первую группу элементов И 3, первую группу запоминающих блоков 4, четвертую группу элементов И 5, третью 6 и вторую 7 группы элементов И, интегратор 8, третью схему 9 сравнения, третий элемент И 10, первый запоминающий блок 11, второй сумматор 12, дифференциальный усилитель 13, первую схему 14 сравнения, группу амплитудных дискриминаторов 15, пятую группу элементов И 16, элемент НЕ 17, источник 18 опорных напряжений, вторую схему 19 сравнения, второй триггер 20, первый элемент И 21, первый триггер 22, элемент 23 задержки, второй элемент И 24.

Устройство для моделирования процессов движения поездов работает следующим образом.

Триггер 20 имеет два положения и задает режимы работы устройства.

В первом положении на первом выходе триггера 20 имеется единичный сигнал, а на втором — нулевой. ори этом устройство имитирует процессы движеФ ния поездов с учетом их взаимного влияния, т.е. на различные (зеленые, желтые или красные ) показания путе10 вых светофоров.

Во втором положении на первом выходе триггера 20 имеется нулевой сигнал, а на втором — единичный.

В этом случае устройство моделирует

15 процесс движения поезда на зеленые показания светофоров . Необходимость использования данного режима работы связана с тем, что воспроизведенный устройством процесс движения первого

20 поезда является опорной" реализацией моделирования.

Устройство при первом положении триггера 20 работает следующим образом.

25 Каждый из генераторов 1 вырабатывает значения случайных напряжений, пропорциональные отклонениям от расчетной величины скорости движения поезда на зеленое (1 ), желтое щ (1 ) и красное (1 ) показание путеI

1 вого светофора. Эти напряжения подаются на входы соответствующих сумматоров 2, где происходит суммирова30 з 1196 ние постоянных напряжений, пропорцио1 нальных расчетным значениям скорости движения поезда, со случайными напряжениями, пропорциональными отклонениям скорости поезда от норматива.

Устройство работает тактами. В подготовительном такте на.выходах триггера 22, элемента 23 задержки, интегратора 8, запоминающего блока

l1, дифференциального усилителя 13, амплитудных дискриминаторов 15, схем 9 и !9 сравнения имеются нулевые сигналы, а на выходе схемы

14 сравнения — единичный сигнал, элементы И 3 открыты по инверсному входу, элементы И 5, 6, 16 и 24 закрыты. При этом случайные напряжения с выходов сумматоров 2 через соответствующие элементы И 3 подаются

20 на блоки 4 запоминания.

Единичный сигнал с выхода триггера 20 поступает на вторые входы элементов И 6.

В момент времени, соответствующий отправлению j-ro поезда на перегон, запускающий импульс опрокидывает триггер 22 и на его выходе появляется единичный сигнал, поступающий на первый вход блока !1 памяти и на вход элемента 23 задержки.

Ва втором входе блока 11 начинается воспроизведение реализации напряжения U x „(t), имитирующего процесс движения хвоста (j-1)-ro поезда.

Напряжение U,(й) подается на

I вход дифференциального усилителя 13 и на вход схемы 14 сравнения. Йа выходе усилителя 13 определяется разность aU(t) напряжения U „., (t) и напряжения U (t), имитирующего

j-1 процесс движения головы j-го поезда, с выхода интегратора 8, поступающая на входы амплитудных дискриминаторов.

При подаче сигнала на вход элемента 23 задержки им формируется интер- 4з вал времени, пропорциональный реальному интервалу времени между моментами отправления (j-1)-го и j-го поездов.

По окончании этого интервала на выходе элемента 23 появляется единичный сигнал, поступивший на входы элементов И 3, 5, 21 и 24. При подаче этого сигнала на входы элементов И 3 происходит их запирание. Выходы сумма->> торов 2 отключаются от входов блоков 4, в которых фиксируются случайные напряжения, пропорциональные

909 4 скорости движения поезда на различные сигналы путевых светофоров.

В момент появления на выходе элемента 23 единичного сигнала на выходе усилителя 13 имеется некоторое напряжение 4U(t), пропорциональное расстоянию между хвостом (j-!)-го и головой j-го поездов. В зависимости от величины этого напряжения происходит срабатывание соответствующего амплитудного дискриминатора 15 и на его выходе появляется единичный сигнал.

Этот сигнал открывает соответствующйй элемент И 16, сигнал с его выхода открывает определенный элемент И 5. Единичный сигнал с выхода последнего подается на первый вход соответствующего элемента И 6, открывая его.

При подаче сигнала с выхода эле- мента И 6 на второй вход соответствующего элемента И 7 напряжение с выхода запоминающего блока 4 подается на вход интегратора 8. На выходе последнего генерируется реализация линейно нарастающего напряжения

U;(t), имитируя процесс движения головы j-го поезда на соответствующее показание путевого светофора.

Напряжение U (t} с выхода интег1 ратора 8 подается иа первый вход схемы 9 сравнения, где производится его сравнение с опорным напряжением

Б!!д, пропорциональным длине поезда.

В момент совпадения напряжений

U !(й) и U1я сРабатывает схема 9 сРавнения и единичный сигнал с ее выхода открывает элемент И 10. При этом напряжение U (t) поступает на вход сумматора !2. На его выходе определяется разность напряжений U.(t) и

Uq>, поступающая на информационный вход блока ll, где происходит ее запоминание.

Вычисленная в усилителе 13 раз"ость "а"р"жений " к> q (t) " " <(t) подается на входы амплитудных дискриминаторов 15 и сравнивается с эталонными напряжениями, пропорциональными длине одного, двух и трех блок-участков, что соответствует движению поезда на красное, желтое или зеленое показания светофора.

На основании результатов сравнения срабатывает один из амплитудных дискриминаторов 15 группы, а сигнал с его выхода, открывая последователь5 1 но элементы И 16, 5, 6, поступает на вход соответствующего элемента

И 7 и открывает его.

В момент совпадения значений напряжений Ug и U>> {й), соответствующий прохожденйю (j-1)-м поездом перегона, на выходе схемы 14 сравнения появляется нулевой сигнал, запирающий элементы И 16, единичный сигнал с выхода элемента HE 17 открывает элементы И 5, 63, 7>.

На вход интегратора 8 при этом подается случайное напряжение, пропорциональное скорости. движения по-. езда на зеленый сигнал светофора.

Необходимость этого обусловлена тем, что при прохождении j-м поездом перегона отсутствует его влияние на следующие поезда.

В момент совпадения значений напряжений U и U< t;t), соответствующий прохождению j-м поездом перегона, на выходе схемы 19 сравнения устанавливается уровень напряжения, соответствующий логической единице. Этот сигнал подается на вход останова блока 1 1, прекращая запись реализации U >(t), а также на вход элемента И 24 и приводит его к срабатыванию. При подаче сигнала на вход останова блока 11 происходит останов записи и возврат магнитного накопителя в.исжодное состояние, характеризуемое U (t)=0.

196909 4

В момент достижения накопителем исходного состояния на первом выходе блока 11 появляется единичный сигнал, поступающий на первый вход триггера 22 и переводящий устройство в подготовительный такт.

Отличие режима работы устройства при втором положении триггера 20 состоит в том, что нулевой сигнал с его

10 первого выхода закрывает элементы

И 6, а единичный сигнал с выхода элемента И 21 открывает элемент И 7 на все время моделирования процесса движения. поездов, независимо от раз а ности напряжений 0 tу.i(t) и U> (t).

Этот режим моделирования используется для получения "опорной" реализации моделирования (реализации про20 цесса движения по участку первого поезда ), для имитации процессов движения поездов на участках с небольшими размерами движения поездов

I при отсутствии их взаимного влия25 ния- ).

После воспроизведения определенного количества реализаций случайных процессов движения поездов находят статистические оценки задержек

3Q поездов, характеризующие степень влияния случайных отклонений скоростей движения от расчетных нормати-, вов на результаты эксплуатационной работы.

ВНИИПИ Заказ 7567/50 Тираж 709 Подписное

Филиал ППП Патент", r.ÓIãîðîä, ул.Проектная, 4