Устройство для деления двоичных чисел

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) Ф е (50 4 С 06 Е 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3773173/24-24 (22) 20.07.84 (46) 07.01.86. Бюл. 1(- 1 (71) Ордена Ленина институт кибернетики им. В.M.Ãëóøêoâà (72) М.В.Семотюк, В.Д.Троц и H.H.Pûжов (53) 681.325(088.8) (56) Карцев М.А. Арифметика цифровых машин. -M. Наука, l969, с. 494, Авторское свидетельство СССР

1(- 589611, кл. С Об F 7/52, 1974. (54)(57) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

ДВОИЧНЫХ ЧИСЕЛ, содержащее сумматор, регистры делителя и делимого, информационные входы которых соединены соответственно с входами дели- теля и делимого устройства, о т л ич а ю щ е е с я тем, что, с целью . сокращения аппаратурных затрат, в него введены группа элементов И, преобразователь унитарного кода в двоичный, регистр коррекции, вспомогательный регистр, генератор тактовых импульсов, два счетчика, дешифратор и блок управления, который содержит пять триггеров, десять элементов И и три элемента ИЛИ, причем выход старшего разряда регистра делимого соединен с входом младшего разряда сумматора и первым информационным входом вспомогательного регистра, выход которого соединен с первым информационным входом сумматора, выход которого соединен с вторым информационным входом вспомогательного регистра, а второй информационный вход — по схеме монтажного ИЛИ с выходами регистра коррекции и преобразователя уннтарнога кода в двоичный, вход которого соединен с выходами элементов И группы, первь е входы которых соединены с выходами регистра делителя. а вторые входы — с выхадамн первого счетчика и выходам -езультата устройства, вход сброса которого соединен с входом сброса второго счетчика, выход которого соединен с входам дешифратора, выход которого соединен с входом запуска генератора тактовых импульсов и входами сброса первого и второго триггеров блока управления, вход сброса третьего триггера которого соединен с выходом переноса сумматора, входы записи регистров делителя, коррекции, делимого и входы сброса первого

*счетчика и вспомогательного регист ра соединены с первыми входами перваго и второго элементов ИЛИ блока управления и выходом первого элемента И блока управления, выход третьего элемента ИЛИ которого соединен с входом записи вспомогательного регистра, вход сдвига которого соединен с выходом второго элемента И блока управления, первый вход которого соединен с вторым входом второго элемента ИЛИ блока управления, выходам третьего элемента И блока управления, счетным входом второго счетчика и входом сдвига регистра делимого, выход четвертого элемента

И блока управления соединен с входом сдвига первого счетчика, вход вычитания единицы которого соединен с

1203514 выходом пятого элемента И блока управления, инверсный выход четвертого триггера которого соединен с входом выборки преобразователя унитарного кода в двоичный, выход разрешения коррекциирегистра коррекции соединен с прямым выходом четвертого триггера блока управления и первыми входами шестого и седьмого элементов

И блока управления, а в блоке управления вход установки первого триггера соединен с первыми входами первого и восьмого элементов И и первым выходом генератора тактовых импульсов, второй выход которого соединен с первыми входами девятого и десятого элементов И, а третий выход — с входом установки второго триггера, первым входом третьего элемента И и вторым входом седьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, второй вход которого соединен с вторым входом третьего элемента И, первым входом

Изобретение относится к цифровой вычислительной технике и может быть использовано для построения цифровых вычислительных машин.

Цель изобретения — сокращение аппаратурных затрат.

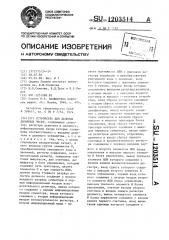

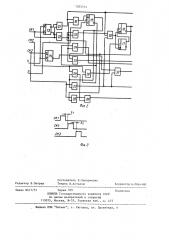

На фиг. 1 показана схема устройства для деления двоичных чисел; на фиг. 2 — схема блока управления; на фиг. 3 — временная диаграмма работы генератора тактовых импульсов.

Устройство для деления (фиг.1) содержит регистр 1 делимого, регистр

2 делителя, первый счетчик 3, сумматор 4, вспомогательный регистр 5, регистр б коррекции, группу 7 элементов И, преобразователь 8 унитарного кода в двоичный, генератор 9 тактовых импульсов, блек 10 управления, второй счетчик 11, дешифратор 12.

Блок 10 управления (фиг.2) содержит пять триггеров 13 — 17, три четвертого элемента И и прямым выходом третьего триггера, вход установ. ки которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с вторыми входами четвертого и шестого элементов И, первым входом пятого элемента И и выходом восьмого элемента И, второй вход которого соединен с прямым выходом первого триггера, инверсный выход которого соединен с вторым входом первого элемента И, инверсный выход второго триггера соединен с вторым входом второго элемента И, второй вход пятого элемента И соединен с инверсным выходом третьего триг— гера и вторым входом десятого элемента И, выход которого соединен с входом установки пятого триггера, прямой выход которого соединен с входом установки четвертого триггера вход сброса которого соединен с входом сброса пятого триггера и выходом второго элемента ИЛИ, третий вход которого соединен с выходом шестого элемента И.

2 элемента ИЛИ 18 — 20, десять элементов И 21 — 30.

Регистр 1 делимого, вспомогательный регистр 5 и счетчик 3 выполнены сдвигающими.

Устройство работает следующим образом.

Сбрасывается счетчик 11, и через дешифратор 12 разрешается работа ге10 нератора 9. По первым трем импульсам

СИ1, СИ2, СИЗ записывается делимое, делитель сбрасывает счетчик 3, уста— навливается регистр 6 коррекции, сбрасывается вспомогательный регистр 5.

15 Затем записывается код с сумматора 4 во вспомогательный регистр 5, после чего происходит сдвиг на один разряд влево в регистре 5 и в регистре 1 делимого. После начальной установки

2G устройство отрабатывает N циклов определения разрядов частного. Каждый цикл состоит из шагов,.количество которых определяется наличием инверсии переноса из сумматора.

По СИ1 в блоке 10 управления выдается импульс сдвига, по которому в счетчик 3 записывается предлагаемый разряд частного, который всегда равен единице. Код делителя и код со счетчика 3 поступают на входы группы 7 элементов И. Образованный унитарный код преобразуется в преобразователе 8 унитарного кода в двоичный.

Полученный код суммируется с кодом всломогательного регистра 5 на сумматоре 4.

Если отсутствует инверсия переноса из старшего разряда сумматора 4, то по СИ2 из блока 10 управления поступает импульс записи, по которому во вспомогательный регистр 5 записывается сумма, а по СИЗ сдвигается регистр 1 делимого.

Если присутствует инверсия переноса, то это говорит о том, что разряд частного определен неверно. Тогда йо очередному СИ1 блок 10 управления выдает импульс вычитания единицы в счетчике 3 и образованный в нем новый код, проходя через группу 7 элементов И, преобразователь 8 унитарного кода в двоичный, суммируется с кодом вспомогательного регистра 5 на сумматоре 4.Если отсутствует инверсия переноса, что говорит о том, что разряд определен

2035 1 ч 4 верно, то по СИ2 импульс записи блока 10 управления записывает полученную сумму во вспомогательный регистр 5, а по СИЗ сдвигается регистр 1 делимого на один разряд влево.

Если же вновь присутствует инверсия переноса то была допущена ошибка в (И вЂ” 1) — м или (q-2) -м разряде, где И -определяемый разряд частного. Тогда по СИ2.прекращается поступление импульсов выборки преобразователя 8 унитарного кода в двоичный, а на входы сумматора 4 поступает код с регистра 6 коррекции, в котором записана двоичная двойка. По СИЗ происходит запись суммы кода коррекции с кодом вспомогательного регистра 5 в этот регистр.

По очередному СИ1 вычитается едини.ца из счетчика 3. По СИ2 новая сумма записывается во вспомогательный регистр 5, а по СИЗ сдвигается регистр 1 делимого.

Счетчик 11 после каждого сдвига делимого увеличивается на единицу.

После того, как счетчик 11 сосчитает (-1) цикл, где — разрядность частного, дешифратор 12 за30 прещает работу генератора 9.

1203514

Составитель Е.Захарченко

Техред И.Асталош

Корректор А.Обручар

Редактор В.Петраш

Заказ 8417/51

Тираж 709

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4