Матричный коммутатор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Л0„„1210218 А (51)4 Н 03 К 17/62

/ з,„„

/7 „. :, .я .

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3762868/24-21 ,(22) 29.06.84 (46).07.02.86. Бвл, ¹ 5 (72) P.Ñ. Кильметов, А.Г. Краснопольский, P À. Лашевский, Е.Б. Механцев, Э.Э. Тенк и B.С. Хорик (53) 621.382(088.8) (56) Электроника, 1975, т. 48, № 12, с, 48.

Макаревич О.Б. и др. МДП БИС для коммутационных систем телефонии.

Зарубежная электронная техника, 1977, ¹- 15, с. 62. (54)(57) МАТРИЧНЬП1 КОММУТАТОР, содержащий N горизонтальных и М вертикальных информационных шин, в каждой точке пересечения которых расположен запоминающий элемент, выход которого соединен с входом ключевого элемента, включенного между соответствующими вертикальными и горизонтальными информационными шинами М резисторов, каждый из которых включен между соответствующей вертикальной шиной и шиной источника питания, дешифратор выборки по вертикали, входы которого соединены с вертикальными входными шинами, а выходы — с вертикальными входами соответствующих запоминающих элементов, дешифратор выборки по горизонтали, входы которого соединены с горизонтальными входными шинами, а выходы — с горизонтальными входами соответствувщих запоминающих элементов, шина управления, шина синхронизации, а также выходные шины, о т л и ч а— ю шийся тем, что, с целью расширения функциональных возможностей, в него введены два элемента ИЛИ-НЕ, инверсная шина управления и инверсная шина синхронизации, прямая и инверсная тактовые шины, а также hh выходных устройств, каждое из которых содержит два 1/ -триггера и элемент ИЛИ-НЕ, выход которого соединен с R -входом второго2-триггера, выход которого соединен с соответствующей выходной шиной, ale -вход — с выходом первогоП-триггера, 2 -вход которого соединен с соответствующей вертикальной информационной шиной и с первым входом элемента

ИЛИ-HE каждого выходного устройства, второй вход которого соединен с шиной управления, причем С -входы первого и второго Х>-триггеров соединены соответственно с прямой тактовой шиной, выходом первого элемента ИЛИ-НЕ и с инверсной тактовой шиной, выходом второго элемента ИЛИ-НЕ, первый вход которого объединен с первым входом первого элемента ИЛИ-НЕ,5 -входом второго

2-триггера и с инверсной шиной управления, а второй вход соединен с шиной синхронизации, инверсная шина синхронизации соединена с вторым входом первого элемента ИЛИ-НЕ.

1

Изобретение относится к импульснои технике в частности к электрон", ным коммутаторам, и может использоваться для автоматического синхронного переключения цепей в зависимости от управляющей информации.

Цель изобретения — расширение функциональных возможностей путем обеспечения не только асинхронного, но и синхронного режима работы матричного коммутатора.

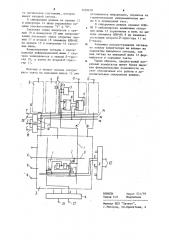

На чертеже представлена функциональная схема матричного коммутатора.

Матричный коммутатор соцержит запоминающий элемент 1, ключевой элемент 2, матрицу 3, дешифраторы 4 выборки по вертикали,,ценплфрВТор 5 Hb16opKH IIQ горизонтали, !! горизонтальных информационных шин 6, M вертикальных информационных шин 7, М выходных устройств 8, каждое из которых содержит элемент ИЛИ-НЕ 9, первый 10 и второй 112-триггеры, кроме того, матричный коммутатор содержит М выходных шин 12, прямую 13 и инверсную 14 шины управления, прямую 15 и инверсную !6 тактовые шины, первый 17 и второй 18 элементы ИЛИНЕ, прямую 19 и инверсную 20 шины синхронизации, вертикальные 21 и горизонтальные 22 входные шины, М резисторов 23.

В каждой точке пересечения вертикальной 7 и горизонтальной 6 информационных шин расположен запоминающий элемент 1, выход которого соединен с входом ключевого элемента 2, включенного между соответствующими вертикальной 7 и горизонтальной 6 информационными шинами. Каждый из М резисторов 23 соединен первым выводом с шиной ис"" точника питания, а вторым выводом -" с соответствующими входом элемента ИЛИ-НЕ 9, выходного устройства 8, 3-входом первого > -триггера. 10 и вертикальной шиной 7.

Другой вход элемента ИЛИ.-НЕ 9 соединен с шиной 13 управления, а выход — с l! -входом второго З -триггера 11, выход которого соединен с соответствующей выходной шиной 12.

Выход первогоЗ-триггера 10 соединен с Э -входом второго 0-триггера ill

С-вход которого соединен с инверс- ной тактовой шиной 16 и выходом вто2!0218

iD

I5

31) рого элемента ИЛИ-НЕ 18 первый вход которого соединен с первым входом пеового элемента ИЛИ-НЕ 17, инверсной шиной 14 управления и о-входом второго 0-триггера 11, С-вход первого .0 -триггера 10 соединен с выходом первого элемента KJJH-НЕ 17„ второй вход которого соединен с инверсной шиной 20 синхронизации. Прямая шина 19 синхронизации соединена с вторым входом второго элемента ИЛИ-НЕ 18.

Матричный коммутатор работает следующим образом, Б режиме настройки на вертикальные входные шины 21 поступают последовательно номера вьгходных шин 12, Одновременно на горизонтальные входные шины 22 поступают номера горизонтальных информационных шин 6, соединяемых с выбранной в данный момент выходной шиной 12.

В выбранный столбец N запоминающих элементов 1 записывается двоичылй код, состоящий из одной единицы и !1 -1) -го нуля, чем обеспечивается соединение с выбранной выходной шиной 12 только одной входной цепи.

После М тактов установления соединений по образованным каналам можно. передавать информацию.

Коммутируемый сигнал с горизонтальной информационной шины 6 через открытый ключевой элемент 2 поступает на вертикальную информацион. ную шину 7, Далее путь сигнала зависит от того, в каком режиме работает коммутатор.

В асинхронном режиме на прямой 1 и инверсной 14 шинах управления устанавливаются соответственно состояния "0" и "1". Поэтому, независимо от серии синхронизирующих импульсов, на прямой 19 и инверсной 20 шинах синхронизации устанавливаются логические "0" на прямой 15 и инверсных 16 тактовых шинах. Первый !0 и второй 1! Л -триггеры не воспринимают информацию по О-входам. Так как на втором входе элемента ИЛИ-НЕ 9 присутствует "0" то входной сигнал инвертируется и поступает íà J! -вход элемента ИЛИ-НЕ 9. При этом на 5 -входе этого триггера постоянно присутствует логическая "1". Поэтому второй 2-триггер ll устанавливается в

1210218 га г2 то логическое состояние, которое имеет входной сигнал.

В синхронном режиме на прямую 13 и инверсную 14 шины управления поданы соответственно "1" и "0".

Тактовая серия импульсов с прямой 19 и инверсной 20 шин синхронизации поступает через открытые первый 17 и второй 18 элементы ИЛИ-НЕ на прямую 15 и инверсную 16 тактовые шины.

Коммутируемые сигналы с вертикальной информационной шины 7 сначала записываются в первый П-триггер 10, а затем во второйП -триггер 11.

Поэтому в момент начала следующего такта на выходных шинах 12 уже установится информация, поданная на горизонтальные информационные шины 6 в предыдущий такт.

В синхронном режиме элемент ИЛИ»

НЕ 9 заблокирован. единичным сигналом шины 13 управления и нуль на вы ходе элемента KIH-HE.9 не изменяет состояние второго 4 -триггера 11 по

R -входу.

ip Задержка распространения сигнала по каналу коммутатора не влияет на параметры выходного сигнала, так как сигнал на выходной шине 12 формируется в середине такта.

Таким образом, предлагаемый матричный коммутатор имеет более широкие функциональные возможности за счет обеспечения его работы в дополнительном синхронном режиме.

ИИПИ Заказ 531/59 аж 818 Подписное филиал ППП "Патент г.ужгород, ул..Проектная, 4