Устройство для подключения к магистрали

Иллюстрации

Показать всеРеферат

Устройство относится к вычислительной технике и может, быть использовано при проектировании цифровых интегральных схем. Цель изобретенияповышение быстродействия и надежности подключения к магистрали. Устройство содержит элементы НЕ, триггер, элемент И-НЕ, элемент ИЛИ-НЕ и формирователь уровня выходного сигнала, выполненный на МДП-транзисторах.З ил. to ND О) 4: С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 С 06 F 13/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОсудАРственный кОмитет сссР пО делАм изОБРетений и ОтнРытий (21) 3801277/24-24 (22) 11.10.84 (46) 23,04.86. Бюл. Р 15 (72) Е.А.Комаров, А.И.Моторин и В.В.Теленков (53) 681.3 (088.8) (56) Патент Японии У 56-7331, кл. Н 03 К 19/00, опублик. 1981.

Авторское свидетельство СССР

1(73284 1, кл. G 06 F 3/04, 1980. (54) УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ К

МАГИСТРАЛИ (57) Устройство относится к вычислительной технике и может. быть использовано при проектировании цифровых интегральных схем. Цель изобретенияповышение быстродействия и надежности подключения к магистрали. Устройство содержит элементы НЕ, триггер, элемент И-НЕ, элемент ИЛИ-НЕ и формирователь уровня выходного сигнала, выполненный на МДП-транзисторах.3 ил.

1226480

Изобретение относится к вычислительной технике и может быть использовано при проектировании цифровых интегральных схем, Цель изобретения — повышение быстродействия и надежности подключения к магистрали.

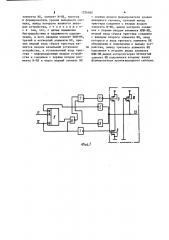

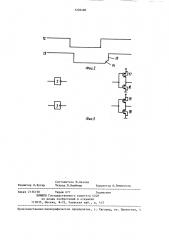

На фиг ° 1 представлена функциональная схема устройства; на фиг.2 — временная диаграмма работы устройства; на фиг.3 — электрическая схема двух элементов НЕ.

Устройство содержит элементы НЕ

1-4, триггер 5, элемент И-НЕ 6, элемент ИЛИ-НЕ 7, п-канальный МДП-транзистор 8, первый р-канальный МДПтранзистор 9, второй р-канальный МДПтранзистор 10,. транзисторы 8-10 образуют формирователь уровня выходного сигнала, шину управления 11, информационную шину 12, выход 13 устройства.

На фиг.2 отмечены участки фронта 14 и 15. Устройство (фиг.3) также содержит и-канальный МДП-транзистор 16, р-канальный МДП-транзистор 17 элемента НЕ 2 и и-канальный МДП-транзистор 18, р-канальный МДП-транзистор 19 элемента НЕ 3, Устройство работает следующим образом.

После включения питания на вход 12 поступает уровень логической "1", который возбуждает элемент HE 1,на выходе которого устанавливается уровень логического "0", и.транзистор 8 закрывается. На вход 11 подается импульс, сбрасывающий триггер 5 и устанавливающий устройство в исходное состояние, При этом на выходе триггера 5 устанавливается уровень логического "0". Возбуждаются элементы И-НЕ 6, ИЛИ-НЕ 7, НЕ 4, и транзистор закрывается. На выходе 13 формируется уровень логической "1" за счет постоянно включенного высокоомного транзистора 10.

Выдаче логического "0" соответствует поступление логического "0" на вход 12. При этом на выходе тригге11 11 ра 5 устанавливается логическая 1

Возбуждается элемент НЕ 1 и транзистор 8, который включается, и на выходе 13 формируется уровень логического "0",а на выходе элементов НЕ " и 3 — уровень логической "1". После окончания выдачи нуля на вход 12 noI 1 11 ступает уровень логическои 1

На. выходе элемента НЕ 1 и выходе элемента И-НЕ 6 формируется уровень. логического "О". Транзистор 8 закрывается и на выходе 13 начинает формироваться уровень логической "1"

ИЛИ-НЕ 7 и транзистор 9 закрывается.

На выходе 13 поддерживается уровень логической "1 I за счет постоянно — г1 включенного высокоомного транзисто30 ра. Разница в порогах срабатывания элементов НЕ 2 и 3 достигается смещением переходных характеристик данных элементов за счет соотношения размеров р- и и-канальных МДП-транзисторов, Если на выходе 13 формируется уровень логического "011 каким-либо другим элементом, объединенным по выходу с данным, то транзистор 9 не включается в рассматриваемом устройстве, так как триггер 5 сбро№О шен и на его выходе поддерживается уровень логического "0". При выдаче информации из параллельно включенных, объединенных о выходу (3 устройств, участок фронта 14 (фиг.2) обеспечивает синхронизацию формирования активного фронта (из состояния логического "0" в состояние логической "1") тогда,, когда и-канальные МДП-транзисторы 8 всех устройств выключены, 50 что существенно влияет на надежные характеристики и повышает быстродействие устройства в целом.

Формула и з о б р е т е н и я

Устройство для подключения к магистрали„ содержащее первый и второй за счет высокоомного транзистора 10 (фиг,2, участок фронта 14). Когда . уровень логической "111 на выходе 13

1Î достигает порога сбрасывания элемента НЕ 3, на его выходе формируется уровень логического "0", который поступает на вход элемента ИЛИ-НЕ 7.

На выходе элемента ИЛИ-НЕ 7 формируется уровень логической "1". Возбуж-!

5 дается элемент НЕ 4, транзистор 9 открывается, н уровень логической "1" на выходе 13 формируется активно (фиг.2; участок фронта 15). При достижении порога сбрасывания элемента НЕ 2, который выбран выше, чем у элемента HE 3, íà его выходе устанавливается уровень логического "0", триггер 5 переключается,и на его выходе формируется уровень логического "0".

Возбуждаются элементы И-НЕ 6, 1226480 элементы НЕ, элемент И-НЕ, триггер и формирователь уровня выходного сигнала, выход которого является выходом устройства, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия и надежности подключения, в него введены элемент ИЛИ-HF, третий и четвертый элементы НЕ, причем первый вход сброса триггера является входом начальной установки устройства, а установочный вход триггера — информационным входом устройства и соединен с первым входом элемента И-НЕ и через первый элемент НЕ с первым входом формирователя уровня выходного сигнала, нулевой выход триггера соединен с вторым входом элемента И-НЕ, выход которого соединен с первым входом элемента ИЛИ-НЕ, второй вход сброса триггера соединен с выходом второго элемента НЕ, вход которого и вход третьего элемента НЕ объединены и подключены к выходу уст30 ройства, выход третьего элемента HE подключен к второму входу элемента

ИЛИ-НЕ,выход которогочерез четвертый элемент. HE подключенк второму входу формирователя уровнявыходного сигнала.

122б480

Составитель И.Хазова

Техред Л.Олейник Корректор А.Зимокосов

Редактор О.Бугир

Заказ 2136/50 . Тираж б7! Подпйсное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4