Многоканальное мажоритарно-резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам с контролем и может быть использовано при построении высоконадежных вычислительных систем. Цель изобретения состоит в повьшении надежности устройства за счет обеспечения контроля его работоспособности . Устройство состоит из трех каналов, дешифратора, причем каждый из каналов содержит основной и резервньй блоки памяти, первьй и второй сумматоры, блок сравнения, мажоритарный элемент. Сигналы с блоков сравнения каждого канала поступают на входы дешифратора, которьш формирует на своих выходах сигналы неисправности соответствующего блока памяти . Изобретение является дополнительным к основному авт. св. № 1182581. 1 ил. S (Л te F 00 00 СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН. SU l 234885 (5П 4 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1182581 (2 I ) 3705591/24-24 (22) 20.02.84 (46) 30.05.86. Бкл. У 20 (72) В.А.Шастин, И.И.Клепиков, В:П.Петровский и Г.В.Дворецкий (53) 681.327.6 (088.8) .(56) Авторское свидетельство СССР

Р 1182581, кл. С 11 С 29/00, 1983. (54) МНОГОКАНАЛЬНОЕ МАЖОРИТЛРНОРЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам с контролем и может быть использовано при построении высоконадежных вычислительных систем. Цель изобретения состоит в повышении надежности устройства за счет обеспечения контроля егоработоспособности. Устройство состоит из трех каналов, дешифратора, причем каждый из каналов содержит основной и резервный блоки памяти, первый и второй сумматоры, блок сравнения, мажоритарный элемент. Сигналы с блоков сравнения каждого канала поступают на входы дешифратора, который форми— рует на своих выходах сигналы неис- правности соответствующего блока памяти. Изобретение является дополнительным к основному авт.св. N- 1182581.

1 ил.

1234885

Изобретение относится к запоминающим устройствам с контролем, может быть использовано при построении выл соконадежных вычислительных систем и является дополнительным к основному авт. св. Р 118258 1.

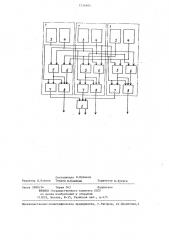

Цель изобретения — повышение надежности устройства за счет обеспечения контроля его работоспособности, На чертеже приведена функциональная схема многоканального мажоритарно-резервированного запоминающего устройства, когда число каналов устройства равно трем.

Устройство состоит из трех кана-. лов 1 и дешифратора 2, причем каждьй из каналов 1 содержит основной 3 и резервный 4 блоки памяти, первый 5 и второй 6 сумматоры, блок 7 сравнения и мажоритарньй элемент 8. 20

Устройство работает следующим образом.

Пусть в основных блоках 3 памяти записана:информация: "а" — в первом канале; "в" — во втором канале; "с"— в третьем канале. Тогда в резервных блоках 4 памяти записана следующая информация (равная поразрядной сумме по модулю два информации основных

3 блоков памяти данного и последую- 30 щего каналов): "а+в"- — в первом кана1 1т ле; "в+с" — во втором канале; с+а в третьем канале.

При обращении к устройству в случае отсутствия неисправности на входы >5 мажоритарного элемента 8 первого каI I 11 нала попадает информация: а — с выхода основного 3 блока памяти; (а(9в) +) (++a-=a — с выхода первого 5 сумматора; (с®а)Ос=а — с выхода второго сумма- щ тора.

Аналогично на входы мажоритарных элементов 8 остальных каналов поступает информация "в" и "с". Одновре— менно на соответствующие входы блоков сравнения 7 поступает одинаковая информация с выходов основного блока 3 памяти и первого сумматора 5.

На входы дешифратора в этом случае поступают сигналы сравнения от блоков 7 сравнения всех каналов. Б итоre на информационных выходах устройства через мажоритарные элементы 8 появляется достоверная информация а, в, "с", а на контрольных выходах (выходы дешифратора 2) — информация об отсутствии неисправностей в устройстве.

Прн наличии неисправностей в основном блоке 3 памяти первого канала на входы дешифратора 2 поступают сигналы несравнения от блоков 7 сравнения первого и третьего каналов. При неисправности основного блока 3 па— мяти второго или третьего каналов на входы дешифратора 2 посту-пают сигналы несравнения от блоков 7 сравнения соответственно первого и второго или второго и третьего каналов, При неисправности резервного блока 4 памяти первого канала на входы дешифратора 2 поступает сигнал несравнения только от блока 7 сравнения первого канала. Аналогично при неисправности резервного блока 4 памяти второго или третьего каналов на входы . дешифратора 2 поступает сигнал неисправности от блока сравнения соответственно второго или третьего каналов.

Б соответствии с этими сигналами дешифратор ? формирует на контрольных выходах устройства Сигналы неисправности соответствующего блока памяти.

Формула и з о б р е т ения

Многоканальное мажоритарно-резервированное запоьжнающее устройство по авт. св. N - 1182581, о т л и ч а— ю щ е е с я тем, что, с целью повышения надежности устройства за счет обеспечения контроля его работоспособности, оно содержит дешифратор и в каждом канале блок сравнения, причем первый вход блока сравнения каждого канала подключен к выходу основного блока памяти, а второй вход к выходу первого сумматора данного канала, вйходы блоков сравнения соединены с входами дешифратора, выходы которогс являются контрольными выходами устройства.

Составитель О. Кулаков

Редактор В.Ковтун Техред Л.Олейник Корректор В.Бутяга

Заказ 2988/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

П оизводственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4