Устройство для выборки команд

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в качестве блока предварительной выборки команд ЦВМ. Цель изобретения - увеличение быстродействия устройства для выборки команд. Устройство содержит первый , второй и третий счетчики, блоки памяти, элемент И, блок хранения команд и формирования управляющих сигналов , первый и второй сумматоры, дешифратор , первьЕй и второй блоки элементов НЕ, зЛемент НЕ. Введение перво - го и второго блоков элементов НЕ, элемента НЕ, дешифратора, первого и второго сумматоров, блока хранения команд и формирования управляющих Сигналов обеспечивает достижение цели . 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ БЛИН

А1

Л0 12592 (594 G 06

E

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР пО делАм изОБРетений и ОтнРытий (21) 3811073/24-24 (22) 10.11.84 (46) 23.09.86. Бюл. У 35 (72) В. Ве Роэдобара, А. Ю. Веревкин, Г. В. Кремез и В. Н. Петрунек (53) 681,32(088,8) (56) Королев Л. И. Структуры ЭВМ и их математическое обеспечение, — М.:

Наука, 1978.

Авторское свидетельство СССР

Н 1149257, кл, G 06 F 9/56, 1983, (54) УСТРОЙСТВО ДЛЯ ВЫБОРКИ КОМАНД (57) Изобретение относится к области цифровой вычислительной техники и может быть использовано в качестве блока предварительной выборки команд

ЦВМ. Цель изобретения — увеличение быстродействия устройства для выборки команд. Устройство содержит первый, второй и третий счетчики, блоки памяти, элемент И, блок хранения команд и формирования управляющих сигналов, первый и второй сумматоры, де- шифратор, первый и второй блоки элементов НЕ, элемент НЕ. Введение перво— го и второго блоков элементов НЕ, элемента НЕ, дешифратора, первого и второго сумматоров, блока хранения команд и формирования управляющих сигналов обеспечивает достижение цели. 2 ил.

1259263

25

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве блока предварительной выборки команд ЦВМ, к которым предъявляются высокие требования по быстродействию и ограничения на аппаратурные затраты (энергопотребление).

Цель изобретения — повышение быстродействия устройства для выборки команд.

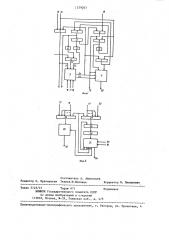

На фиг, 1 приведена функциональная схема устройства для выборки команд; на фиг. 2 - функциональная схема блока хранения команд и формирования управляющих сигналов.

Устройство (фиг, 1) содержит счетчики и 2, блок 3 хранения команд и формирования управляющих сигналов, блок 4 памяти, счетчик 5, элемент И 6, сумматор 7, дешифратор 8, блоки элементов HE 9 и 10, элемент НЕ 11, сумматор 12, вход 13 адреса группы команд, вход 14 запроса группы команд, тактовый вход 15, входы 16-18 адреса, длины и запроса команды абонента, сигнальный выход 19, выход 20 устройства, входы

21-23 и выходы 24 и 25 блока 3.

Блок хранения команд и формирования управляющих сигналов (фиг. 2) содержит коммутаторы 26 и 27, блок 28 памяти, счетчик 29, дешифратор 30 и микропрограммный автомат 31 (МПА).

Устройство работает слудующим образом, В начальный момент на вход 13 устройства подается адрес начала группы команд, подлежащей выборке.

По сигналу на входу 14 этот адрес записывается в счетчик 2, а счетчики и 5 обнуляются, Если объем блока 4 памяти составляет и ячеек, то разрядность счетчиков 1 и 5 равна) Lnp: и(+1, где )x(— ближайшее целое чйсло, больше или равное х.

)Lop n(младших разрядов счетчиков и 5 поступают на адресные входы записи и чтения блока 4 памяти.

Заметим, что адрес записи в счетчике 1 всегда больше или равен адресу чтения в счетчике 5. FIa сумматоре 7 вычисляется разность между полноразрядными содержимыми счетчиков i и 5 путем сложения по модулю ()Lop;n(+

+1) кода со счетчика 1 с инверсным кодом со счетчика 5 и добавлением единицЫ в младший разряд сумматора, Если разность содержимых счетчиков 1 и 5 равна нулю, что определяе ся дешифратором 8, то блок 4 памяти пуст, и с выхода дешифратора 8 на вход элемента И 6 поступает сигнал запрета. Сигналы запроса на команду с входа 15 не проходят через элемент И 6 и удовлетворяются, Если разность содержимых счетчиков 1 и 5 не равна п, т.е, блок 4 памяти не заполнен полностью командами, то с выхода дешифратора 8 через элемент НЕ 10 на вход 23 блока 3 поступает сигнал запроса на обслуживание устройства. На вход 22 блока 3 с выхода сумматора 12 поступает код, равный числу свободных ячеек в блоке 4 памяти, которое равно разности между кодом п, который задается на входе сумматора 12, и кодом разности содержимых счетчиков 1 и 5, Микропрограммный автомат 31 анализирует поступление запроса от устройства для выборки команд на входе 23 и от других абонентов на входе 18.

Если на входе 18 есть запросы, то

MIIA âûïoëíÿâòñÿ микропрограммы их обслуживания. После обслуживания всех запросов на входе 18 МПА 31 переходит к обслуживанию запроса устройства. На выходе 33 МПА формируется адрес канала коммутаторов 26 и 27, соответствующий входам 21 и 22, .вследствие чего на адресный вход блока 28.памяти поступает адрес начала команд, а в счетчик 29 записывается код длины считывания групп команд. Ло сигналу с выхода 34 МЛА выполняется считывание одной команды с блока 28, которая поступает на выход 25. По сигналу на выходе 24

MIA эта команда записывается в блок4 памяти по адресу, находящемуся в

) оя nj младших разрядах счетчика 1.

По заданному фронту этого сигнала адрес в счетчиках 1 и 2 увеличивается на единицу.

Следукщим сигналом на выходе 32

МПА из счетчика 29 вычитается единица. Если его содержимое не равно нулю, что определяется дешифратором 30, то считывается следующая команда.

В противном случае МПА 31 переходит к обслуживанию других запросов.

Если блок 4 памяти не пуст. то запрос на команду с входа 15, проидя через элемент И 6, поступает на вход чтения блока 4 памяти, выдает

l 25 на выход 20 команду, хранящуюся по адресу счетчика 5, и поступает на выход 19 в качестве строба выдачи.

По заднему фронту этого сигнала адрес в счетчике 5 увеличивается на единицу.

Формула и э обретения

Устройство для выборки команд, со- 10 держащее три счетчика, два блока памяти и элемент И, первый вход которого соединен с тактовым входом устройства, выход элемента И соединен со стробирующим выходом устройства, <5 с входом чтения первого блока памяти и со счетным входом первого счетчика, запросный вход устройства соединен с входами сброса первого и второго счетчиков и с входом записи 20 третьего счетчика, выходы первого и второго счетчиков соединены соответственно с входом адреса чтения и входом адреса записи первого блока памяти, выход которого соединен с . 25 информационным выходом устройства вход адреса группы команд устройства соединен с информационным входом третьего счетчика, выход второго блока памяти соединен с информацион- 3р ным входом первого блока памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него дополнительно введены два блока элементов НЕ, элемент НЕ, два дешифратора, два коммутатора, четвертый счетчик, микропрограммный автомат и два сумматора, причем выход первого счетчика соединен с входом первого блока элементов НЕ, выход которого и выход второго счетчика соединены

9263 4

1 соответственно с первым и вторым входами iiepaoro сумматора, выход которого соединен с входом второго блока элементов.НЕ и с входом первого дешифратора, первый и второй выходы которого соединены соответственно с вторым входом элемента И и входом элемента HE выход которого соединен с первым входом логических условий микропрограммного автомата, выход второго блока элементов НЕ соединен с первым входом второго сумматора, выход второго сумматора соединен с первым информационным входом первого коммутатора, выход которого соединен с информационным входом четвертого счетчика, выход которого соединен с входом второго дешифратора, выход которого соединен с входом останова микропрограммного автомата, первый, второй и третий управляющие выходы которого соединены соответственно с вычитающим входом четвертого счетчика, с управляющими входами первого и второго коммутаторов и с микровходом второго блока памяти, четвертый управляющий выход микропрограммного автомата соединен с входом записи первого блока памяти и со счетными входами второго и третьего счетчиков, вход адреса группы команд и вход кода записи группы команд устройства соединены соответственно с первым информационным входом второго коммутатора и вторым информационным входом первого коммутатора, выход третьего счетчика соединен с вторым информационным sxoдом второго коммутатора, выход которого соединен с адресным входом второго блока памяти, 1259263 I

20!

Фиа!

27 7б

Фиг. 2

Проиэводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель А. Афанасьев

Редактор О, Юрковецкая Техред И.Попович

Заказ 5123/47 Тираж 671

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий.1!3035, Москва, Ж-35, Раушская наб,, д„ 4/5

Корректор Л. Пилипенко

Подписное