Устройство для контроля бис

Иллюстрации

Показать всеРеферат

Изо ретеиие относится к цифровой вычислительной технике и может быть использовано при проектировании самоконтролируемых больших и сверхбольших интегральных схем для цифровых вычислительных машин и систем. Цель изобретения - повьппение полноты контроля и увеличение контролепригодности / упрощение процесса контроля/. . Устройство для контроля БИС содержит дешифратор номеров выводов, блок синхронизации, две группы блоков элементов И, коммутатор контрольных кодов, блок анализа результата, блок переключателей пар вьшодов, группу входных коммутаторов. Данное техническое решение обеспечивает более высокую полноту и достоверность контроля выводов БИС и исключает пропуск константных неисправностей. Кроме того упрощается процесс контроля благодаря приспособленности схемы к про (Л верке йьшодов БИС путем коммутации ее входов и выходов. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОНЕТСМИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1264181 (511 4 G 06 F ll/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,: 11

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3750835/24-24 (22) 30.05.84 (46) 15.!0.86. Бюл. У 38 (72) Б.О.Сперанский, В.С.Харченко, Г.Н.Тимонькин, В.П.Улитенко, С.Н.Тка-. ченко и В.Б.Самарский (53) 681.3(088.8). (56) Авторское свидетельство СССР

У 1049912, кл. G 06 F !1/00, 1982.

Патент CltIA Ф 4216539, кл. G 01 R 31/28, !980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БИС (57$ Изобретение относится к цифров ой вычислительной технике и может быть использовано прн проектировании самоконтролируемых больших и сверхбольших интегральных схем для цифровых вычислительных машин и систем. Цель изобретения — повышение полноты контроля и увеличение контролепригодности (упрощение процесса контроля/.

Устройство для контроля БИС содержит дешифратор номеров выводов, блок синхронизации, две группы блоков элементов И, коммутатор контрольных кодов, блок анализа результата, блок переключателей пар выводов, группу входных коммутаторов. Данное техни.ческое решение обеспечивает более высокую полноту н достоверность контроля выводов БИС и исключает пропуск константных неисправностей. Кроме того упрощается процесс контроля благодаря приспособленности схемы к проЯ верке выводов БИС путем коммутации ее входов и выходов. 1 э.п. ф-лы, 3 ил., 1264181

Изобретение относится к цифровой вычислительной технике и может быть, использовано при проектировании само. контролируемых больших и сверхбольших интегральных схем для цифровых вычислительных машин и систем.

Цель изобретения — повышение полноты контроля и увеличение контролепригодности (упрощение процесса контроля).

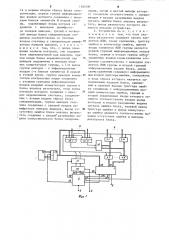

На фиг.l представлена схема устройства; на фиг.2 — схема блока анализа результата; на фиг.3 — схема блока синхронизации.

Устройство содержит блок 1 анализа результата, блок 2 синхронизации, блоки 3.1 — З,N и 4 .1-4.N элементов И первой и второй групп, вход

5 начальной установки, вход 6 пуска, информационные входы 7 и выходы 8 устройства, выход 9 результата, счетчик 10,,цешифратор 11 номеров выводов, вхоцные коммутаторы 12.1 — 12.N группы, коммутатор 13 контрольных кодов, блок 14 задания контрольных кодов, блок 15 переключателей пар

Вь1водов.

Блок 1 анализа результата (фиг.2) содержит коммутатор 16 ошибки, триггер 17 ошибки, схему 18 сравнения, группу элементов ИЛИ 19, вторую 20 и первую 21 группы информационных входов, синхровход 22.1 и вход 22.2 разрешения выдачи сигнала ошибки,:вход

23 конца контроля, выход 24 отсутствия ошибки.

Блок 2 синхронизации (фиг. 3) содержит первый 25, третий 26, вто- ° рой 27, четвертый 28 выходы„второй вход 29 сброса, генератор 30 импульсов, триггеры 31-33, дешифратор 34, элемент ИЛИ 35, элементы И 36 и 37.

Контроль целостности выводов модуля БИС устройства осуществляется следующим образом.

Цикл проверки пары выводов модуля

БИС состоит из двух тактов. В первом такте с прямого выхода блока 14 через коммутатор 13 и соответствующий коммутатор 12 группы прямой конгрольный код с выхода устройства поступа- ет на соответствующий вход блока 15. .Кроме того, этот код поступает с выхода коммутатора 13 на вход блока

Контрольный код, пройдя через блок 15, поступает на вход соответствующих блоков З.i и 4.i элементов

I5

5G

-с

И и далее на вход блока 1. В блоке 1 происходит сравнение кодов, поступивших на его входы. В первом такте первого цикла путем сравнения значений прямого кода, выданного с выхода БИС и полученного на ее входе, происходит проверка соответствующей пары выводов на предмет отсутствия (наличия) в них неисправностей типа константа 1 или константа 0 .

При этом, есл.- . в прямом коде значение i-гс разряда равно "0, то в результате проверки обрыв одного выхода контролируемого вывода будет обнаружен, так как в этом случае значение i-ro разряда в коде, поступившем на вход БИС, равно

В том случае, если в первом такте цикла нарушений целостности выводов нет, устройство переходит к второму такту работы. Во втором такте с инверсного выхода блока 14 задания контрольнь>х кодов выдается обратный контрольный код.

Таким образом, те неисправности, которые не были выявлены в первом такте (например, короткое замыкание

i ãî выхода контролируемого вывода), будут обнаружены. В том случае, если отклонений от нормы в соответствующей паре контролируемых выводов нет, происходит автоматически переход к контролю очередной пары выводов. Этот переход осуществляется путем увеличения во втором такте цикла содержимого счетчика 10. Следовательно, при такой организации контроля прямым и обратным кодом пар выводов БИС обеспечивает выявление всех константных неисправностей выводов.

В исходном состоянии все элементы памяти находятся в нулевом состоянии. В блоке 15 выключатели находятся в положении "Включено . Код операции "Контроль" подается на вход 6 устройства.

Код операции поступает на вход дешифратора 34. Единичный сигнал с его выхода поступает íà S-вход триггера 31, который устанавливается в единичное состояние. Единичный сигнал с прямого выхода триггера 31 запускает генератор 30 и на era нервом выходе появляется тактовый импульс. Этот сигнал поступает на второй вход элемента И 36, на первый вход которого поступает единичный

3 l 2.641 сигнал с нулевого выхода триггера 17 блока l. Первый импульс с первого выхода генератора 30, пройдя через элемент И 36, поступает на счетный вход триггера 32 и переключает его в единичное состояние. С первого выхода блока 14 прямой контрольный код поступает через коммутатор 13 на первые информационные входы коммутаторов 12.! — 12.0 и второй инфор!

О мационный вход блока l .

Единичный сигнал, появившийся на нулевом выходе дешифратора 11 в результате поступления на его вход единичного сигнала, открывает коммутатор 12.1, и контрольный код с выхода ЬИС поступает на соответствующий вход блока 15. Контрольный код проходит через замкнутые тумблеры блока 15 и поступает на открытый тем же единичным сигналом с нулевого выхода дешифратора Jl блок элементов

И 4.1 и далее на первый информационный вход блока 1. Тактовый импульс с второго выхода генератора 30 через открытый элемент И 37 поступает на синхровход триггера 17. В том случае, если коды, поступившие на входы блока 1, совпадают, на его выходе единичный сигнал отсутствует, и триггер 17 остается в исходном состоянии.

В противном случае по заднему фронту этого синхроимпульса триггер 17 переключается в единичное состояние и на выходе коммутатора 16 появляется последовательность тактовых импульсов, сигнализирующая о неисправности выводов БИС.

Одновременно по .заднему фронту этого же тактового импульса переклю- 40 чается в единичное состояние триггер

33. В том случае, если неисправность не обнаружена, по заднему фронту синхроимпульса, поступившего с первого выхода генератора 30, триггер 45

32 переключается в исходное состояние. С второго выхода блока 14 на выход коммутатора 13 поступает инверсный контрольный код. Этот код одновременно поступает на второй ин- 50 формационный вход блока l . .С выхода коммутатора 12.1 через блок 15 инверсный контрольный код поступает на вход блока 4.1 элементов И и на первый информационный вход блока l. 55

Очередной тактовый импульс с второго выхода генератора 30 поступает на синхровходы триггеров 17 и 33. По

8! заднему фронту этого импульса происходит запись результата проверки целостности выводов в триггер 17, Триггер 33 возвращается в исходное состояние. При этом в счетчик 10 записана единица. На первом выходе дешифратора ll сформирован высокий потенциал. По заднему фронту очередного тактового импульса с первого выхода генератора 30 триггер 32 переключается в единичное состояние. На очередную пару выводов БИС подается прямой контрольный код. Цикл проверки повторяется. После проверки последней пары выводов БИС на и-м выходе счетчика 10 сформирован единичный сигнал, который поступает через элемент ИЛИ 35 íà R-вход триггера

3!. В результате этого .выдача тактовых импульсов с выхода генератора

30 прекращается.

На выход 9 устройства через коммутатор 16 поступает единичный сигнал, свидетельствующий о конце контроля и исправности выводов БИС.

Формула изобретения

1. Устройство для контроля БИС, содержащее дешифратор номеров выводов, две группы блоков элементов И, коммутатор контрольных кодов, блок задания контрольных кодов, счетчик, блок синхронизации, блок анализа резулътата, группу входных коммутаторов, причем выходы блока задания контрольных кодов соединены с информационными входами коммутатора контрольньгх кодов, прямой и инверсный управляющие входы которого соединены с первым выходом блока синхронизации, первые группы информационных входов входных коммутаторов группы соединены с выходами контролируемой БИС, входы которой соединены с выходами блоков элементов И первой группы, вход пуска устройства соединен с вхо-. дом пуска блока синхронизации, первые управляющие входы входных коммутаторов группы и управляющие входы . блоков элементов И первой группы соединены с вторым выходом блока синхронизации, выходы дешифратора номеров выводов соединены с вторыми управляющими входами входных коммутаторов группы, вход начальной установки устройства соединен .с входами сброса счетчика, блока анализа результа- .

1264181 та и первым входом сброса блока синхронизации, первая группа информационных входов которого соединена с выходами блоков элементов И второй группы, управляющие входы которых соединены с выходами дешифратора номеров выводов, третий и четвертый выходы блока синхронизации соединены соответственно со счетным входом счетчика и синхровходом дешиф- 10 ратора номеров выводов, о т л и ч а ю щ е е с я .тем, что, с целью повышения полноты контроля, оно содержит блок переключателей пар выводов, причем входы блока переключателей пар выводов подключены к выходам входных коммутаторов группы, à 1 и выход группы выходов — к информационным входам х-х блоков элементов И первой и второй групп, группа выходов комму- 20 татора контрольных кодов соединена с вторыми группами информационных входов, входных коммутаторов группы и блока аналиэа результата, вход конца контроля которого соединен с выходом переполнения счетчика, соединенным с вторым входом сброса блока синхронизации, группа выходов счетчика соединена с группой входов дешифратора номеров выводов, выход от- ЗО, сутствия ошибки блока анализа резуль тата соединен с входом разрешения выдачи синхроимпульсов блока синхронизации, пятый и шестой выходы которого соединены соответственно с синхровходом и входом разрешения выдачи сигнала ошибки блока анализа результата, выход результата которого является выходом устройства.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок анализа результата содержит группу элементов ИЛИ, схему сравнения, триггер ошибки и коммутатор ошибки, причем входы элементов ИЛИ группы являются первой группой информационных входов блока, первая и вторая группы информационных входов схемы сравнения сое3 динены соответственно с выходами элементов ИЛИ группы и второй группой информационных входов блока, выход схемы сравнения соединен с информационным входом триггера ошибки, синхровход и. вход сброса которого являются одноименными входами блока, единичный и нулевой выходы триггера ошибки соединены с информационными входами коммутатора ошибки, первый и второй управляющие входы которого являются соответственно входом конца контроля и входом разрешения выдачи сигнала ошибки блока, нулевой выход триггера ошибки и выход коммутатора ошибки являются соответственно вы ходом отсутс.твия ошибки и выходом результата блока.

1264181 б

Составитель И.Хазова

Техред В. Кадар

Корректор А.Зимокосов

Редактор И.Касарда

Заказ 5563/49 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4

22. 2

22.