Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств в вычислительных системах обработки массивов данных. Целью изобретения является повышение быстродействия устройства . Устройство содержит регистр, блоки преобразования адреса, адресные коммутаторы, коммутатор входных данных, регистр входных данных, коммутаторы выходных данных, регистр выходных данных и накопители. Устройство обеспечивает сортировку и вьщачу информации в соответствии с требованиями алгоритма двоично-инверсной выдачи данных, Повьшение быстродействия устройства осущест (Л вляется за счет того, что данные, считанные одновременно из N блоков памяти, расположены в двоично-инверсной последовательности. 3 ил.

СОКИ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ БЛИН (191 (И) (511 4 < 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 3896413/24-24 (22) 16.05.85 (46) 15 ° 10.86 ° Бюл, В 38

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (72 } Е .Л. Полин, В .А. Минченко, А.В.Дрозд, B.Â.Ëåáåäü и В.В,Шабадаш (53) 681 327.6(088.8) (56) Прангипвили И.В., Виленкин С.Я.

Медведев И.Л. Параллельные вычислительные системы с общим управлением. N.: Энергоиздат, 1983, с. 66, рис. 2.5.

Авторское свидетельство СССР

11 297070, кл. С 11 С 19/00, 1977. (54) ОПЕРАТИВНОЕ ЗАПОКИНАНЩЕЕ УСТРойетво (57) Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств в вычислительных системах обработки массивов данных. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистр, блоки преобразования адреса, адресные коммутаторы, коммутатор входных данных, регистр входных данных, коммутаторы выходных данных, регистр выходных данных и накопители. Устройство обеспечивает сортировку и выдачу информации s соответствии с требованиями алгоритма двоично-инверсной выдачи данных. Повышение быстродействия устройства осуществляется за счет того, что данные, считанные одновременно из11 блоков памяти, расположены в двоично-инверсной последовательности. 3 ил.

45

50 При поступлении четверки данных

0,, О,, О, О на инФормационные входы устройства происходит их запись в регистр 7, Если код старших разрядов адре55 са равен 00, то нулевой выход входного регистра подключается коммутатором б в первую четверть накопителя 10

12642

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств в вычислительных системах обработки массивов данных, Цель изобретения — повышение быстродействия устройства.

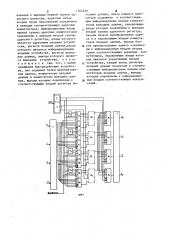

На фиг. 1 представлена структурная схема устройства для четырех блоков памяти; на фиг, 2 — структу- !О ра размещения информации после записи массива из 64 информационных слов на фиг, 3 — блок-схема блока . 1 преобразования данных.

Устройство содержит адресный ре- 15 гистр 1, разделенный на две части: старшую 2 и младшую 3, блоки 4 преобразования адреса, адресные коммутаторы 5, коммутатор 6 входных данных, регистр 7 входных данных, ком- 20 мутаторы 8 выходных данных, регистр

9 выходных данных и накопители 10.

Адресный регистр l предназначен для приема из внешнего управляющего устройства (процессора) адре- 25 сов считывания (з аписи) данных.

Регистр разделен на две части— старшую 2 и младшую 3. Старшая часть содержит f.=log n старших разрядов адреса, младшая — (llew-1) разрядов (М вЂ” полное число разрядов адреса обращения к памяти).

Блоки 4 обеспечивают преобразование 1 старших, разрядов адреса обращения для каждого из и накопите- 35 лей в соответствии со следующим алгоритмом. Из номера i-ro блока, закодированного 1-разрядным двоичным кодом, вычитается код 1 старших разрядов адреса, выраженных в дополни- 40 тельном коде, Блоки 4 могут быть реализованы в соответствии с фиг,. 3 и представляют собой сумматор, выходы которого являются выходами формирователя, первые входы соединены с уровнями

"0" и "1", образующими код номера

1-го блока, а вторые — с выходами инверторов, входы которых являются входами формирователя. На вход заема сумматора подается уровень "l".

Например, для четырех накопителей преобразователь имеет двухразрядный сумматор и два элемента НЕ. При появлении на выходе старшей части 2 адресного регистра 1 адресов 00, 01

10, 11 на выходе преобразователя 4 для нулевого блока памяти вырабатыва40

2 ются соответственно адреса 00, 11, 10, 01, для первого блока памяти—

01, 00, 11, 10, для второго блока памяти — 10, 01, 00, 11, для третьего блока памяти — ll 01, 01, 00.

Коммутаторы 6 предназначены для перераспределения входных данных, считываемых с регистра 7, перед записью их в блоки памяти.

Регистр 7 предназначен для приема четырех k-разрядных входных данных, Коммутаторы 8 обеспечивают перераспределение входных данных, считываемых из блоков памяти перед записью их в регистр 9, Регистр 9 предназначен для записи считанных из блоков памяти и

k-разрядных данных, Рассмотрим работу устройства для обеспечения алгоритма выдачи данных в двоично-инверсной последовательности. Под двоично †инверсн последовательностью выдачи данных понимается выдача данных с двоично-инверсными номерами, т.е. если при прямой последовательности номер 1 -ro выдаваемого данного определяется выражением М.=а 2 +а, 2 +...а .. 2 +а 2, то при двоично-инверсной последовао

1 1т -1 тельности и =а ? +а 2+ ...+а 2

+а -2 . Например, для массива из восьми данных прямая последовательность вывыдачи О,, О,, 0, 0, 0, 0

0 1 а двоично-инверсная — О, О,, т1

У вом случае четвертым по счету будет выдано данное 0 а во втором — О

Для этого случая устройство работает следующим образом, При записи массива информации в блоки памяти на вход устройства УПР подается "0", задающий режим работы "Запись в ЗУ". Адресные коммута торы 5 подключают к входу старших разрядов блоков памяти 10 адрес, преобразованный соответствующими блоками 4. з 12

Первый выход регистра 7 подключа- ется коммутатором 6 к входу накопителя 10, и данное D, записывается .1 Ф во вторую четверть накопителя 10„ .

Второй выход входного регистра подключается к входу накопителя 10 данное 0 записывается в третью четверть накопителя 10 . Третий выход входного регистра подключается к входу накопителя 10з, данное О записывается в четвертую четверть на— копителя 10з. Последующие четверки данных записываются аналогично до заполнения четверти накопителей, Далее код пары старших адресов принимает значение 01. При этом данные с нулевого выхода входного регистра записываются в первую четверть накопителя 10„, с первого выхода— во вторую четверть накопителя 10 с второго выхода — в третью четверть накопителя 10, с третьего выхода — в четвертую четверть накопителя 10, После заполнения второй четверти накопителя код пары стар- 2 ших адресов принимает значение 10.

При этом данные с нулевого выхода входного регистра записываются в первую четверть накопителя 10, с первого выхода — во вторую четверть накопителя 10з, с второго выхода— в третью четверть накопителя 10 с третьего выхода — в четвертую четверть накопителя 10, . После заполнения трех четвертей накопителей

35 код пары старших адресов принимает значение 11. При этом данные с нулевого выхода входного регистра 7 записываются в первую четверть накопителя 10, а с первого выхода 0 во вторую четверть накопителя 10, .с второго выхода — в третью четверть накопителя 10 с третьего выхода— в четвертую четверть накопителя 10 .

Пример размещения информации по- сле записи всего массива данных в память для массива из 64 данных (D,— O ) показан на фиг. 2.

При считывании массива информации из блоков памяти в процессор, gp выполняющий операцию БПФ, на входе устройства управления оперативной памятью УПР имеется "1". Коммутаторы адреса 5,, 5, 5, 5 подключают к

1в старшим разрядам адресных входов на- у копителей 10 -10 пару старших разрядов старшей части 2 адресного регистра 1, Старшие и младшие адреса

64240 4 выдаются на вход устройства в двоично-инверсном порядке. В соответствии с этим код пары старших адресов принимает вначале значение 00, и происходит считывание четверок дан ных из первых четвертей всех блоков памяти в двоично-инверсном порядке.

Для массива из 64 данных считываются четверки (О, Г,, О, D ), (О, О

0м, О „, . После считывания первой четверки массива данных в соответствии с двоичной инверсией код пары старших адресов принимает значение

10„ Далее происходит считывание четверок данных в двоично-инверсном порядке с третьих четвертей накопителей 10, -10 . Выход накопителя 10, подключается коммутатором 8 к вто0 рому входу регистра 9, выход накопителя 10 — к третьему входу регист1 ра 9> выход накопителя 10 — к нулевому входу регистра 9, выход накопителя 10 — к первому входу выходно5 ro регистра 9, После считывания половины данных код пары старших адресов принимает значение 01 и происходит считывание четверки данных в двоично-ипверсном порядке с вторых четвертей накопителей 10, — 10з ° Выход накопителя 10, подключается к третьему входу регистра 9, выход накопителя

10„ — к нулевому входу, выход накопителя 10 — к первому входу, выход накопителя 10 — к второму входу

3 регистра 9.

Считывание массива данных завершается считыванием в двоично-инверсном порядке данных из четвертой четверки накопителей 10,-10 . При з этом выход накопителя 10 подключается к первому входу, выход накопителя 10„ — к второму входу, выход накопителя 10 — к третьему входу, выход накопителя 10 — к нулевому з входу регистра 9.

Таким образом, устройство управления оперативной памятью обеспечивает сортировку и выдачу информации в соответствии с требованиями алгоритма двоично-инверсной выдачи данных.

Формула и з о б р е т ения

Оперативное запоминающее устройство, содержащее накопители, адресные входы первых групп которых подФ 1 ключены к выходам первой группы адресного регистра, адресные входы вторых групп накопителей подключены к выходам соответствующих адресных коммутаторов, информационные входы первой группы адресных коммутаторов подключены к выходам второй группы адресного регистра, входы которого являются адресными входами устройства, регистр входных данных, входы которого являются информационными входами устройства, регистр выходных данных, выходы которого являются выходами устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит блоки преобразования адреса, коммутаторы входных данных и коммутаторы выходных данных, выходы которых подключены к соответствующим входам регистра вы264240 4 ходных данных, выход каждого накопителя подкл1очен к соответствующим информационным входам коммутаторов выходных данных, управляющие входы которых подключены к выходам второй группы адресного регистра, входам блоков преобразования адреса и к управляющим входам коммутаторов входных данных, выходы бло!

О ков преобразования адреса подключены к информационным входам вторых групп соответствующих адресных коммутаторов, управляющие входы которых являются управляющим входом

1 устройства, каждый выход регистра входных данных подключен к соответствующим информационным входам коммутаторов входных данных, выходы которых подключены к информационным входам соответствующих накопителей.

Фие 2

Составитель С. 111устенко

Редактор M.Öèòêèíà Техред И.Попович Корректор Е. Сирохман

Заказ 5568/52 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

6лон юиятиР!

26424П блан bna &юи ломята1 памятия лцмяти 5