Сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении БИС на дополняющих МДП-транзисторах. Целью изобретения является повышение быстродействия , Цель достигается изменением связей между входными ВДЦ-транзисторами и информационными входами и входом переноса сумматора, а также введением связи МДП-транзисторов, подключенных к выходу переноса сумматора с его первым информационным входом. Это дает возможность исключить последовательное соединение двунаправленных ключей при построении многоразрядных сумматоров на основе данного, а также обеспечивает усиление сигнала переноса между разрядами. 1 ил., 1 табл. (Л С

СОЮЗ СОНЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„БО„„1270756 А 1 (gg 4 G 06 F 7/50

ГОСУДАРСТБЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ е

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ полняющих КЦП-транзисторах. Целью изобретения является повышение быстродействия. Цель достигается изменением связей между входными МДП-транзнстораии и информационными входами и входом переноса сумматора, а также введением связи ИДП-транзисторов, подключенных к выходу переноса сумматора с его первым информационным входом. Это дает возможность исключить последовательное соединение двунаправленных ключей при построении многоразрядных сумматоров на основе данного, а также обеспечивает усиление сигнала переноса между разрядами. t ил., 1 табл. (21) 3743816/24-24 (22) 25.05.84 (46) 15. 11.86. Бюл. У 42 (71) Московский ордена Трудового

Красного Знамени инженерно-физический институт (72) 10. Г. Дьяченко и В.А. Коваленко (53) 681.325 ° 5(088.8) (56) Заявка Японии Р 55-1619, кл, G 06 Г 7/50, 1980.

Авторское свидетельство СССР

9 1100620, кл. G 06 F 7/50, 1983 ° (54) СУММАТОР (57) Изобретение относится к вычислительной технике и может быть использовано при построении БИС на доОПИСАНИЕ ИЗОБРЕТЕНИЯ

1270756

Изобретение относится к вычислительной технике и может. быть исполь зовано при построении интегральных схем обработки цифровой информации на дополняющих МДП-транзисторах.

Целью изобретения является повышение быстродействия сумматора.

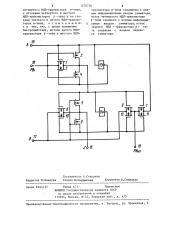

На чертеже представлена принципиальная электрическая схема сумматора.

Сумматор содержит МДП-транзисторы 1- 12, из которых транзисторы 1, I °

Выходь Транзисторы

Входы

А /2 (Р „Б 1 Р „1 2 3 /4 9 /6 Г7 f8 9 (10 11(12

0 0 O 0 0 II rl II 3 II II 11 3 3. II 11 3

0 0 1 1 0 П 3 П П П 3 3 П 3 3 3 П

0 П П П 3 3 П П 3 П П П 3

0 1 0 1

0 1 1 0 1 П 3 II П 3 3 3 П П 3 3 П

0 3 П 3 3 П 3 3 П 3 3 3 П

1 0 0 1

1 0 1 0 1 3 3 3 П П П П 3 3 П П 3

1 1 0 0 1 3 П 3 3 3 3 3 П П 3 3 П

1 1 1 1 1 3 3 3 П 3 П П 3 П П П 3

При этом за счет элементов НЕ 13 .и 14 осуществляется усиление сигна1 ла переноса, подаваемого на вход

16 что дает воэможность эффективно использовать данный сумматор в много разрядных сумматорах.

Формула изобретения

Сумматор, содержащий шесть МДПтранзисторов п-типа, шесть ИДП-транзисторов Р -типа и два элемента НЕ, причем затвор первого МДП-транзистора р -типа соединен с истоком второго МДП-транзистора p -- типа,,с первым информационным входом сумматора и с входом первого элемента НЕ, выход которого соединен с затвором первого и с истоком второго МДП-транзисторов п-типа, вход второго элемента НЕ соединен со стоками первого и второго МДП-транзисторов p -типа, со стоками первого и второго

ИДП-транзисторов п-типа, с истоком

2, 5, 6., 7 и 12 являются транзисторами -типа„ а остальные п-типа, элементы НЕ 13 и 14, первый информационный вход 15, вход переноса 16, 5 второй информационный вход 17, выход 18 суммы и выход 19 переноса.

Работа сумматора иллюстрируется с помощью таблицы истинности сумматора, дополненной таблицей состояний транзисторов. Символы П и 3 соответствуют проводящему и закрытому состоянию транзисторов. третьего МДП-транзистора р -типа с затворами четвертого и пятого

ИДП-транзисторов р --типа и с затвором четвертогс МДП-транзистора р-òèïà, выход второго элемента НЕ соединен с истоком четвертого МДП40 транзистора п-типа, с затворами пятого и шестого МДП-транзисторов и-типа и с затвором шестого

МДП-транзистора р -типа, выход

45 переноса сумматора соединен со стока- ми пятого и шестого МДП-транзисторов р -типа и со стоками третьего и шестого ИДП-транзисторов п-типа, выход суммы сумматора соединен со стоками третьего и четвертого ИДП50 транзисторов Р -типа и со стоками четвертого и пятого ИДП-транзисторов п-типа, затвор второго МДП-транзистора р --типа соединен с затвором второго МДП-транзистора п-типа, с истоками первого МДП-транзистора

Р -типа и первого МДП-транзистора п-типа, затвор третьего МДП-транзис тора р -типа соединен с затвором

1270756

Рй х

Составитель А .Степанов

Редактор М.Бандура Техред Л.Сердюкова Корректор В.Синицкая

Заказ 6244/51

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 четвертого МДП-транзистора п-типа, с истоками четвертого и шестого

МДП-транзисторов р --типа и со стоками третьего и пятого МДП-транзисторов п-типа, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, истоки пятого МДПтранзистора Р -типа и шестого МДПтранзистора п-типа соединены с первым информационным входом сумматора, исток четвертого МДП-транзистора р -òèïà соединен с вторым информаци5 онным входом сумматора, исток первого ЩД вЂ” транзистора.P — ти.та соединен с входом переноса сумматора.