Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих арифметических устройств, работакицих, например, в позиционно-остаточной системе счисления . Цель изобретения - повышение быстродействия. Устройство содержит регистр множителя, регистр множимого , группу умиожителей, коммутатор и накапливакяций сумматор и соответствующие связи. 1 з.п. ф-лы, 1 ил.

СООЗ СОВЕТСКИХ

СОЦИАЛИСТЬИЕСКИХ

РЕСПУБЛИК (51)4 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, 4 .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 4 с:,, (21) 3833620/24-24 (22) 30.12.84 (46) 07.12.86. Бюп. 11 45 (71) Московский институт инженеров гражданской авиации (72) В.Г,Евстигнеев, О.В.Евстигнеева и А.П.Титов (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

У 754412, кл. G 06 F 7/52, 1970.

Авторское свидетельство СССР

В 383044, кл. С 06 F 7/52, 1970.

„;SU„„1275432 A i (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих арифметических устройств, работающих, например, в позиционно-остаточной системе счисления. Цель изобретения — повышение быстродействия. Устройство содержит регистр множителя, регистр множимого, группу умножителей, коммутатор и накапливающий сумматор и соответствующие связи. l з.п. ф-лы, 1 ил.

75432 3

1 12

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств работающих, например, в поэиционноостаточной системе счисления (ПОС).

Цель изобретения — повышение быстродействия.

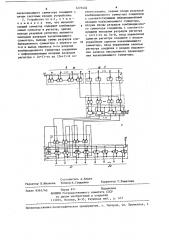

На чертеже представлена схема устройства для умножения. 1

Устройство содержит регистр 1 множителя, регистр 2 множимого, умножители 3, коммутатор 4, накапливающий сумматор 5. Регистр 1 содержит разряды 6. Регистр 2 содержит разряды 7. Накапливающий сумматор 5 содержит комбинационный сумматор 8 и регистр 9. Сумматор 8 имеет разряды 10. Регистр 9 имеет разряды

11. Устройство имеет тактовые входы 20

12-16, а также вход 17 обнуления, входы 18 и 19 множимого и множителя, выходы 20 и 21 результата.

° Работа устройства начинается по управляющему сигналу, подаваемому 2 по входу 17 и сбрасывающему регистр

9 в нуль. Затем операнды А и В по входам 19 заносятся в регистры 2 и 1.

На входы умножителей 3 подаются разряды множимого А и один (младший) разряд множителя В. Каждый умножитель 3 формирует произведение в виде двух цифр: старшего разряда и младшего разряда. Поскольку сначала фор мируются младшие разряды произведения, то они управляющим сигналом по . входу 13 передаются через коммутатор

4 на входы соответствующих разрядов сумматора 8, на вторых входах которых пока нули. Образовавшаяся в сум- 10 маторе 8 частичная сумма управляющим сигналом, подаваемьщ по входу 16, заносится в старшие разряды сдвигового регистра 9. После этого управляющий сигнал с входа 13 снимается и по- 4 дается по входу 15, который сдвигает содержимое 8 регистра на один разряд вправо.

К этому моменту времени на умножителях 3 сформируются старшие разряды произведения, которые управляющим сигналом по входу 14 передаются через коммутатор 4.на входы соответствующих разрядов 10 сумматора 8, на другие Входы которых поступает содержимое старших разрядов регистра 9.

Образовавшаяся сумма управляющим сигналом по входу 16 записывается в старшие, разряды регистра 9. Затем управляющим сигналом по входу 12 содержимое регистра 1 сдвигается. вправо на, один разряд. На этом заканчивается цикл умножения множимого на один

S-ичный разряд множителя.

Изложенный процесс повторяется m раэ до умножения множимого на все разряды множителя. В результате на регистре 9 образуется произведение, имеющее в общем случае двойную разрядность.

Формула и э обретения

1. Устройство для умножения, содержащее регистры множимого и множиn+1 теля, накапливающий сумматор, (†-)

2 умножителей (n — разрядность множимого) и коммутатор, причем выходы накапливающего сумматора являются выходами реэультата устройства, вход управления сдвигом регистра множителя соединен с первым тактовым входом устройства, вход управления сдвигом накапливающего сумматора соединен с вторым тактовым входом устройства, выход первого разряда регистра множителя соединен с первыми входами умнои+l жителей с первого по (†-)-й, о т— л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в неи+1 го введены n — — — умножителей

Э причем первые входы умножителей с

n+1 (+ 1)-го по и-й соединены с выхо2 дом первого разряда регистра множителя, выходы разрядов регистра множимого соединены с вторыми входами соответствующих умножителей, выходы младших разрядов умножителей соединены с информационными входами первой группы коммутатора, информационные входы второй группы которого соедииены с выходами старших разрядов умножителей, управляющие входы коммутатора соединены соответственно с третьим и четвертым тактовыми входами устройства, выходы. второго коммутатора соединены с входами накапливающего сумматора, вход управления записью накопленного произведения

1275432

Составитель А. Клюев

Редактор В.Иванова Техред Н.Глущенко

Корректор Г.Решетник

Заказ 6561/40 тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 накапливающего сумматора соединен с пятым тактовым входом устройства.

2. Устройство по п.1, о т л и— ч а ю щ е е с. я тем, что накапливающий сумматор содержит комбинационный сумматор и регистр, причем выходы разрядов регистра являются выходами разрядов накапливающего сумматора, выходы суммы разрядов комбинационного сумматора с первого по 10 и-й и выход переноса n-ro разряда комбинационного сумматора соединены с информационными входами разрядов регистра с (n+1)-го по (2п+1)-й соответственно, первые входы разрядов комбинационного сумматора соединены с соответствующими информационными входами накапливающего сумматора, вторые входы разрядов комбинационного сумматора соединены с соответствующими выходами разрядов регистра с (и+1)-го по 2п-й, вход управления сдвигом регистра соединен с входом управления сдвигом накапливающего сумматора, вход управления записью регистра соединен с входом управления записью накопленного произведения накапливающего сумматора.