Формирователь выходного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к электронной коммутационной и вычислительной технике. Может использоваться в буфернык устройствах ввода-вывода интегральных схем. Цель изобретениярасширение функциональных возможностей - достигается за счет введения в формирователь выходного сигнала второго элемента И-НЕ 5 и устройства сравнения 6, состоящего из элемента 1-ШИ-И/НЕ 7 и двух инверторов 8 и 9. Формирователь, кроме того, содержит магистральный элемент 1, элемент ИЛИ-НЕ 2, первый элемент И-НЕ 3, инвертор 4, входы - информационньп1 10, стробирующий 11, выходную шину 12, контрольную шину 13, шину питания 14 и общую шину 15. Введение устройства 6 сравнения позволяет отслеживать завершенность процесса передачи информации через формирователь при различных нагрузках на выходе формирователя и использовать сигнал контрольной шины 13 для улучшения временных характеристик обмена информацией между различными блоками информационно-вычислительной системы. 1 ил. i (Л IC со сх 4ib //

СОЮЗ СОЕЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (gII y H 03 К 19/094

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3922905/74-21 .(22) 05.07,85 (46) 15.12.86. Бюл, № 46 .(72) В,Л. Дшхунян, Е.А, Комаров.

А.И. Моторин, В,В. Теленков и Ю.II. Фомин (53) 621.382(088.8) (56) Патент ФРГ ¹ 2843791, кл. Н 03 К 19/08, 06,10.78.

Европейский патент ЕР № 0102670, кл, Н 03 К 19/094, 26.08.83. (54) ФОРМИРОВАТЕЛЬ ВЫХОДНОГО СИГНАЛА (57) Изобретение относится к электронной коммутационной и вычислительной технике. Может использоваться в буферных устройствах ввода-вывода интегральных схем. Цель изобретениярасширение функциональных возможностей — достигается за счет введения

„„SU„„1277384 A 1 в формирователь выходного сигнала второго элемента И-НЕ 5 и устройства сравнения 6, состоящего из элемента

ИЛИ-И/НЕ 7 и двух инверторов 8 и 9.

Формирователь, кроме того, содержит магистральный элемент 1, элемент

ИЛИ-НЕ 2, первый элемент И-HE 3, инвертор 4, входы — информационный 10, стробирующий 11, выходную шину 12, контрольную шину 13, шину питания 14 и общую шину 15. Введение устройства

6 сравнения позволяет отслеживать завершенность процесса передачи информации через формирователь при различных нагрузках на в:rxope формирователя и использовать сигнал контрольной шины 13 для улучшения временных характеристик обмена информацией между различными блоками информационно-вычислительной системы. 1 ил.

1277384

Изобретение относится к электронной коммутационной и вычислительной технике и может быть использовано в буферных устройствах ввода-вывода интегральных схем. 5

Цель изобретения — расширение функциональных возможностей путем введения устройства сравнения, выполненного на логических элементах

ИЛИ-И/НЕ, сравнения входного и выход- 10 ного сигналов и вьдачи контрольного сигнала совпадения на окончание операции.

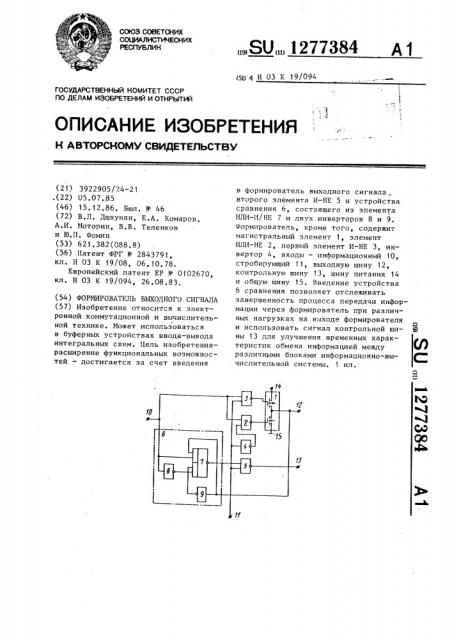

На чертеже показана принципиальная схема устройства. !5

Устройство содержит магистральный элемент 1, элемент ИЛИ-НЕ 2, первый элемент И-НЕ 3, первый инвертор 4, второй элемент И-НЕ 5, устройство 6 сравнения, состоящее из элемента 20

ИЛИ-И/НЕ 7, второго 8 и третьего 9 инверторов.

Информационный вход 10 соединен с первыми входами первого элемента

И-НЕ 3 и элемента ИЛИ-НЕ 2, а также с входом второго инвертора 8 и с первым входом элемента ИЛИ-И/НЕ 7, Стробирующий вход 11 формирователя подключен к вторым входам первого 3 и второго 5 элементов И-НЕ и через пер30 вый инвертор 4 к второму входу элемента ИЛИ-НЕ 2. Выходная шина 12-формирователя подключена к второму входу элемента ИЛИ-И/НЕ 7 и через третий инвертор к третьему входу того же эле-З5 мента ИЛИ-И/НЕ, Четвертый вход элемента ИЛИ-И/НЕ соединен с выходом второго инвертора 8, а выход — с первым входом второго элемента И-НЕ 5, выход которого подключен к контроль- 40 ной шине 13 формирователя.

Магистральный элемент 1 состоит из последовательно соединенных дополняющих МДП-транзисторов и включен между шиной 14 питания и общей шиной 15. 4>

Стоки МДП-транзисторов соединены с выходной шиной 12 формирователя, а затворы р — и n — - канальных МДП-транзисторов соответственно с выходами первого элемента И-НЕ 3 и элемента И

ИЛИ-НЕ 2.

Формирователь выходного сигнала работает следующим образом.

На информационный вход 10 поступает информация (логический "0" или ло- Я гическая "1"). В некоторый, момент вревремени от управляющего устройства на стробирующий вход 11 формирователя поступает сигнал, разрешающий выдачу информации на выходную шину 12. При этом либо на выходе элемента И-НЕ 3 формируется логический "0" и соответственно открывается МДП-транзистор магистрального элемента 1 р-типа проводимости, либо на выходе.элемента HJIH-HE 2 формируется логическая

II

1 и соответственно открывается

1ЯП-транзистор и-типа проводимости.

Соответственно на выходной шине 12 формируется уровень логической "1" или уровень логического "0". В зависимости от емкостной нагрузки на выходной шине 12 время вьдачи информации изменяется и соответствующее устройство, включающее указанный формирователь выходного сигнала, должно отслеживать момент окончания вьдачи информации. Формируемый на выходной шине 12 логический уровень поступает на соответствующий вход элемента

ИЛИ-И/НЕ 7 и третий инвертор 9. На выходе элемента ИЛИ-И/НЕ 7 после совпадения передаваемой информации с информационного входа 10 и информации, сформированной на выходной шине 12, появляется сигнал логической 1, который при наличии стробирующего сигнала обеспечивает на выходе второго элемента И-НЕ 5 и, следовательно, на контрольной шине

13 устройства формирование сигнала логического "0 .

Появление укаэанного сигнала свидетельствует об окончании операции выдачи информации для устройства, управляющего стробирующим сигналом по стробирующему входу 11, и, таким образом, разрешает переход на следующий этап обработки информации.

При несовпадении сигналов на информационном входе 10 устройства и выходной шине 12, устройство сравнения выдает сигнал логического "0"I, который при наличии стробирующего сигнала вьдает на контрольной шине

13 сигнал логической "1, что свидетельствует о незавершенности переходного процесса на выходной шине 12.

Таким образом, наличие устройства сравнения позволяет отслеживать завершенность процесса передачи информации через формирователь при различных нагрузках на выходной шине устройства и использовать сформированный сигнал контрольной шины формирователя для улучшения временных харак1277384

Составитель В. Лементуев

Техред И.Попович Корректор M-шароши

Редактор М, Петрова

Заказ 6759/56- Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 теристик обмена информацией между различными блоками информационно-вычислительных систем, Формула изобретения

Формирователь выходного сигнала, содержащий элемент ИЛИ-НЕ, первый элемент И-НЕ, первый инвертор и Магистральный элемент, состоящий из двух последовательно соединенных

МДП-транзисторов р — и п-типа, затворы которых подключены к выходам соответственно первого элемента И-HE и элемента ИЛИ-НЕ, а стоки которых подключены к выходной шине устройства, первые входы элемента ИЛИ-НЕ и первого элемента И-HE соединены и подключены к информационному входу формирователя, второй вход первого элемента И-НЕ и вход первого инвертора подключены к стробирующему входу формирователя, выход первого инвертора соединен с вторым входом элемента ИЛИ-НЕ, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей устройства, в него введен второй элемент И-НЕ и устройство сравнения, содержащее элемент ИЛИ-И/HE и второй и третий инверторы, первый и второй входы элемента ИЛИ-И/НЕ, являющиеся

10 первой парой входов этого элемента, соединены с информационным входом и выходной шиной устройства, которые в свою очередь через второй и третий инверторы соответственно подключены

>5 к третьему и четвертому входам элемента ИЛИ-И/НЕ, являющимися второй ларой входов этого элемента, выход элемента ИЛИ-И/НЕ и стробирующий вход устройства подключены к входам 0 второго элемента И-НЕ, выход которого соединен с контрольной шиной формирователя.