Усилитель считывания

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при создании полупроводниковых схем памяти. Отличие предлагаемого технического решения от известных состоит в том, что, с целью упрощения схемы и повышения быстродействия , усилитель считывания построен по однокаскадной схеме, причем транзисторы дифференциального каскада выполняют одновременно функцию задатчика опорного напряжения для источников .тока в трансляторе уровней сигналов. 1 ил. (Л с tc 00 о сд

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИН а11 4 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3911361/24-24 (22) 12.06.85 (46) 30.12.86. Бюл. И 48 (72) А.С.Попель, М.П.Сахаров, И.В.Черняк и N.Î.Áîòâèíèê (53) 68 1.327.6 (088.8) (56) ИС ОЗУ К155РУ7, И63 †4, 046-0533.

ИС ОЗУ К155РУ7, ПГФ 348.701.133. (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ (57) Изобретение относится к области вычислительной техники и может быть,.SU„„1280450 А 1 использовано при создании полупроводниковых схем памяти. Отличие предлагаемого технического решения от известных состоит в том, что, с целью упрощения схемы и повышения быстродействия, усилитель считывания построен по однокаскадной схеме, причем транзисторы дифференциального каскада выполняют одновременно функцию задатчика опорного напряжения для источников, тока в трансляторе уровней сигналов ° 1 ил.

1280450

Изобретение относится к вычислительной технике и может быть использовано при создании полупроводниковых схем памяти.

Цель изобретения — упрощение 5 схемы и повышение быстродействия.

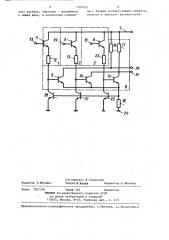

На чертеже представлена принципиальная схема предлагаемого усилителя считывания, Усилитель считывания содержит эмиттерные повторители 1, 2 и 3 на транзисторах 4, 5 и 6, шину питания

7, дифференциальный каскад 8 на тран. зисторах 9, 10 и 11, резисторы 12 и 13 первого и второго эмиттерных повторителей, выходы 14 и 15 усилителя считывания, резисторы 16, 17 и 18 дифференциального каскада, вход 19 запрета считывания, генераторы тока 20, 21 и 22, резистор 23 третьего эмиттерного повторителя, общую шину 24.

Усилитель считывания работает следующим образом.

Сигналы, поступающие на информационные входы 23 и 24 и вход 19 запрета считывания, транслируются на базы транзисторов 9, 10 и 11 через повторители на транзисторах 4, 5 и

6 и резисторы 12, 13 и 23 при протекании по ним тока генераторов тока 20, 21 и 22. Опорное напряжение на базы транзисторов поступает с резистора 18.

Транзисторы 9-11 и резисторы

16-18 образуют дифференциальный каскад, причем сигнал на выходы 14 и

15 снимается с резисторов 16 и 17 соответственно.

При поступлении на вход 19 запрета считывания высокого уровня, превышающего уровень на информационных входах 23 и 24, транзистор 11 открывается, а транзисторы 9 и 10 закры. ваются и на выход 14 поступает высокий уровень, а на выход 15 — низкий независимо от состояния информа ционных входов 23 и 24.

При поступлении на вход 19 запре- 5р та считывания низкого уровня транзистор 11 закрывается, и состояние выходов определяется транзисторами 9 и

10 в зависимости от состояния информационных входов. При поступлении на 5 информационный вход 23 высокого уровня, а на информационный вход 24 низкого уровня открывается транзистор 9 и закрывается транзистор 10, на вы- . ход 14 поступает низкий уровень, а на выход 15 — высокий. При поступлении противоположной информации меняется состояние транзисторов 9 и 10 и выходов 14 и 15.

Таким образом, транзисторы дифференциального каскада выполняют одновременно функцию задатчика опорного напряжения для источников тока в трансляторе уровней сигналов, что позволяет. построить усилитель по однокаскадной схеме и, следовательно, упростить и повысить быстродействие.

Формула изобретения

Усилитель считывания, содержащий три эмиттерных повторителя на транзисторах, коллекторы транзисторов первого и второго эмиттерных повторителей соединены с шиной питания,дифференциальный каскад на транзисторах, базы первого и второго транзисторов дифференциального каскада соединены соответственно со вторыми выводами резисторов первого и второго емиттерных повторителей, а коллекторы являются первым и вторым выходами усилителя считывания и через соответствующие резисторы подключены к шине питания, эмиттеры первого, второго и третьего транзисторов дифференциального каскада объединены и через резистор подключены к общей шине, база транзисторатретьего эмиттерного повторителя является входом запрета считывания, и три генератора тока на транзисторах, о т л ив ч а ю шийся тем, что, с цепью упрощения усилителя считывания и повышения его быстродействия, базы транзисторов первого и второго эмит терных повторителей являются соответственно первым и вторым информационными входами усилителя считывания, коллектор третьего эмиттерного повторителя подключен к шине питания, второй вывод резистора третьего эмиттерного повторителя соединен с базой третьего транзистора дифференциального каскада, коллектор и эмиттер которого соединены соответственно с коллекторЬм и эмиттером транзистора второго дифференциального каскада, базы транзисторов первого, второго и третьего генераторов тока подключены к эмиттеру второго транзистора дифференциаль1280450

Составитель В.Гордонова

Техред В. Кадар Корректор А.Обручар

Редактор Т.Митейко

7057/46 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., p. 4/5

Заказ

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 ного каскада, эмиттеры — подключены к общей шине, а коллекторы соединены.с базами соответственно первого, второго и третьего транзисторов.