Устройство для считывания информации из блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Цель изобретения - повьшение быстродействия устройства. Устройство считывания информации содержит первую и вторую пары входных разрядных шин, первую и вторую вьпходные разрядные шины, первый и второй адресные входы, шину питания, первый и второй адресные транзисторы первого типа проводимости, первую и вторую пары переключающих транзисторов первого типа проводимости с соответствующими связями и дополнительно содержит первый и второй переключающие транзистторы второго типа проводимости , первый и второй установочные транзисторы второго типа проводимости , первый и второй развязывающие транзисторы второго типа проводимости , тактовую и общую шины с соответствующими связями. 2 ил. (Л ю 00 о 1 СП N9

СС1ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1..SU „„1280452 (5D 4 С 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3947204/24 (22) 26.08.85 (46) 30.12.86. Бюл. В 48 (72) В.В.Баранов, Ю.М.Герасимов, Н.Г.Григорьев, А.Н.Кармазинский, П.Б.Поплевин и Э.П.Савостьянов (53) 681.Э27.6(088.8) (56) Патент США 11 4379344, кл. 365-203, опублик ° 1984.

Патент США и 4386419, кл. 365-203, опублик. 1985. (54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ ИЗ БЛОКОВ ПАМЯТИ (57) Изобретение относится к вычис"

I лительной технике. Цель изобретения— повышение быстродействия устройства.

Устройство считывания информации содержит первую и вторую пары входных разрядных шин, первую и вторую выходные разрядные шины, первый и второй адресные входы, шину питания, первый и второй адресные транзисторы первого типа проводимости, первую и вторую пары переключающих транзисторов первого типа проводимости с соответствующими связями и дополнительно содержит первый и второй переключающие транзис торы второго типа проводимости, первый и второй установочные транзисторы второго типа проводимости, первый и второй раэвязы- вающие транзисторы второго типа проводимости, тактовую и общую шины с соответствующими связями. 2 ил.

1280452

Изобретение относится к вычислительной технике и может быть испольэованО в запоминающих устройствах на КМДП транзисторах для считы-. вания информации.

Цель изобретения — повышение быстродействия устройства.

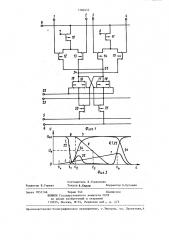

На фиг.1 дана схема устройства считывания информации; на фиг.2 временная диаграмма работы устройства.

Устройство содержит гервую пару входных разрядных шин 1-2, вторую пару входных разрядных шин 3-4, первую 5 и вторую 6 выходные разрядные шины, первый 7 и второй 8 адресные входы, шину питания 9, первый 10 и второй 11 адресные транзисторы первого типа проводимости, первую 1213 и вторую 14-15 пары переключающих транзисторов первого типа проводимости, а также первый 16 и второй 17 переключающие транзисторы второго типа проводимости, первый 18 и второй 19 установочные транзисторы второго типа проводимости, первый

20 и второй 21 раэвязывающие транзисторы второго типа проводимости, тактовую шину 22 и общую шину 23, внутренние узлы 24 и 25, причем истоки адресных транзисторов 10 и 11 соединены с шиной питания 9, затворы — с первым 7 и вторым 8 адресными входами соответственно, стоки — с истоками переключающих транзисторов первой 12-13 и второй 14-15 пар соответственно, затворы которых соединены с соответствующими парами 1-2 и 3-4 входных разрядных шин, а стоки переключающлх транзисторов первой пары 12-13 объединены с стоками соответствующих транзисторов второй пары 14-15, первый 16 и второй 17 переключающие транзисторы второго типа проводимости соединены по схеме с перекрестной обратной связью, сток первого переключающего транзи стара второго типа проводимости 16 соединен с затворами вторых переключающего 17 и развязывающего 21 транзисторов второго типа проводимости и с стоками первого установочного транзистора 18 и соответствующих переключающих транзисторов первого типа проводимости 13 и 15, сток второго переключающего транзистора второго типа проводимости 17 соединен с затворами первых переключающе10

2S

40 го 16 и развязывающего 20 транзисто- ров второго типа проводимости и с

l стоками второго установочного транзистора 19 и соответствующих переключающих транзисторов первого типа проводимости 12 и 14, истоки переключающих транзисторов второго типа проводимости 16 и 17, установочных

18- 19 и развязывающих 20-21 транзисторов соединены с общей шиной 23, стоки первого 20 и второго 21 развязывающего транзисторов соединены с первой 5 и второй 6 выходными разрядными шинами соответственно.

Устройство считывания информации работает следующим образом.

В статическом режиме на тактовом

22 и адресных 7 и 8 входах и выходных разрядных шинах 5 и 6 поддерживается напряжение "1, а на входных разрядных шинах 1-4 — напряжение

"0". При этом транзисторы 10-17, 20 и 21 закрыты, а 18 и 19 открыты, благодаря чему обеспечивается нали чие нулевых напряжений в узлах 24-25 и отсутствие потребления мощности в статическом режиме. Активный режим работы устройства поясняется с помощью временной диаграммы. В начальный момейт времени начинается изменение напряжений на входных разрядных шинах 1-2, соответствующие считываемой информации. Пусть для определенности напряжение на шине

2 остается равным нулю, а на шине

1 увеличивается по линейному закону (это имеет место в типовых БИС ОЗУ статического типа)

V,„ „ = =V, (t — t,) (1) где V — скорос-.ü изменения напряжения на входной разрядной шине; — время.

В момент времени t,,когда разность напряжений на входных разрядных шинах 1 и 2 станет достаточной

V,,чтобы компенсировать разброс параметров симметричных транзисторов 12-13, 14-15, 16-17, 18-19 и

20-21 и разброс емкостей в узлах

24-25, на адресный вход 7 подается напряжение 0", разрешающее передачу информации с первой пары входных разрядных шин 1-2 на выходные разрядные шины 5-6. При этом в устройстве начинается регенеративный процесс: совокупность транзисторов 10, 12-13 и 16-17 образует усилительную

1280452 (2) схему с положительной обратной связью. В результате регенеративного процесса в узлах 24-25 формируются напряжения "1" и "0" соответственно. В момент t 2, когда напряже- 5 ние в узле 24 достигнет порогового напряжения Ч„„р транзистора 21, начинается уменьшение напряжения выходной разрядной шины 6 за счет перезаряда емкости С „,„ этой шины током транзистора 21.. Время считывания определяется интервалом времени от t до момента t, когда напряжение выходной разрядной шины 6 достигнет заданного уровня V

В режиме восстановления напряжения на шинах 1, 6 и входах 7 и 22 восстанавливают до уровней, соот-вестсвующих статическому режиму.При этои засчет открытого транзистора 18 20 напряжение в узле 24 также восстанавли— вается до начального уровня "0".

Таким образом, время считывания в предложенном устройстве определяется тремя составляющими:

СЧ 1 Ь 2 где ЬЕ, =, — to

"<

3 3 2

Подставив в формулу (1) =С, и

Vrp ь = Vrp (3)

Вторая составляющая 6t2 определяется скоростью изменения V напряжения в узле 24 (25) и величиной 35 порогового напряжения V транзисторов

At2 Ur>oP г (4)

Третья составляющая Ь t определяется средней скоростью V измене- 40

З ния напряжения выходной разрядной шины 6 (5) и уровнем Vö окончания считывания

Ьй3 = VO/V3 (5)

Таким образом, время считывания 45 устройства, как следует из выражений (2) — (5), равно гр пор о — + + (6)

% 2 3 50

Формула изобретения

Устройство для считывания информации иэ блоков памяти, содержащее первый и второй адре-ные транзисторы первого типа проводимости, первую и вторую пары переключающих транзисторов первого типа проводимости, причем истоки адресных транзисторов соединены с шиной питания, затворы являются первым и вторым адресными входами соответственно, стоки соединены с истоками переключающих транзисторов первой и второй пар соответственно, затворы которых являются соответствующими разрядными входами устройства, а стоки переключающих транзисторов первой пары объединены со стоками соответствующих транзисторов второй пары, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены первый и второй переключающие транзисторы второго типа проводимости, соединенные по схеме с перекрестной связью, первый и второй установочные транзисторы второго типа проводимости, первый и второй развяэывающие транзисторы второго типа проводимости, причем сток первого переключающего транзистора второго типа проводимости соединен с затворами вторых переключающего и развязывающего транзисторов второго типа проводимости и со стоками первого установочного транзистора и соответствующих переключающих транзисторов первого типа проводимости, сток второго переключающего транзистора второго типа проводимости соединен с затворами первых переключающего и раэвяэывающего транзисторов второго типа проводимости и со стоками второго установочного транзистора и соответствующих переключающих транзисторов первого типа проводимости, истоки переключающих транзисторов второго типа проводимости, установочных и развязывающих транзисторов соединены с общей шиной, стоки первого и второго развязывающих транзисторов являются первым и вторым разрядными выходами устройства соответственно, затворы установочных транзисторов являются тактовым входом устройства.

1280452

2 5

Фиг. 2

Составитель В.Гордонова

Техред В.Кадар Корректор О.Луговая

Редактор Н.Горват

Эаказ 7057/46 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул, Проектная,4